Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

6.5.2 Varianten von Moore- und Mealy-Automaten<br />

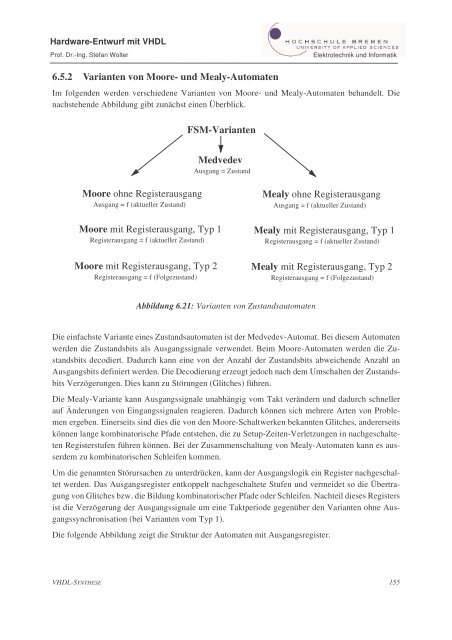

Im folgenden werden verschiedene Varianten von Moore- und Mealy-Automaten behandelt. Die<br />

nachstehende Abbildung gibt zunächst einen Überblick.<br />

Moore ohne Registerausgang<br />

Ausgang = f (aktueller Zustand)<br />

Medvedev<br />

Moore <strong>mit</strong> Registerausgang, Typ 1<br />

Registerausgang = f (aktueller Zustand)<br />

Moore <strong>mit</strong> Registerausgang, Typ 2<br />

Registerausgang = f (Folgezustand)<br />

FSM-Varianten<br />

Ausgang = Zustand<br />

Abbildung 6.21: Varianten von Zustandsautomaten<br />

Mealy ohne Registerausgang<br />

Ausgang = f (aktueller Zustand)<br />

Mealy <strong>mit</strong> Registerausgang, Typ 1<br />

Registerausgang = f (aktueller Zustand)<br />

Mealy <strong>mit</strong> Registerausgang, Typ 2<br />

Registerausgang = f (Folgezustand)<br />

Die einfachste Variante eines Zustandsautomaten ist der Medvedev-Automat. Bei diesem Automaten<br />

werden die Zustandsbits als Ausgangssignale verwendet. Beim Moore-Automaten werden die Zustandsbits<br />

decodiert. Dadurch kann eine von der Anzahl der Zustandsbits abweichende Anzahl an<br />

Ausgangsbits definiert werden. Die Decodierung erzeugt jedoch nach dem Umschalten der Zustandsbits<br />

Verzögerungen. Dies kann zu Störungen (Glitches) führen.<br />

Die Mealy-Variante kann Ausgangssignale unabhängig vom Takt verändern und dadurch schneller<br />

auf Änderungen von Eingangssignalen reagieren. Dadurch können sich mehrere Arten von Problemen<br />

ergeben. Einerseits sind dies die von den Moore-Schaltwerken bekannten Glitches, andererseits<br />

können lange kombinatorische Pfade entstehen, die zu Setup-Zeiten-Verletzungen in nachgeschalteten<br />

Registerstufen führen können. Bei der Zusammenschaltung von Mealy-Automaten kann es ausserdem<br />

zu kombinatorischen Schleifen kommen.<br />

Um die genannten Störursachen zu unterdrücken, kann der Ausgangslogik ein Register nachgeschaltet<br />

werden. Das Ausgangsregister entkoppelt nachgeschaltete Stufen und vermeidet so die Übertragung<br />

von Glitches bzw. die Bildung kombinatorischer Pfade oder Schleifen. Nachteil dieses Registers<br />

ist die Verzögerung der Ausgangssignale um eine Taktperiode gegenüber den Varianten ohne Ausgangssynchronisation<br />

(bei Varianten vom Typ 1).<br />

Die folgende Abbildung zeigt die Struktur der Automaten <strong>mit</strong> Ausgangsregister.<br />

<strong>VHDL</strong>-SYNTHESE 155