Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Hardware-Entwurf mit VHDL

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

<strong>Hardware</strong>-<strong>Entwurf</strong> <strong>mit</strong> <strong>VHDL</strong><br />

Prof. Dr.-Ing. Stefan Wolter Elektrotechnik und Informatik<br />

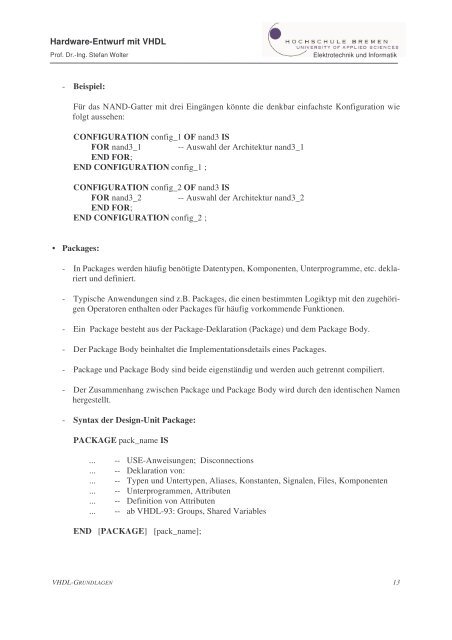

- Beispiel:<br />

Für das NAND-Gatter <strong>mit</strong> drei Eingängen könnte die denkbar einfachste Konfiguration wie<br />

folgt aussehen:<br />

CONFIGURATION config_1 OF nand3 IS<br />

FOR nand3_1 -- Auswahl der Architektur nand3_1<br />

END FOR;<br />

END CONFIGURATION config_1 ;<br />

CONFIGURATION config_2 OF nand3 IS<br />

FOR nand3_2 -- Auswahl der Architektur nand3_2<br />

END FOR;<br />

END CONFIGURATION config_2 ;<br />

• Packages:<br />

- In Packages werden häufig benötigte Datentypen, Komponenten, Unterprogramme, etc. deklariert<br />

und definiert.<br />

- Typische Anwendungen sind z.B. Packages, die einen bestimmten Logiktyp <strong>mit</strong> den zugehörigen<br />

Operatoren enthalten oder Packages für häufig vorkommende Funktionen.<br />

- Ein Package besteht aus der Package-Deklaration (Package) und dem Package Body.<br />

- Der Package Body beinhaltet die Implementationsdetails eines Packages.<br />

- Package und Package Body sind beide eigenständig und werden auch getrennt compiliert.<br />

- Der Zusammenhang zwischen Package und Package Body wird durch den identischen Namen<br />

hergestellt.<br />

- Syntax der Design-Unit Package:<br />

PACKAGE pack_name IS<br />

... -- USE-Anweisungen; Disconnections<br />

... -- Deklaration von:<br />

... -- Typen und Untertypen, Aliases, Konstanten, Signalen, Files, Komponenten<br />

... -- Unterprogrammen, Attributen<br />

... -- Definition von Attributen<br />

... -- ab <strong>VHDL</strong>-93: Groups, Shared Variables<br />

END [PACKAGE] [pack_name];<br />

<strong>VHDL</strong>-GRUNDLAGEN 13