Komponentenbasierte Mixed-Level-Modellierung mit variablen ...

Komponentenbasierte Mixed-Level-Modellierung mit variablen ...

Komponentenbasierte Mixed-Level-Modellierung mit variablen ...

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

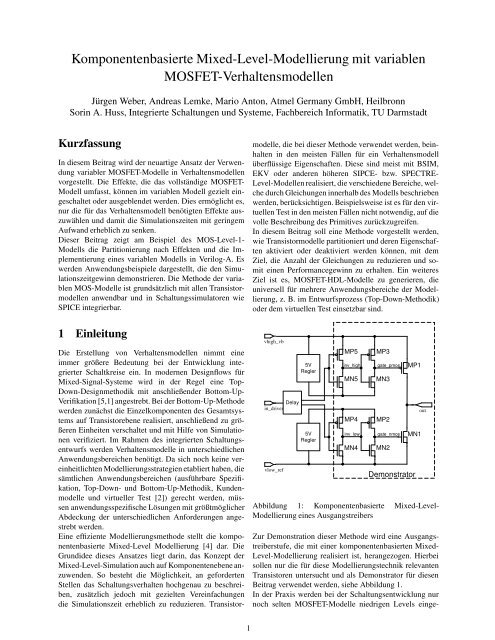

<strong>Komponentenbasierte</strong> <strong>Mixed</strong>-<strong>Level</strong>-<strong>Modellierung</strong> <strong>mit</strong> <strong>variablen</strong>MOSFET-VerhaltensmodellenJürgen Weber, Andreas Lemke, Mario Anton, Atmel Germany GmbH, HeilbronnSorin A. Huss, Integrierte Schaltungen und Systeme, Fachbereich Informatik, TU DarmstadtKurzfassungIn diesem Beitrag wird der neuartige Ansatz der Verwendungvariabler MOSFET-Modelle in Verhaltensmodellenvorgestellt. Die Effekte, die das vollständige MOSFET-Modell umfasst, können im <strong>variablen</strong> Modell gezielt eingeschaltetoder ausgeblendet werden. Dies ermöglicht es,nur die für das Verhaltensmodell benötigten Effekte auszuwählenund da<strong>mit</strong> die Simulationszeiten <strong>mit</strong> geringemAufwand erheblich zu senken.Dieser Beitrag zeigt am Beispiel des MOS-<strong>Level</strong>-1-Modells die Partitionierung nach Effekten und die Implementierungeines <strong>variablen</strong> Modells in Verilog-A. Eswerden Anwendungsbeispiele dargestellt, die den Simulationszeitgewinndemonstrieren. Die Methode der <strong>variablen</strong>MOS-Modelle ist grundsätzlich <strong>mit</strong> allen Transistormodellenanwendbar und in Schaltungssimulatoren wieSPICE integrierbar.1 EinleitungDie Erstellung von Verhaltensmodellen nimmt eineimmer größere Bedeutung bei der Entwicklung integrierterSchaltkreise ein. In modernen Designflows für<strong>Mixed</strong>-Signal-Systeme wird in der Regel eine Top-Down-Designmethodik <strong>mit</strong> anschließender Bottom-Up-Verifikation [5,1] angestrebt. Bei der Bottom-Up-Methodewerden zunächst die Einzelkomponenten des Gesamtsystemsauf Transistorebene realisiert, anschließend zu größerenEinheiten verschaltet und <strong>mit</strong> Hilfe von Simulationenverifiziert. Im Rahmen des integrierten Schaltungsentwurfswerden Verhaltensmodelle in unterschiedlichenAnwendungsbereichen benötigt. Da sich noch keine vereinheitlichten<strong>Modellierung</strong>sstrategien etabliert haben, diesämtlichen Anwendungsbereichen (ausführbare Spezifikation,Top-Down- und Bottom-Up-Methodik, Kundenmodelleund virtueller Test [2]) gerecht werden, müssenanwendungsspezifische Lösungen <strong>mit</strong> größtmöglicherAbdeckung der unterschiedlichen Anforderungen angestrebtwerden.Eine effiziente <strong>Modellierung</strong>smethode stellt die komponentenbasierte<strong>Mixed</strong>-<strong>Level</strong> <strong>Modellierung</strong> [4] dar. DieGrundidee dieses Ansatzes liegt darin, das Konzept der<strong>Mixed</strong>-<strong>Level</strong>-Simulation auch auf Komponentenebene anzuwenden.So besteht die Möglichkeit, an gefordertenStellen das Schaltungsverhalten hochgenau zu beschreiben,zusätzlich jedoch <strong>mit</strong> gezielten Vereinfachungendie Simulationszeit erheblich zu reduzieren. Transistormodelle,die bei dieser Methode verwendet werden, beinhaltenin den meisten Fällen für ein Verhaltensmodellüberflüssige Eigenschaften. Diese sind meist <strong>mit</strong> BSIM,EKV oder anderen höheren SIPCE- bzw. SPECTRE-<strong>Level</strong>-Modellen realisiert, die verschiedene Bereiche, welchedurch Gleichungen innerhalb des Modells beschriebenwerden, berücksichtigen. Beispielsweise ist es für den virtuellenTest in den meisten Fällen nicht notwendig, auf dievolle Beschreibung des Pri<strong>mit</strong>ives zurückzugreifen.In diesem Beitrag soll eine Methode vorgestellt werden,wie Transistormodelle partitioniert und deren Eigenschaftenaktiviert oder deaktiviert werden können, <strong>mit</strong> demZiel, die Anzahl der Gleichungen zu reduzieren und so<strong>mit</strong>einen Performancegewinn zu erhalten. Ein weiteresZiel ist es, MOSFET-HDL-Modelle zu generieren, dieuniversell für mehrere Anwendungsbereiche der <strong>Modellierung</strong>,z. B. im Entwurfsprozess (Top-Down-Methodik)oder dem virtuellen Test einsetzbar sind.vhigh_vbDelayin_drivervlow_ref5VRegler5VReglerMP5inv_highMN5MP4inv_lowMN4MP3gate_pmosMN3MP2gate_nmosMN2MP1MN1DemonstratorAbbildung 1: <strong>Komponentenbasierte</strong> <strong>Mixed</strong>-<strong>Level</strong>-<strong>Modellierung</strong> eines AusgangstreibersZur Demonstration dieser Methode wird eine Ausgangstreiberstufe,die <strong>mit</strong> einer komponentenbasierten <strong>Mixed</strong>-<strong>Level</strong>-<strong>Modellierung</strong> realisiert ist, herangezogen. Hierbeisollen nur die für diese <strong>Modellierung</strong>stechnik relevantenTransistoren untersucht und als Demonstrator für diesenBeitrag verwendet werden, siehe Abbildung 1.In der Praxis werden bei der Schaltungsentwicklung nurnoch selten MOSFET-Modelle niedrigen <strong>Level</strong>s einge-out1

U Usetzt. Hier haben sich in den meisten Fällen schon z. B.BSIM oder EKV etabliert. So auch bei dem in diesem Beitragvorgestellten Demonstrator, dessen originale Transistormodelleauf Basis von EKV realisiert sind. Auf eineVerdeutlichung der Methode <strong>mit</strong> EKV-Modellen sollwegen der Komplexität der Berechnungen hier verzichtetwerden, statt desssen werden <strong>Level</strong>-1-Modelle verwendet.Aus diesem Grund werden alle diese komplexen Transistormodellein <strong>Level</strong>-1-Modelle überführt, die in den meistenFällen ausreichend für die Anforderungen an das DUT-Verhaltensmodell [3] sind.Dieses MOSFET-Verhaltensmodell ist in Verilog-A realisiertund wird im Spectre Simulator von Cadence eingesetzt.Die Grundlagen eines <strong>Level</strong>-1-Modells werden inKapitel 2 kurz erläutert. In Kapitel 3 wird die Realisierungdes MOSFET-Verhaltensmodells in Verilog-A vorgestelltsowie die Demonstration der Methode in Kapitel 4.2 MOSFET-<strong>Level</strong>-1-ModellDas MOSFET-<strong>Level</strong>-1-Modell unterscheidet drei Arbeitsbereichedes Transistors, die sich durch die Spannungsdifferenzenzwischen Gate, Source und Drain definieren.Diese Arbeitsbereiche sind in Tabelle 1 aufgeführt.SperrbereichLinearer BereichSättigungsbereichU GS U thU U 0£ U GS¡U th¢ U DS¡U DS¤satDS U DS¤satDer Drainstrom lässt sich unter der Annahme, dass eineideale Ladungsverteilung im Kanal herrscht, näherungsweise<strong>mit</strong> Sah’s Modell [6] berechnen.Das schwache Ansteigen von I DS im Sättigungsbereichwird durch die Kanallängenmodulation verursacht. Sielässt sich <strong>mit</strong> dem Shichman-Hodges-Modell [6] beschreiben.Da<strong>mit</strong> lauten die Gleichungen für einen n-Kanal-MOSFET in den verschiedenen Arbeitsbereichen wiefolgt:I D¨ © 0 U GS U thK nWUL U DSU GSU DS th 21 λUDS U GS U0thU DSDSsatK nW2LU GS U th21 λU DS U GS U thU DS U DSsatIn Abbildung 3 ist das Blockschaltbild eines <strong>Level</strong>-1-Modells dargestellt. Zusätzlich zu der Drainstromquelle I Dnach Gleichung 1 enthält es Bahnwiderstände, Kapazitätenund Bulkdioden.DC GDR DC BD(1)UTabelle 1: Arbeitsbereiche im MOSFET-<strong>Level</strong>-1-ModellAbbildung 2 zeigt das Ausgangskennlinienfeld einesNMOSFET-Transistors. Ist die Gate-Source-SpannungU GS kleiner als die Schwellspannung U th , kann sich keinleitender Kanal ausbilden. Da<strong>mit</strong> befindet sich der Transistorim Sperrbereich, wo der Drainstrom I 0 unabhängigvon der Drain-Source-Spannung U DS ist. ÜberschreitetU GS die Schwellspannung U th , bildet sich ein Kanal,in dem Strom fließen kann. Der Strom I D ist für kleineU DS näherungsweise proportional zu U DS . Dieser BereichD¥wird daher als linearer Bereich bezeichnet. Wird U DS überU DS¤sat¦ U GS§ U th erhöht, wird der Kanal auf der Drainseiteabgeschnürt und I D steigt nur noch sehr schwach an.Der Transistor befindet sich im Sättigungsbereich.GR GR BI DC GSCC BSGBR SSAbbildung 3: Blockschaltbild MOSFET-<strong>Level</strong>-1-ModellBI DLinearer BereichV GS5SättigungsbereichKurzkanal-EffektV GS4V GS3V GS2V GS1Der in aktuellen Technologien auftretende Kurzkanal-Effekt führt zu einer Verschiebung der Schwellspannungbei Transistoren <strong>mit</strong> kurzen Kanallängen [7]. Dieser Effektfindet im ursprünglichen MOSFET-<strong>Level</strong>-1-Modellkeine Berücksichtigung. Für das in Abschnitt 3 vorgestellteModell wurde der Effekt durch den in [6] vorgeschlagenenFaktorV DSe f fθL e f f DS(2)Abbildung 2: Kennlinie eines NMOSFET-TransistorsθLin Gleichung 1 hinzugefügt.λ1 12

3 Variables MOSFET-HDL-ModellDieser Abschnitt beschreibt, wie auf der Basis des <strong>Level</strong>-1-Modells ein variables Verilog-A-Verhaltensmodell erstelltwird.Ziel bei der Entwicklung des <strong>variablen</strong> Modells ist es,die benötigten Modelleffekte auswählen und die übrigenaus dem Modell ausblenden zu können. Da<strong>mit</strong> wirdbei der Simulation eine minimale Jacobi-Matrix erreichtund der Rechenaufwand reduziert. Hierfür werden ausgehendvom <strong>Level</strong>-1-Modell die Berechnung des Drainstroms,des Substrateffekts sowie die Einbeziehung der inAbbildung 3 dargestellten Kapazitäten, Widerstände undDioden variabel gemacht. Tabelle 2 führt die unterschiedlichenVarianten bei der Berechnung des Drainstroms auf.Ferner können die in Tabelle 3 dargestellten Bestandteiledes MOSFET-Verhaltensmodells ausgewählt werden.Variante Beschreibung0 Spannungsgesteuerter Widerstand1 Ohne Kanallängenmodulation2 Mit Kanallängenmodulation3 Mit KurzkanaleffektTabelle 2: Berechnung des Drainstroms im Verilog-A-ModellBestandteilres_nodalcap_gatecap_subdio_subthresholdBeschreibungBahnwiderständeGate-KapazitätenSperrschichtkapazitätenSubstratdiodenSubstrateffektTabelle 3: Wählbare Bestandteile des MOSFET-Verilog-A-ModellsNachfolgend werden drei Methoden der Realisierung des<strong>variablen</strong> <strong>Level</strong>-1-Modells vorgestellt: ein statisches <strong>mit</strong>Präprozessoranweisungen, bei dem Teile des Quelltextesvor seiner Übersetzung ausgeblendet werden, ein statisches<strong>mit</strong> Parameterübergabe und ein dynamisches, dasVeränderungen der Modelleigenschaften während der Simulationermöglicht.3.1 Statisches MOSFET-Modell <strong>mit</strong>PräprozessoranweisungenDurch Verwendung von Präprozessoranweisungen wieifdef können aus dem Quelltext des Modells beliebige Bereicheausgewählt werden. Vorteilhaft an dieser Realisierungist, dass wirklich nur diese Bereiche ins kompilierteModell übernommen werden. Nachteil ist, dass die Auswahlvor dem Kompilieren getroffen werden muss unddiese Einstellung global für alle Instanzen des Transistorsübernommen wird. Im folgenden Quelltext wird dieserAnsatz schematisch dargestellt:‘ifdef res_nodal- Funktion Bahnwiderstände‘else- keine Funktion Bahnwiderstände‘endifEin weiterer Vorteil des Ansatzes ist die Möglichkeit derVeränderung der Schaltungstopologie durch Hinzufügenoder Weglassen interner Knoten. Am Beispiel der Bahnwiderständewird dies deutlich: Sie können nur unter Verwendunginterner Knoten ins Modell aufgenommen werden.Nur <strong>mit</strong> Hilfe von Präprozessoranweisungen kann ihreDeklaration (electrical Bi, Di, Si, Gi;) wahlweise verwendetwerden. Im weiteren Quelltext wird dann zwischeninternen Knoten (Si, Di etc.) und den Pins (D, Setc.) gewechselt:‘ifdef res_nodalvds = V(Di, Si);...‘elsevds = V(D, S);...‘endifArbeitsbereichserkennungBei der Erkennung, in welchem Arbeitsbereich sich derTransistor befindet, wird die Variable region verwendet:if ((vgs

‘elsevtho = vt0;‘endif3.2 Statisches MOSFET-Modell <strong>mit</strong> ParameterübergabeBeim statischen MOSFET-Modell <strong>mit</strong> Parameterübergabewird anstelle von Präprozessoranweisungen das ifelse-Konstruktverwendet. Das Aus- und Einschalten dereinzelnen Funktionen wird durch Parameterübergabe gesteuertund kann für jede Transistorinstanz individuelldurchgeführt werden. Dies ist ein Vorteil gegenüber derVerwendung von Präprozessoranweisungen. Als Nachteilzeigt sich ein etwas höherer Rechenaufwand bei der Simulation.parameter integer res_nodal = 0;.....if (res_nodal == 1)- Funktion Bahnwiderständeelse- keine Funktion Bahnwiderständeend3.3 Dynamische MOSFET-ModelleEinige Anwendungen, z. B. der virtuelle Test, erfordern,dass eine ganze Testgruppe aus mehreren Tests zusammensimuliert wird. So<strong>mit</strong> ergibt sich die Forderung nach dynamischwährend der Simulation umschaltbaren MOSFET-Modellen. Ermöglicht wird dies durch Verwendung vonVariablen anstelle der in Abschnitt 3.2 beschriebenen Parameter.integer res_nodal;...if (res_nodal == 1)- Funktion Bahnwiderständeelse- keine Funktion BahnwiderständeendDas Umschalten dieser Variablen kann in einer Testbenchinstanzspezifisch erfolgen. Im nachfolgenden Quelltext istein Beispiel einer Testbench dargestellt, in der die Bahnwiderständeeiner Instanz nach 10000 Zeiteinheiten hinzugeschaltetwerden.initial beginI_top.I_inv.I_NMOS1.res_nodal = 0;# 10000I_top.I_inv.I_NMOS1.res_nodal = 1;......endZur Zeit lassen der AMS-Designer und Spectre analogeAnweisungen [8] in Verilog-A innerhalb von if -Konstrukten <strong>mit</strong> Variablen nicht zu. Daher müssen dieseAnweisungen, z. B. Berechnung der Kapazitäten <strong>mit</strong>ddt oder limexp für die Diodenberechnung, außerhalb derif -Konstrukte liegen. Dadurch wird der mögliche Rechenzeitgewinnbei der Simulation <strong>mit</strong> <strong>variablen</strong> dynamischenModellen nicht erreicht. Im folgenden Abschnitt werdendeshalb statische Modelle <strong>mit</strong> Parameterübergabe verwendet.4 AnwendungsbeispieleIn diesem Abschnitt wird der Einsatz variabler MOSFET-Verhaltensmodelle am Beispiel einer Ausgangstreiberstufedemonstriert, die komponentenbasiert mixed-levelmodelliertist. Ferner wird auf die Ergebnisse der Einzeltransistorensowie der Treiberstufe eingegangen und abschließendeine Auswertung dargestellt.Bei dem hier verwendeten Beispiel handelt es sichum die Endstufe eines Ausgangstreibers, die in Abbildung4 dargestellt ist. Untersucht werden nur dieTransistoren, die bei einer komponentenbasierten <strong>Mixed</strong>-<strong>Level</strong>-<strong>Modellierung</strong> dieser Treiberstufe benötigt werden(MP1, MP2, MP3, MP4, MP5, MN1, MN2, MN3, MN4,MN5). Die verbleibenden Komponenten, die zusätzlichzur <strong>Mixed</strong>-<strong>Level</strong>-<strong>Modellierung</strong> der Stufe verwendet wurden,werden in diesem Beitrag nicht betrachtet. Die EKV-Transistormodellparameter der zu diesem Beispiel gehörendenTechnologie wurden in Parameter für das <strong>Level</strong>-1-Modell überführt.vhigh_vbin_highvhigh_refvlow_vbin_lowvlow_refMP5inv_highMN5MP4MN4inv_lowMP3MN3MP2MN2gate_pmosgate_nmosMP1MN1Abbildung 4: Endstufe eines Ausgangstreibers4.1 DC-Verhalten <strong>mit</strong> variablem MOSFET-ModellAbbildung 5 zeigt die simulierte Ausgangskennlinie desNMOS <strong>mit</strong> verschiedenen Einstellungen des <strong>variablen</strong>MOSFET-Verhaltensmodells. Die Kapazitäten (Gate- undSperrschichtkapazitäten) haben keinen Einfluss auf dasDC-Verhalten. Gleiches gilt für den Substrateffekt, daBulk und Source verbunden sind.4.2 Anwendung des <strong>variablen</strong> MOSFET-ModellsFolgende Aspekte müssen bei der Konfiguration des <strong>variablen</strong>MOSFET-Verhaltensmodells berücksichtigt werden:• Applikation der Schaltung (Testbench)• Arbeitspunkt der Schaltung bzw. des Transistorsout5

1 @ ) # % # 5 , + A E E A 0 , @ A 1 L = H ! , 1 L = H , 1 L = H , 1 L = H , 1 H A I @ = , 1 = , 5 @ A L = H 5 @ A L = H 5 @ A L = H ! 5 @ A E J 4 I K @ 4 @ K @ L = H 5 @ A L = H F A J J A I 5 @ A E J L = H Variante Mx1 Mx2, Mx3 Mx4, Mx5var 1 2 2res_nodal ja nein neincap_gate ja nein neincap_sub ja nein neindio_sub ja nein neinthreshold nein nein neinTabelle 4: Konfigurationen zur Bestimmung von R DS¤on # # ! " L L @@ H H = = EE Abbildung 5: MOSFET-Kennlinie für verschiedene Einstellungendes <strong>variablen</strong> MOSFET-Verhaltensmodells• Simulationsart (DC, transient etc.)• Geforderte Genauigkeit der Simulation• Zweck der Simulation (virtueller Test, Entwicklungsphase,Systemsimulation etc.)Zur Auswahl der richtigen Einstellungen ist schaltungstechnischesWissen erforderlich.Die Einstellungen erfolgen direkt am Transistorsymbol imSchaltplaneditor, siehe Abbildung 6.Das Simulationsergebnis in Abbildung 7 zeigt die Ausgangsspannungfür drei verschiedene Einstellungen derMOSFET-HDL-Modelle: <strong>mit</strong> allen Eigenschaften (kompletteMOSFET-Modelle), <strong>mit</strong> Abwahl aller Eigenschaftenund var¦ 0 (spannungsgesteuerter Widerstand) sowie<strong>mit</strong> den in Tabelle 4 dargestellten Einstellungen. Durch dieVereinfachung bei den ansteuernden Transistoren weichendie Verzögerungen sehr stark gegenüber dem vollständigenModell ab. Die Endwerte, bei denen die Er<strong>mit</strong>tlungdes Wertes R DS¤on stattfindet, sind bei den Einstellungennach Tabelle 4 identisch <strong>mit</strong> denen des vollständigen Modells.8 8 % ## #- H E J J K C @ A I 4 @ I 5 % ' % K I & & # 8 & " K I & & 8 ) K I C = C I I F = K C A L = H E = > A 5 @ A AMN2var = 2cap_sub = 1cap_gate = 1dio_sub = 1res_nodal = 1threshold = 11 ) # " ! F A J J A 5 @ A A A E B = ? D I J A 5 @ A A ! " K I " ) ) K I C = C I I J H Abbildung 6: Konfiguration des Verhaltensmodells amSymbolDie folgenden Beispiele zeigen das Vorgehen bei verschiedenenSimulationsaufgaben.Er<strong>mit</strong>tlung von R DS¤onBei den meisten Treiberstufen wird beim Produktionsmessender Parameter R DS¤on überwacht. Dieses Verhaltensoll im virtuellen Test durch das Verhaltensmodell wiedergebenwerden. Bei der Er<strong>mit</strong>tlung von R DS¤on wird amAusgang ein Strom von 40 mA als Last angelegt. Danachwird der Spannungsabfall vom Ausgang zur Betriebsspannung(10 V) gemessen und der Widerstandswert berechnet.Für diese Anforderung wurde die in Tabelle 4 aufgeführteKonfiguration der Transistoren der Treiberstufeeingestellt.Die beiden Ausgangstransistoren MN1 und MP1 beinhaltenalle Eigenschaften außer dem Substrateffekt, da Bulkund Source kurzgeschlossen sind. Bei den ansteuerndenTransistoren sind alle Eigenschaften deaktiviert worden. # J E A K I # # ! Abbildung 7: Er<strong>mit</strong>tlung des R DS¤on(NMOS) der TreiberstufeDie Simulation der Treiberstufe <strong>mit</strong> den nach Tabelle 4eingestellten Parametern ist 6,7-mal schneller als bei derVerwendung der MOSFET-Modelle <strong>mit</strong> allen Eigenschaften.Dass Transistormodelle, die als Pri<strong>mit</strong>ive im Simulatorimplementiert sind, optimale Performance bieten, ist hinlänglichbekannt. In diesem Beispiel ist bei der Verwendungder ursprünglichen EKV-Modelle eine zweimalschnellere Simulation gegenüber vollständigen Verhaltensmodellenerreicht worden. Werden die Zeiten derEKV-Modelle <strong>mit</strong> den optimal eingestellten MOSFET-Verhaltensmodellen verglichen, wird immer noch einebis zu dreimal schnellere Simulation erreicht. BeiVerwendung der einfachsten Einstellung der MOSFET-Verhaltensmodelle sogar bis zu 22-mal, bei einem Fehlervon 8,6 %. Tabelle 5 fasst diese Ergebnisse zusammen.6

Eigenschaften Performance Abweichungvollständig 1 x keinewie in Tab. 4 6,7 x keinekeine 44 x 8,6 %Tabelle 5: Simulationsperformance und Modellgenauigkeitbei der Bestimmung von R DS¤onEr<strong>mit</strong>tlung der Bulk-Dioden-SpannungBeim Kontakttest wird ein Strom an dem zu messendenPin eingespeist und eine Spannung, die der Bulk-Dioden-Spannung entspricht, erwartet. In der Testbench ist hierfüreine Stromquelle am Ausgang angeschlossen, die einmaleinen positiven und einmal einen negativen Strom einprägt.Alle anderen Eingänge liegen auf Masse. Die in Tabelle6 aufgeführten Funktionen sind bei den einzelnenTransistoren der Treiberstufe für diese Simulationsaufgabeeingestellt worden. Bei dieser Konfiguration werdennur die Bulk-Dioden und die Bahnwiderstände der Ausgangstransistorenverwendet.Variante Mx1 Mx2, Mx3 Mx4, Mx5var 1 2 2res_nodal ja nein neincap_gate nein nein neincap_sub nein nein neindio_sub ja nein neinthreshold nein nein neinTabelle 6: Verwendete Funktionen für die MOSFET-Modelle zur Bestimmung der Bulk-Dioden-SpannungIn Abbildung 8 ist das Simulationsergebnis der Bulk-Dioden-Spannungen dargestellt. Zu erkennen sind diezwei Ausgangsspannungen und der Ausgangsstrom von1 mA. Tabelle 7 führt Simulationszeit und -genauigkeitauf. #8 8 1 ) # # # # - H E J J K C @ A H * K , E @ A . K I I I F = K C A ! # # K I ) " % K I & ! " 8 ) K I C = C I I F = K C A L = H E = > A 5 @ A A F A J J A 5 @ A A ! $ ! K I & ! ! ' 8 ! $ % K I ) ) K I C = C I I J A ! J E A K I " # $ Abbildung 8: Er<strong>mit</strong>tlung der Bulk-Dioden-FlussspannungEr<strong>mit</strong>tlung der Slew-RateBei der Er<strong>mit</strong>tlung der Slew-Rate wird der Ausgang <strong>mit</strong>einer ohmschen Last belastet. Die Er<strong>mit</strong>tlung der An-Performancegewinn Modellabweichung2,3 x keineTabelle 7: Simulationszeit und Modellgenauigkeit bei derBestimmung der Bulk-Dioden Spannungstiegszeit wird bei 2 V Ausgangsspannung (20 % des Endwertes)und 8 V (80 % des Endwertes) gemessen.Die einzelnen MOSFET-Modelle sind wie bei der Er<strong>mit</strong>tlungdes R DS¤on eingestellt, siehe Tabelle 4.In Abbildung 9 ist das Simulationsergebnis dargestellt.Hier ist die Simulationsgeschwindigkeit 34-mal höher beieinem Fehler von 47 % bei der Anstiegszeit und 15,1 % beider Abfallzeit, siehe Tabelle 8. Falls dieser Fehler nicht akzeptabelist, müssen ausgeblendete Eigenschaften der ansteuerndenTransistoren wieder eingeschaltet werden. Daswürde den Performancegewinn reduzieren.8 8 8 8 % ## #$ # " ! E M % ' I & 8 $ $ $ $ $ $ $ $ IIII %%%% '''' '''' """" 8888 $ $ I % ' ' " 8 #### #### !!!! IIII 8888 # # ! I 8 !!!! ! $ $ $ $ #### $ # """" IIII " I 8888 8 FFFF AAAA JJJJJJJJAAAA 5555 @@@@ AAAA AAAA- E C = C I I F = K C- H E J J K C @ A H ) I J E A C I A E J F A J J A 5 @ A A)))) KKKK IIII C C C C = = = = CCCC IIII IIII F F F F = = = = KKKK CCCC AAAA L L L L = = = = HH H HE E E = E = = = > > > > AA A A 55 5 5 @@ @ @ AA A A AAA AL = H E = > A 5 @ A A) K I C = C I I F = K C A ---- EEEE C C C C = = = = CCCC IIII IIII F F F F = = = = KKKK CCCC J E A K I ! " # Abbildung 9: Er<strong>mit</strong>tlung der AnstiegszeitPerformance Abweichung (rise) Abweichung (fall)34 x 47 % 15,1 %Tabelle 8: Simulationszeit und Modellgenauigkeit bei derEr<strong>mit</strong>tlung der Anstiegs- und AbfallzeitEr<strong>mit</strong>tlung der Spannung im ein- und ausgeschaltetenZustandAls Last wird bei der Er<strong>mit</strong>tlung der Spannungen im einundausgeschalteten Zustand ein Widerstand verwendet.Gemessen werden diese Spannungen immer im eingeschwungenenZustand, d. h. weit weg von den AnstiegsundAbfallflanken. Bei korrekter Funktion des Treibers arbeitetder Ausgangstransistor dann im linearen Bereich.Mit diesen Randbedingungen können für alle Transistorendie Verhaltensmodelle <strong>mit</strong> var¦ 0 und ohne zusätzlicheModelleffekte verwendet werden.Abbildung 10 zeigt das Simulationsergebnis. Es sinddie Ausgangsspannungsverläufe <strong>mit</strong> den Spannungswertenim ein- bzw. ausgeschalteten Zustand dargestellt. Anden Simulationszeiten in Tabelle 9 wird der Vorteil des7

<strong>variablen</strong> MOSFET-HDL-Modells in diesem Beispiel besondersdeutlich. Die Simulation ist 217,5-mal schnellerbei nur 0,15 % Fehler.8 8 8 8 % ## #$ E M# " ! - H E J J K C @ A H ) K I C = C I I F = K C A ) K I C = C I I F = K C # ! # % I ' ' ' " 8 L = H E = > A 5 @ A A- E C = C I I F = K C ! " K I 8 F A J J A 5 @ A A ! ' K I ' ' $ = 8 ! " ! K I # 8 J E A K I ! " # Abbildung 10: Er<strong>mit</strong>tlung der Spannung im ein- und ausgeschaltetenZustandPerformancegewinn Modellabweichung217,5 x 0,15 %Tabelle 9: Simulationszeit und Modellgenauigkeit bei derSpannung im ein- und ausgeschalteten Zustand5 Zusammenfassung und AusblickIn diesem Beitrag wurde eine Methode vorgestellt, wieMOSFET-Modelle partitioniert und deren Eigenschaftenaktiviert oder deaktiviert werden können, <strong>mit</strong> dem Ziel,einen Performancegewinn zu erhalten. Diese Methodewurde anhand von MOSFET-Verhaltensmodellen, die aufBasis von <strong>Level</strong>-1-MOSFET Berechnungen realisiert wurden,demonstriert. Die Modelle bieten zusätzlich nochauswählbare Erweiterungen wie den Kurzkanaleffekt oderVereinfachungen, die es erlauben, den Transistor als spannungsgesteuertenWiderstand einzusetzen. Die einzelnenModelleffekte, die variabel ein- und ausschaltbar sind,wurden einzeln durch den Source-Code beschrieben. DasModell wurde in Verilog-A erstellt und <strong>mit</strong> Spectre vonCadence simuliert.Es wurden für das Auswählen der MOSFET-Modelleigenschaften drei Möglichkeiten, die ihreVor- und Nachteile haben, aufgezeigt. Abschließendwurden die <strong>variablen</strong> MOSFET-HDL-Modelle an einemDemonstrator angewandt. Hierbei wurden der Performancegewinnund der Modellfehler an vier verschiedenenSimulationsaufgaben er<strong>mit</strong>telt. Es ergab sich eine Geschwindigkeitszunahmevon bis zu 217 mal <strong>mit</strong> einemFehler von nur 0,15%. Ein Nachteil zeigte sich beimehrmals vorkommenden Konvergenzproblemen, dieaber immer wieder durch neue Simulatoreinstellungenbehoben werden konnten.Die Tatsache, dass die Verwendung der originalen EKV-Transistoren schneller als die komplexeste Ausbaustufeder MOSFET-HDL Modelle ist, ist hinreichend bekannt.Um dem entgegenzuwirken, hat Cadence beiden neueren Simulatorversionen einen C-Compiler fürVerilog-A implementiert. Trotzdem lässt sich feststellen,dass auch ein Performancegewinn der optimal eingestelltenMOSFET-HDL-Modelle gegenüber den originalenEKV-Transistoren vorliegt.Um eine Verbesserung der Performance zu bekommen,wäre es wünschenswert, die hier beschriebene Methodein den Simulator zu integrieren.In diesem Beitrag wurde ein MOS-HDL-Modell aufBasis des <strong>Level</strong>-1-Modell realisiert, was aber nur alsDemonstration der Methode dienen sollte. Sinnvoll wäre,bei allen MOSFET-Modelltypen eine solche Methode anzuwenden.Das optimale Einstellen der verschiedenen Eigenschaftendes Modells erfordert schaltungstechnisches Wissen, wasbei der <strong>Modellierung</strong> Voraussetzung sein sollte.Literatur[1] M. Anton, J. Weber: Simulationsmethodik fuerintegrierte <strong>Mixed</strong>-Signal Automotive Schaltkreise,Analog 2003, Heilbronn, 10-12 September, Seite103-108[2] J. Weber, M. Anton, S. A. Huss: Verhaltensmodellierungvon Ein- und Ausgangsstufen für den VirtuellenTest von <strong>Mixed</strong>-Signal Automotive Schaltkreisen,Analog 2003, Heilbronn, 10-12 September,Seite 91-96[3] M. Anton, J. Weber, J. Schuster, A. Lehmann: Verhaltensmodellierungvon <strong>Mixed</strong>-Signal AutomotiveICs für die Anwendung im Virtuellen Test, Analog2002, Bremen, 13-14 Mai, Seite 55-60[4] J. Weber, M. Anton, S. A. Huss: Effiziente <strong>Mixed</strong>-<strong>Level</strong> <strong>Modellierung</strong> integrierter <strong>Mixed</strong>-Signal AutomotiveSchaltkreise, Analog 2005, Hannover, 16-18 März,Seite 217-222[5] Sommer, R.; Rugen-Herzig, I.; et al.: From systemspecification to layout: Seamless topdown designmethods for analog and mixed-signal applications.DATE 02, Paris, March 4-8, 2002, ISBN 0-7695-1471-5[6] "The VLSI Handbook", Wai-Kai Chen, CRC PressLLC, Dezember 1999[7] "Halbleiter Schaltungstechnik", U. Tietze und C.Schenk, Springer Verlag, 1999, 11. Auflage[8] Accellera Verilog Analog <strong>Mixed</strong>-Signal Group:Verilog-AMS Language Reference Manual, Version2.2, November 20048