Jahresbericht 2008 - Fakultät für Elektrotechnik, Informatik und ...

Jahresbericht 2008 - Fakultät für Elektrotechnik, Informatik und ...

Jahresbericht 2008 - Fakultät für Elektrotechnik, Informatik und ...

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

Datentechnik<br />

Prof. Dr. rer. nat. Sybille Hellebrand<br />

„Test <strong>und</strong> Diagnose von Systems-on-a-Chip“<br />

„Systems-on-a-Chip“ implementieren<br />

komplexe mikroelektronische Systeme<br />

auf einem Chip <strong>und</strong> finden sich mittlerweile<br />

in allen Bereichen des täglichen<br />

Lebens, insbesondere auch in sicherheitskritischen<br />

Anwendungen. Zur<br />

Qualitätssicherung werden effiziente<br />

Test- <strong>und</strong> Diagnoseverfahren benötigt,<br />

die defekte Bausteine möglichst schnell<br />

<strong>und</strong> mit möglichst geringen Kosten<br />

identifizieren können. Konventionelle<br />

Verfahren mit externen Testgeräten<br />

reichen nicht mehr aus, da viele<br />

Systemkomponenten von außen nur<br />

schwer zugänglich sind <strong>und</strong> große<br />

Mengen von Testdaten über Kanäle<br />

mit geringer Bandbreite transportiert<br />

werden müssten.<br />

Institut <strong>für</strong> <strong>Elektrotechnik</strong> <strong>und</strong> Informationstechnik<br />

Informationstechnik<br />

28<br />

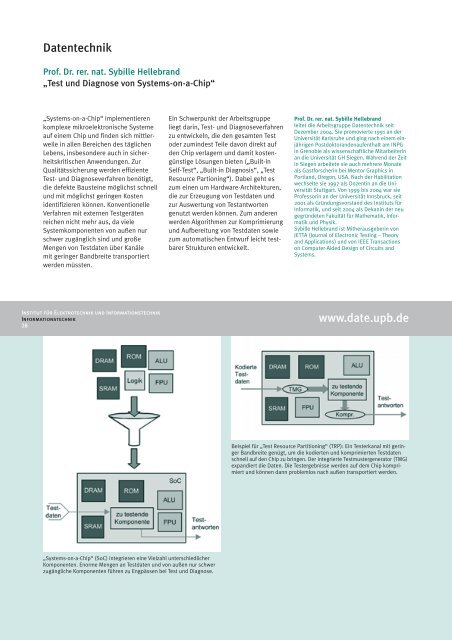

„Systems-on-a-Chip“ (SoC) integrieren eine Vielzahl unterschiedlicher<br />

Komponenten. Enorme Mengen an Testdaten <strong>und</strong> von außen nur schwer<br />

zugängliche Komponenten führen zu Engpässen bei Test <strong>und</strong> Diagnose.<br />

Ein Schwerpunkt der Arbeitsgruppe<br />

liegt darin, Test- <strong>und</strong> Diagnoseverfahren<br />

zu entwickeln, die den gesamten Test<br />

oder zumindest Teile davon direkt auf<br />

den Chip verlagern <strong>und</strong> damit kostengünstige<br />

Lösungen bieten („Built-in<br />

Self-Test“, „Built-in Diagnosis“, „Test<br />

Resource Partioning“). Dabei geht es<br />

zum einen um Hardware-Architekturen,<br />

die zur Erzeugung von Testdaten <strong>und</strong><br />

zur Auswertung von Testantworten<br />

genutzt werden können. Zum anderen<br />

werden Algorithmen zur Komprimierung<br />

<strong>und</strong> Aufbereitung von Testdaten sowie<br />

zum automatischen Entwurf leicht testbarer<br />

Strukturen entwickelt.<br />

Prof. Dr. rer. nat. Sybille Hellebrand<br />

leitet die Arbeitsgruppe Datentechnik seit<br />

Dezember 2004. Sie promovierte 1991 an der<br />

Universität Karlsruhe <strong>und</strong> ging nach einem einjährigen<br />

Postdoktorandenaufenthalt am INPG<br />

in Grenoble als wissenschaftliche Mitarbeiterin<br />

an die Universität GH Siegen. Während der Zeit<br />

in Siegen arbeitete sie auch mehrere Monate<br />

als Gastforscherin bei Mentor Graphics in<br />

Port land, Oregon, USA. Nach der Habilitation<br />

wechselte sie 1997 als Dozentin an die Univer<br />

sität Stuttgart. Von 1999 bis 2004 war sie<br />

Professorin an der Universität Innsbruck, seit<br />

2001 als Gründungsvorstand des Instituts <strong>für</strong><br />

<strong>Informatik</strong>, <strong>und</strong> seit 2004 als Dekanin der neu<br />

gegründeten <strong>Fakultät</strong> <strong>für</strong> Mathematik, Infor -<br />

matik <strong>und</strong> Physik.<br />

Sybille Hellebrand ist Mitherausgeberin von<br />

JETTA (Journal of Electronic Testing – Theory<br />

and Applications) <strong>und</strong> von IEEE Transactions<br />

on Computer-Aided Design of Circuits and<br />

Systems.<br />

www.date.upb.de<br />

Beispiel <strong>für</strong> „Test Resource Partitioning“ (TRP): Ein Testerkanal mit geringer<br />

Bandbreite genügt, um die kodierten <strong>und</strong> komprimierten Testdaten<br />

schnell auf den Chip zu bringen. Der integrierte Testmustergenerator (TMG)<br />

expandiert die Daten. Die Testergebnisse werden auf dem Chip komprimiert<br />

<strong>und</strong> können dann problemlos nach außen transportiert werden.