CSCE 212: Example quiz answers 1. Assemble the following ...

CSCE 212: Example quiz answers 1. Assemble the following ...

CSCE 212: Example quiz answers 1. Assemble the following ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

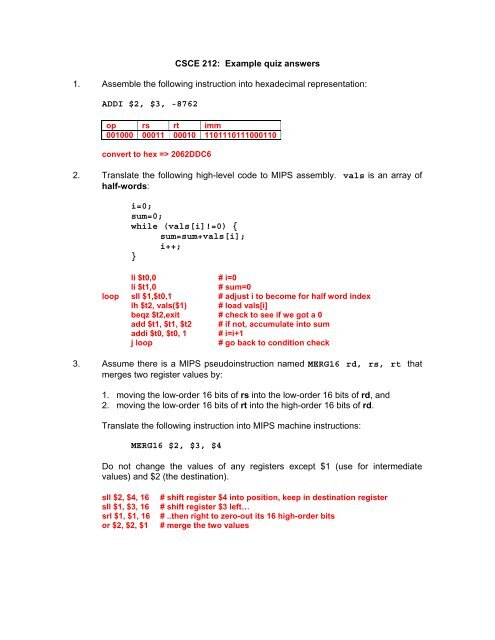

<strong>CSCE</strong> <strong>212</strong>: <strong>Example</strong> <strong>quiz</strong> <strong>answers</strong><br />

<strong>1.</strong> <strong>Assemble</strong> <strong>the</strong> <strong>following</strong> instruction into hexadecimal representation:<br />

ADDI $2, $3, -8762<br />

op rs rt imm<br />

001000 00011 00010 1101110111000110<br />

convert to hex => 2062DDC6<br />

2. Translate <strong>the</strong> <strong>following</strong> high-level code to MIPS assembly. vals is an array of<br />

half-words:<br />

i=0;<br />

sum=0;<br />

while (vals[i]!=0) {<br />

sum=sum+vals[i];<br />

i++;<br />

}<br />

li $t0,0 # i=0<br />

li $t1,0 # sum=0<br />

loop sll $1,$t0,1 # adjust i to become for half word index<br />

lh $t2, vals($1) # load vals[i]<br />

beqz $t2,exit # check to see if we got a 0<br />

add $t1, $t1, $t2 # if not, accumulate into sum<br />

addi $t0, $t0, 1 # i=i+1<br />

j loop # go back to condition check<br />

3. Assume <strong>the</strong>re is a MIPS pseudoinstruction named MERG16 rd, rs, rt that<br />

merges two register values by:<br />

<strong>1.</strong> moving <strong>the</strong> low-order 16 bits of rs into <strong>the</strong> low-order 16 bits of rd, and<br />

2. moving <strong>the</strong> low-order 16 bits of rt into <strong>the</strong> high-order 16 bits of rd.<br />

Translate <strong>the</strong> <strong>following</strong> instruction into MIPS machine instructions:<br />

MERG16 $2, $3, $4<br />

Do not change <strong>the</strong> values of any registers except $1 (use for intermediate<br />

values) and $2 (<strong>the</strong> destination).<br />

sll $2, $4, 16 # shift register $4 into position, keep in destination register<br />

sll $1, $3, 16 # shift register $3 left…<br />

srl $1, $1, 16 # ..<strong>the</strong>n right to zero-out its 16 high-order bits<br />

or $2, $2, $1 # merge <strong>the</strong> two values

4. Complete <strong>the</strong> <strong>following</strong> table by filling in <strong>the</strong> empty cells to connect MIPS<br />

instruction types with <strong>the</strong>ir corresponding encoding format.<br />

Instruction type Encoding format<br />

Load and store instructions I-type<br />

Branch instructions I-type<br />

Arithmetic instructions having 2<br />

R-type<br />

register input operands<br />

Shift instructions R-type<br />

Jump (J, JAL) instructions J-type<br />

5. Describe three different functions of <strong>the</strong> immediate field in <strong>the</strong> MIPS instruction<br />

set.<br />

constant operand for arithmetic, PC-relative branch offset for branches,<br />

offset for base-offset addressing for loads and stores<br />

6. When executing <strong>the</strong> ADDI instruction, <strong>the</strong> MIPS architecture sign-extends its 16bit<br />

immediate field before adding it to <strong>the</strong> contents of register rs. Assume for this<br />

question that <strong>the</strong> hardware designers saved costs by always zero-extending <strong>the</strong><br />

immediate value instead. As a result, any ADDI instruction with a negative<br />

immediate value is treated as a pseudoinstruction by <strong>the</strong> assembler. When <strong>the</strong><br />

pseudoinstruction is assembled, it is converted into a series of instructions that<br />

perform a software-based sign extension of <strong>the</strong> immediate. Assuming <strong>the</strong>re have<br />

been no o<strong>the</strong>r architectural changes, how is <strong>the</strong> <strong>following</strong> pseudoinstruction<br />

translated:<br />

ADDI $s0, $s1, -12<br />

Hint: <strong>the</strong> first instruction in <strong>the</strong> translation moves <strong>the</strong> 16-bit immediate into<br />

temporary register $1, which (in this case) results in register $1 having value<br />

0000 FFF4. Three more instructions are needed:<br />

<strong>1.</strong> ADDI $1, $0, -12<br />

2. sll $1, $1, 16<br />

3. sra $1, $1, 16<br />

4. add $s0, $s1, $1

7. Describe what computation <strong>the</strong> <strong>following</strong> segment of assembly code is<br />

performing. List what registers need to be initialized before <strong>the</strong> code begins and<br />

how <strong>the</strong>se registers are used.<br />

li $s0, 0<br />

lw $s2, 0($a1)<br />

loop: lw $s1, 0($a0)<br />

mult $s3, $s1, $s2<br />

add $s0, $s0, $s3<br />

addi $a0, $a0, 4<br />

addi $a2, $a2, -1<br />

bnez $a2, loop<br />

multiplies each element of a word array, starting at address specified in $a0, by a<br />

word value stored in memory at address in $a1, and accumulates a running sum of<br />

<strong>the</strong> products into $s0. <strong>the</strong> array size is specified in $a2.<br />

8. Translate <strong>the</strong> <strong>following</strong> high-level code to MIPS assembly:<br />

for (i=0;i

9. Many CISC instruction set architectures, such as Intel IA-32 (x86) and IBM 360,<br />

include a set of instructions that do computation using a datatype called binarycoded<br />

decimal (BCD). BCD stores integer values by assigning binary-encoded<br />

decimal values (0-9) into 4-bit fields. Eight of <strong>the</strong>se 4-bit fields can be packed<br />

into a 32-bit word, representing a value between 0 and 99,999,999. For<br />

example, <strong>the</strong> (16-bit) value 0011 1001 0001 0101 represents 3,915 (instead of<br />

14,613 as it would as a regular base-2 integer).<br />

Assume we have a pseudoinstruction called CBCD rd, rs that converts <strong>the</strong><br />

binary value in register rs to an 8-digit packed BCD value written to register rd.<br />

Show (for full credit) or describe (for partial credit) how CBCD $2, $3 could be<br />

translated into MIPS instructions. Hint: how would you perform this base<br />

conversion yourself?<br />

Note that <strong>the</strong> <strong>following</strong> answer changes <strong>the</strong> value of $4 (used by this code as a<br />

counter) and register $3 (<strong>the</strong> original rs register). This is not typical for<br />

pseudoinstructions, but given <strong>the</strong> complexity we will allow it.<br />

li $2, 0 # $2 = 0<br />

li $4, 4 # $4 = 0<br />

loop: li $1,10 # $1=10<br />

mult $2,$2,$1 # multiply $2 by 10<br />

sll $3,$3,4 # shift $3 4 bits to <strong>the</strong> left<br />

srl $1,$3,28 # copy <strong>the</strong> left-most 4 bits of $3 into $1<br />

add $2,$2,$1 # add $1 into $2<br />

addi $4,$4,-1 # decrement counter<br />

bgtz $4, loop<br />

10. Write a sequence of MIPS assembly instructions that will swap <strong>the</strong> values of<br />

registers $s0 and $s1 without using any additional registers or any loads<br />

and stores.<br />

Hint: this requires that you use <strong>the</strong> XOR instruction.<br />

xor $s0,$s0,$s1<br />

xor $s1,$s0,$s1<br />

xor $s0,$s0,$s1