- Page 1: On-chip Networks for Manycore Archi

- Page 6 and 7: express how deeply grateful I am to

- Page 8 and 9: 2.4 Experimental Results . . . . .

- Page 11 and 12: List of Figures 2-1 Randomized mini

- Page 13: List of Tables 1.1 Recent multicore

- Page 16 and 17: was mostly due to leakage current b

- Page 18 and 19: either of these two scenarios be th

- Page 20 and 21: work to support specific mechanisms

- Page 23 and 24: Chapter 2 Oblivious Routing with Pa

- Page 25 and 26: minimum number of hops, a feature k

- Page 27 and 28: 2.2 Path-based, Randomized, Oblivio

- Page 29 and 30: Uniform PROM Uniform PROM weighs th

- Page 31 and 32: 1 0.9 0.8 0.7 0.6 0.5 0.4 0.3 0.2 0

- Page 33 and 34: to both turn models. Once the sourc

- Page 35 and 36: 2.3 Implementation Cost Other than

- Page 37 and 38: Name Pattern Example (b=4) Bit-comp

- Page 39 and 40: under this allocation scheme multip

- Page 41 and 42: to O1TURN and simpler than 2-phase

- Page 43: 2.2 Bit-complement 2.4 Bit-reverse

- Page 46 and 47: assertions about, or optimize for,

- Page 48 and 49: (1,…,p) RoutingLogic VirtualChann

- Page 50 and 51: fromothernodes toothernodes fromoth

- Page 52 and 53: conventional router architecture in

- Page 54 and 55:

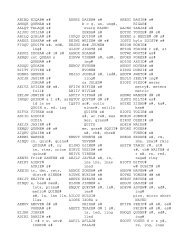

Architecture Ingress Demux Xbar Swi

- Page 56 and 57:

A B f B f A C D Figure 3-5: Deadloc

- Page 58 and 59:

Characteristic Configuration Topolo

- Page 60 and 61:

Total Throughput (packets/cycle) 5.

- Page 62 and 63:

3.4.4 Bursty Synthetic Tra c The te

- Page 64 and 65:

5 Shuffle (Burst) 6 Uniform Random

- Page 67 and 68:

Chapter 4 On-chip Network Support f

- Page 69 and 70:

Native Context (ENC). To the best o

- Page 71 and 72:

Core and Migration Core architectur

- Page 73 and 74:

the case where each core has a cont

- Page 75 and 76:

Figure 4-4: The percentage of acces

- Page 77 and 78:

grate on their own because, for exa

- Page 79 and 80:

4.4 Performance Evaluation 4.4.1 Ba

- Page 81 and 82:

network-independent traces (NITs) f

- Page 83 and 84:

Figure 4-5: Total migration cost of

- Page 85 and 86:

Figure 4-6: Total migration distanc

- Page 87 and 88:

Figure 4-8: Total migration cost of

- Page 89 and 90:

Chapter 5 Physical Implementation o

- Page 91 and 92:

accesses while it stays at the dest

- Page 93 and 94:

600 I/O pins, while flip chip can p

- Page 95 and 96:

(a) (b) Figure 5-2: EM 2 tile floor

- Page 97 and 98:

Figure 5-4: EM 2 tile layout that o

- Page 99 and 100:

Figure 5-5: EM 2 chip-level floorpl

- Page 101 and 102:

(a) Tile-level (b) Chip-level Figur

- Page 103 and 104:

(a) Tile-level view (b) Inside the

- Page 105 and 106:

of migration tra c. If we cannot si

- Page 107 and 108:

Chapter 6 Conclusions 6.1 Thesis Co

- Page 109 and 110:

Bibliography [1] Arvind, Nirav Dave

- Page 111 and 112:

[25] Hadi Esmaeilzadeh, Emily Blem,

- Page 113 and 114:

[51] Kangmin Lee, Se-Joong Lee, and

- Page 115 and 116:

[75] S. Rusu, Simon Tam, H. Muljono