Multi-programming, Time-sharing & Real-time systems - IIHE

Multi-programming, Time-sharing & Real-time systems - IIHE

Multi-programming, Time-sharing & Real-time systems - IIHE

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

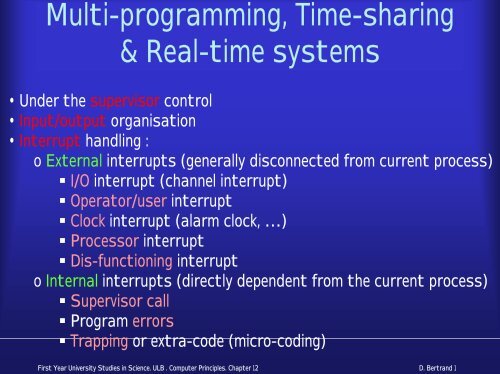

<strong>Multi</strong>-<strong>programming</strong>, <strong>Time</strong>-<strong>sharing</strong><br />

& <strong>Real</strong>-<strong>time</strong> <strong>systems</strong><br />

• Under the supervisor control<br />

• Input/output organisation<br />

• Interrupt handling :<br />

o External interrupts (generally disconnected from current process)<br />

• I/O interrupt (channel interrupt)<br />

• Operator/user interrupt<br />

• Clock interrupt (alarm clock, …)<br />

• Processor interrupt<br />

• Dis-functioning interrupt<br />

o Internal interrupts (directly dependent from the current process)<br />

• Supervisor call<br />

• Program errors<br />

• Trapping or extra-code (micro-coding)<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

D. Bertrand 1

A simple mechanism<br />

• The interrupt handling task is chosen by the supervisor<br />

• No interrupt during the current interrupt handling<br />

• Interrupts can be masked (to avoid uncontrolled sequence breaking)<br />

User process<br />

Masked<br />

event<br />

Unmasked<br />

event<br />

interrupt<br />

Supervisor<br />

Interrupt<br />

analysis<br />

Interrupt<br />

end<br />

Process<br />

calling<br />

end of<br />

handling<br />

Interrupt routines<br />

1 st type<br />

interruption<br />

2 nd type<br />

interruption<br />

Interrupts<br />

enabled<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

Interrupts<br />

disabled<br />

3 rd type<br />

interruption<br />

D. Bertrand 2

Implementation<br />

Registers :<br />

• General interrupt mask (MM = 1 : enabled; MM = 0 disabled) MM<br />

• Interrupt requests : array of bits IR<br />

• Interrupt masks : array of bits MS<br />

• Supervisor entry point for interrupt handling ES: 32 bits<br />

• PC saving memory zone<br />

PS: 32 bits<br />

Interrupts<br />

enabled ?<br />

MM=1 ?<br />

Interrupts<br />

masked ?<br />

yes<br />

n<br />

∑IRi.MS<br />

i<br />

≠ 0?<br />

i=1<br />

yes<br />

1 0 1 0 0 0 0 0 0 1 1 1 0 1 0 0<br />

0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1<br />

MM 0; PS PC<br />

PC ES<br />

1<br />

no<br />

I [PC]<br />

Execute I<br />

no<br />

• ES register can be replaced by an array<br />

• Each entry pointer to a specific service routine<br />

• Working registers saving (stack) !<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

D. Bertrand 3

<strong>Multi</strong><strong>programming</strong><br />

Variation in speed of various modules of a computer dead <strong>time</strong>s<br />

Task A<br />

input<br />

channel 1<br />

Processing<br />

output<br />

channel 2<br />

Task B<br />

Task B : timing ≡ timing task A; independent I/O channels<br />

input<br />

channel 3<br />

1<br />

Processing 1<br />

output<br />

channel 4 1<br />

1<br />

1 2 3 4 5 6 7 8 9 10<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

2<br />

3<br />

1 2<br />

3<br />

4<br />

5<br />

2<br />

1<br />

2<br />

2<br />

ideal configuration !!!<br />

3<br />

2<br />

3<br />

4<br />

3<br />

4<br />

3<br />

4<br />

5<br />

4<br />

5<br />

D. Bertrand 4<br />

4<br />

5<br />

<strong>time</strong>

Processes states<br />

• Concurrent processing : 3 states recognised by the scheduler<br />

• Working state : task using the control unit (computational state)<br />

• Waiting state : task waiting for an external resource<br />

• Ready state : task waiting for the control unit (main resource)<br />

• Scheduler serving the first ”ready” task<br />

• Priority system can be implemented<br />

system idle<br />

Task A<br />

waiting<br />

ready waiting ready ready<br />

Task B<br />

waiting<br />

ready<br />

waiting<br />

ready<br />

waiting ready<br />

Task C<br />

ready<br />

waiting<br />

ready<br />

waiting<br />

1 2 3 4 5 6 7 8 9 10<br />

<strong>time</strong><br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

D. Bertrand 5

Interrupt use<br />

• Task entering waiting state control given to supervisor :<br />

o Special interrupt : Supervisor call<br />

o System records the transition state (working waiting)<br />

o System records the restart condition (resource availability)<br />

o System chooses a task ready to work (priorities !)<br />

o Interrupt handling<br />

o State transition handling (scheduling work : next task to run)<br />

Task A<br />

switching <strong>time</strong> = supervision cost As small as possible !<br />

from task A<br />

1 2 3 4 5 6 7 8 9 10<br />

<strong>time</strong><br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

waiting<br />

Task B ready<br />

Task C ready ready<br />

Chan. 1 ready<br />

interrupt<br />

from chan. 1<br />

ready<br />

ready<br />

waiting<br />

D. Bertrand 6

Job classes and priorities<br />

Two main categories of processes :<br />

• CP-bound : computation in central memory; few I/O (number crunching)<br />

• IO-bound : little computation; many I/O operations<br />

• If only CP-bound processes : processor idle <strong>time</strong> very small<br />

no gain (even losses !) with multi-<strong>programming</strong><br />

• If only IO-bound processes : efficiency depends on synchronisation<br />

Mixture of CP-bound and I/O bound processes<br />

Task A I/O<br />

Task A<br />

Task B<br />

ready<br />

ready<br />

waiting<br />

ready<br />

ready<br />

waiting<br />

ready<br />

ready<br />

well-balanced<br />

system<br />

(use of clock inter.)<br />

Task A I/O<br />

Task A<br />

Task B<br />

ready<br />

ready<br />

waiting<br />

ready<br />

ready<br />

1 2 3 4 5 6 7<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

Unbalanced<br />

system<br />

(optimised for proc.<br />

not for periph.)<br />

<strong>time</strong><br />

D. Bertrand 7

Spooling<br />

• Sharing of ”sequential” peripherals (printers, magnetic tapes) difficult<br />

• Not a problem for random access devices (different areas)<br />

To solve the problem :<br />

Deferral output system<br />

• Output sent to a secondary storage device (magnetic disk, …)<br />

• At the end of the task output put into an output queue<br />

• When the device is ready : get one of the files of the output queue<br />

(special task : the output symbiont)<br />

Remarks<br />

• Symbiont : part of system software but handled as a user process<br />

• Queues can be built for different classes of peripherals (staging …)<br />

• A class of devices can be handled by the same or different symbionts<br />

• Same system can be applied to input queues<br />

• Priorities can be defined at the level of the queues<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

I/O device spooling<br />

D. Bertrand 8

Input<br />

device<br />

Input<br />

queue<br />

Input<br />

symbiont<br />

Job<br />

scheduler<br />

working<br />

Request<br />

Job evolution<br />

Process<br />

Process<br />

scheduler<br />

waiting<br />

Resources<br />

scheduler<br />

ready<br />

Output<br />

scheduler<br />

Output<br />

symbiont<br />

Termination<br />

Output<br />

device<br />

Output<br />

queue<br />

The operating system manages this evolution :<br />

tables (status of the system and of its components)<br />

o queue content<br />

o processes status<br />

o memory/peripherals occupation<br />

choices algorithms (scheduling)<br />

resource management (allocation)<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

D. Bertrand 9

<strong>Time</strong> <strong>sharing</strong><br />

<strong>Multi</strong>-programmation resource usage optimisation<br />

But …<br />

Response <strong>time</strong> ?<br />

Response <strong>time</strong> = reading <strong>time</strong> + waiting <strong>time</strong> in input queue<br />

+ execution <strong>time</strong><br />

+ waiting <strong>time</strong> in output queue + output <strong>time</strong><br />

execution <strong>time</strong> = Σ working <strong>time</strong>s + Σ waiting <strong>time</strong>s + Σ ready <strong>time</strong>s<br />

Reduction of processor idle <strong>time</strong> may be inefficient for response <strong>time</strong> !<br />

Example :<br />

• Two CP-bound tasks<br />

• Different execution <strong>time</strong>s (60 minutes ↔ 1 minute)<br />

• Tasks are submitted at different <strong>time</strong>s<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

D. Bertrand 10

1 st case :<br />

Task A<br />

Task B<br />

ready<br />

0 11<br />

• Looks like mono-programmation !<br />

60 61 <strong>time</strong><br />

• But control unit is quite efficiently used<br />

• User A happy !<br />

• User B must wait 50 minutes for the execution of one minute job !<br />

2 nd case :<br />

Task A<br />

Task B<br />

0 11 12 61<br />

<strong>time</strong><br />

• Less efficient (more switching <strong>time</strong>)<br />

• User B happy (response <strong>time</strong> reduced by 50)<br />

• User A still happy (response <strong>time</strong> increased by 1.5 %)<br />

• Average response <strong>time</strong> : 31 minutes (55 minutes in the first case)<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

D. Bertrand 11

Remarks<br />

• Many short processes delay for medium and long processes<br />

• Execution <strong>time</strong> is not always a priori known (errors, convergences, …)<br />

Other technique :<br />

• Put a working process in waiting state after a given <strong>time</strong> slice<br />

• Activate a ready process<br />

• Continue with another process …<br />

clock interrupt<br />

Task A<br />

Task B<br />

Task C<br />

ready<br />

ready<br />

<strong>Time</strong>-<strong>sharing</strong> :<br />

ready<br />

1 2 3 4 5 6 7 8 9 10<br />

<strong>time</strong><br />

• All processes systematically put to working state (quasi-parallelism)<br />

• Short processes quickly finished<br />

• Medium and long processes not indefinitely waiting<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

ready<br />

ready<br />

ready<br />

D. Bertrand 12

<strong>Multi</strong>-programmation<br />

<strong>Time</strong>-<strong>sharing</strong><br />

Comparison<br />

Simultaneous management<br />

of several processes<br />

<strong>Multi</strong>-management <strong>systems</strong><br />

Main aim Method Consequence<br />

<strong>Multi</strong>-programmation<br />

optimisation of<br />

control unit usage<br />

Management of<br />

several processes<br />

quasi-parallelism<br />

<strong>Time</strong>-<strong>sharing</strong><br />

Response <strong>time</strong><br />

optimisation (users)<br />

Management of<br />

several processes<br />

better use of<br />

active resources<br />

Some operating <strong>systems</strong> based on a compromise<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

D. Bertrand 13

Interactive <strong>systems</strong><br />

• Task directives given interactively by the user<br />

• Each user has its own access units (terminal : keyboard + screen)<br />

• The user units do not need to be driven by a symbiont<br />

• Commands generate interrupts and tasks state transition<br />

Average response <strong>time</strong> = n . t<br />

n : number of users; t : average execution <strong>time</strong> of a command<br />

• In general system in waiting state<br />

• Each user get the impression to have his own computer<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

D. Bertrand 14

<strong>Real</strong> <strong>time</strong> <strong>systems</strong><br />

<strong>Time</strong>-<strong>sharing</strong> <strong>systems</strong> with strict timing constraints<br />

Systems requiring minimum response <strong>time</strong> :<br />

• Process control in industry<br />

• Probe control in space<br />

• Electronic assistance <strong>systems</strong> in cars<br />

• Flying <strong>systems</strong> in planes<br />

• Data acquisition <strong>systems</strong> (physics, chemistry, …)<br />

Systems requiring fast but not critical response <strong>time</strong> :<br />

• Reservation <strong>systems</strong> (plane, trains, …)<br />

• Automatic banking <strong>systems</strong>, …<br />

First Year University Studies in Science. ULB . Computer Principles. Chapter 12<br />

D. Bertrand 15