implementation of turbo decoder using max-log-map ... - ijater

implementation of turbo decoder using max-log-map ... - ijater

implementation of turbo decoder using max-log-map ... - ijater

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

International Journal <strong>of</strong> Advanced Techno<strong>log</strong>y & Engineering Research (IJATER)<br />

IMPLEMENTATION OF TURBO DECODER<br />

USING MAX-LOG-MAP ALGORITHM FOR<br />

WIRELESS APPLICATION<br />

Mr. RAGHUKRISHNA.S 1, Dr. K. N. HARI BHATT 2<br />

1,2 Nagarjuna College <strong>of</strong> Engineering and Techno<strong>log</strong>y, Bangalore, Karnataka, India.<br />

Email: raghukrishnas85@gmail.com, knhari.bhat@gmail.com<br />

Abstract<br />

Turbo code is one <strong>of</strong> the most significant achievements<br />

in coding theory. Turbo decoding architectures have<br />

greater error correcting capability than any other known<br />

code. The successive decoding procedures carried out in<br />

the conventional Max-Log-MAP algorithm are performed<br />

in parallel, and well formulated into a set <strong>of</strong> simple and<br />

regular matrix operations, which can therefore considerably<br />

speed up the decoding operations and reduce the computational<br />

complexity. The Max-Log-MAP algorithms also<br />

maintain the advantage <strong>of</strong> the general <strong>log</strong>arithmic MAP<br />

like algorithms in avoiding complex numerical representation<br />

problems. The Max-Log-Map algorithm is the least<br />

complex <strong>of</strong> the four algorithms (MAP, LOG-MAP, SOVA<br />

and Improved SOVA). It has twice the complexity <strong>of</strong> the<br />

Viterbi algorithm for each half-iteration but <strong>of</strong>fers the<br />

worst BER performance. The Max-Log-Map algorithm<br />

has the additional benefit <strong>of</strong> being tolerant <strong>of</strong> imperfect<br />

noise variance estimates when operating on an AWGN<br />

channel.<br />

In 1948 paper, Shannon defined the limits <strong>of</strong> a communication<br />

System. The gap between the Shannon limit<br />

and practice was still 2dB until 1993[1]. Berrou et al in<br />

1993introduced a major advancement in the channel coding<br />

area was the advent <strong>of</strong> <strong>turbo</strong> codes [1][8]. Their decoding<br />

complexity was very high for them to be efficiently<br />

implemented in hardware when compared with a <strong>decoder</strong><br />

for convolutional codes like a Viterbi <strong>decoder</strong> [3]. Demand<br />

for <strong>turbo</strong> codes in wireless communication systems<br />

has been increasing since their appearance in the early<br />

1990s, due to their outstanding performance in terms <strong>of</strong> bit<br />

error rate (BER) [2]. For this reason, they have been<br />

adopted by various wireless systems such as DVB-RCS,<br />

3GPP UMTS, IEEE 802.16, and CCSDS [2]. Various <strong>turbo</strong><br />

<strong>decoder</strong>s have been developed to improve their performance<br />

at algorithm and architecture levels. A Dual<br />

mode <strong>decoder</strong> for convolutional and <strong>turbo</strong> codes have also<br />

been introduced for multi-standard wireless Communication<br />

systems. Since there are different methods and approaches<br />

for decoding the received signals at the receiver,<br />

but in general trellis-based algorithms are commonly used.<br />

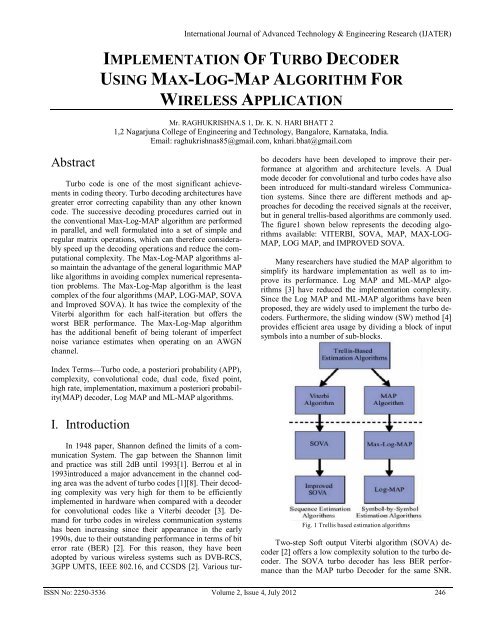

The figure1 shown below represents the decoding algorithms<br />

available: VITERBI, SOVA, MAP, MAX-LOG-<br />

MAP, LOG MAP, and IMPROVED SOVA.<br />

Many researchers have studied the MAP algorithm to<br />

simplify its hardware <strong>implementation</strong> as well as to improve<br />

its performance. Log MAP and ML-MAP algorithms<br />

[3] have reduced the <strong>implementation</strong> complexity.<br />

Since the Log MAP and ML-MAP algorithms have been<br />

proposed, they are widely used to implement the <strong>turbo</strong> <strong>decoder</strong>s.<br />

Furthermore, the sliding window (SW) method [4]<br />

provides efficient area usage by dividing a block <strong>of</strong> input<br />

symbols into a number <strong>of</strong> sub-blocks.<br />

Index Terms—Turbo code, a posteriori probability (APP),<br />

complexity, convolutional code, dual code, fixed point,<br />

high rate, <strong>implementation</strong>, <strong>max</strong>imum a posteriori probability(MAP)<br />

<strong>decoder</strong>, Log MAP and ML-MAP algorithms.<br />

I. Introduction<br />

Fig. 1 Trellis based estimation algorithms<br />

Two-step S<strong>of</strong>t output Viterbi algorithm (SOVA) <strong>decoder</strong><br />

[2] <strong>of</strong>fers a low complexity solution to the <strong>turbo</strong> <strong>decoder</strong>.<br />

The SOVA <strong>turbo</strong> <strong>decoder</strong> has less BER performance<br />

than the MAP <strong>turbo</strong> Decoder for the same SNR.<br />

ISSN No: 2250-3536 Volume 2, Issue 4, July 2012 246

The MAP algorithm provides the best performance in<br />

BER while its complexity is higher than the two-step SO-<br />

VA.<br />

II. Turbo Encoder Structure<br />

International Journal <strong>of</strong> Advanced Techno<strong>log</strong>y & Engineering Research (IJATER)<br />

(A)<br />

B. ML-MAP SISO Decoder Architecture<br />

Fig. 2 Turbo encoder structure<br />

A generic structure for <strong>turbo</strong> encoding based on parallel<br />

concatenation <strong>of</strong> two Recursive Systematic Convolutional<br />

(RSC) encoders is given in Fig 2. Two identical<br />

RSC encoders produce the redundant data as parity bits.<br />

The input data stream and parity bits are combined in series<br />

to form the <strong>turbo</strong> coded word. The size <strong>of</strong> the input<br />

data word may vary from 40 bits to 6144 bits for UMTS<br />

[1] and take specified values such as 378, 570, and 20730<br />

for CDMA2000 [6] <strong>turbo</strong> coding which are the two main<br />

standards <strong>of</strong> 3GPP and 3GPP2 respectively.<br />

III. Turbo Decoder<br />

A. Turbo Decoder Structure<br />

Figure 4 shows the SISO <strong>decoder</strong> architecture which<br />

consists <strong>of</strong> the forward and backward state metric, LLR<br />

computation, and memory (LIFO and FIFO) blocks. The<br />

FIFO 1 and 2 are used to Buffer the input data symbols<br />

and the LIFO 3 and 4 are to store the forward state metric<br />

and the LLR values, respectively. The SISO <strong>decoder</strong> has<br />

been built with two backward state metric units, β1 and<br />

β2. α and γ denote the forward state and branch metric<br />

units.<br />

Fig. 4 SISO Architecture<br />

The ML-MAP algorithm can be used for reduced<br />

complexity <strong>decoder</strong> <strong>implementation</strong> [4].The decoding<br />

process in MAP algorithm performs calculations <strong>of</strong> the<br />

forward and backward state metric values to obtain the <strong>log</strong><br />

likelihood ratio (LLR) values, which have the decoded bit<br />

information and reliability values. The LLR values are<br />

represented by the Following equation [6]:<br />

Fig. 3 Iterative Turbo- Decoder<br />

The <strong>turbo</strong> <strong>decoder</strong> structure represents two s<strong>of</strong>t-input<br />

s<strong>of</strong>t-output (SISO) <strong>decoder</strong>s and one interleaver/deinterleaver<br />

between them. Decoding process in a <strong>turbo</strong><br />

<strong>decoder</strong> is performed iteratively through the two SISO<br />

<strong>decoder</strong>s via the interleaver and the deinterleaver. As<br />

shown in Figure 3. When the Maximum A Posteriori<br />

(MAP) algorithm is applied to each SISO <strong>decoder</strong>, the<br />

Log-Likelihood Ratio (LLR) for each double-binary pair<br />

can be expressed as equation (A) [7]:<br />

k-1. The equation <strong>of</strong> γ, α, and β can be represented to <strong>log</strong>arithm<br />

form as shown below [3],[6]:<br />

ISSN No: 2250-3536 Volume 2, Issue 4, July 2012 247

International Journal <strong>of</strong> Advanced Techno<strong>log</strong>y & Engineering Research (IJATER)<br />

The main kernel <strong>of</strong> the Turbo-Viterbi algorithm is<br />

ADD-COMPARE-SELECT (ACS) operation which is<br />

performed by Forward recursion, Reverse recursion and<br />

dummy reverse recursion blocks. There are 8 parallel ACS<br />

blocks and hence 8 states can be processed in parallel. Fully<br />

parallel architectures assign one ACS for each state to<br />

meet the performance constraints on speed and latency [5].<br />

Where the branch metric (γ) is calculated by the a priori<br />

information (Le), channel reliability value (Lc), input<br />

Symbols (x and y1), the systematic bit (uk s) and the parity<br />

bit (uk p). As described in previous section, a priori information<br />

is obtained from the LLR value computed in<br />

previous decoding process after subtracting the input symbol<br />

data and a priori values from the LLR value. The MAP<br />

algorithm, which uses the above equations, is not suitable<br />

for hardware <strong>implementation</strong> due to the <strong>log</strong>arithm function.<br />

This problem can be addressed <strong>using</strong> a well know<br />

approximation, called Jacobi <strong>log</strong>arithm, which is given below.<br />

1. Branch And State Metric Unit:<br />

The branch and state metric units (BMU and SMU)<br />

are implemented <strong>using</strong> ML-MAP algorithm. The conventional<br />

BMU and SMU consists <strong>of</strong> branch metric calculation,<br />

add, compare, select, and normalization processes<br />

which is shown in fig 5. The general SMU in <strong>turbo</strong> SISO<br />

<strong>decoder</strong> must include the normalization process to avoid<br />

overflow <strong>of</strong> the state metric values [3].<br />

This approximation is used to implement the state metric<br />

unit (SMU) and LLR computation unit (LCU) in Log<br />

MAP and ML-MAP SISO <strong>decoder</strong>. The 2nd term <strong>of</strong> the<br />

right hand side in equation (4) is a correction term which<br />

can be implemented through a simple look-up table [3].<br />

However, the correction term is ignored in this paper as<br />

we have implemented ML-MAP SISO <strong>decoder</strong>.<br />

C. Specifications<br />

Complexity studies showed that Max-Log-MAP is the<br />

Best compromise between performance and complexity<br />

when compared with MAP, Log-MAP and SOVA. Therefore,<br />

our <strong>implementation</strong> will be based on the Max-Log-<br />

MAP algorithm. Regarding Turbo <strong>decoder</strong> <strong>implementation</strong>s,<br />

several interesting <strong>implementation</strong>s were recently<br />

proposed, most <strong>of</strong> which are based on fixed-point arithmetic<br />

[6]. Since fixed-point operations require multiplications<br />

and divisions for normalization, computational complexity<br />

is still high. In this paper, we propose an integer<br />

based Turbo <strong>decoder</strong>. The <strong>turbo</strong> <strong>decoder</strong> considered in this<br />

paper has the following specifications:<br />

I. Code rate R = 1/3.<br />

II. Puncturing pattern: even/odd parity.<br />

III. Block size: N = 40 to 6144 bits.<br />

IV. Interleaver: S-random interleaver with S = 8.<br />

Fig. 5 conventional structures <strong>of</strong> the branch and state metric units<br />

The branch metric values are obtained from input data<br />

symbols. The new state metric values are calculated in<br />

single clock cycle recursively <strong>using</strong> add, compare (C), select,<br />

and normalization (N) processes from branch metric<br />

and state metric values [3],[6].<br />

The critical path delay is determined by the above<br />

processes. In the proposed architecture which is shown in<br />

fig 6 the normalization is done in the branch metric values<br />

itself. This normalization method leads to a simplified<br />

SMU (shown in fig.7) [3], but more complex in BMU.<br />

The novel architecture reduces the critical path delay significantly<br />

by eliminating the state metric normalization<br />

process used in the conventional SMU [6].<br />

D. Implementation<br />

ISSN No: 2250-3536 Volume 2, Issue 4, July 2012 248

International Journal <strong>of</strong> Advanced Techno<strong>log</strong>y & Engineering Research (IJATER)<br />

Fig. 6 Branch Metric Unit.<br />

Fig. 9 Conventional LCU Units<br />

Fig. 7 SMU Unit<br />

2. Normalization / Saturation:<br />

To avoid overflow metrics, Normalization is usually<br />

employed as shown in figure 5 and 6. We have adopted a<br />

very efficient normalization scheme where at each time<br />

instant we check if any <strong>of</strong> the state metrics is greater than<br />

2,[5] then a fixed value 2 is subtracted from all<br />

state metrics. This is shown by normalization (N) block<br />

shown in figure 5 and 6[3]. The block comprises <strong>of</strong> a subtractor<br />

that subtracts a fixed value (2) from state metrics<br />

and a multiplexer that selects the subtracted value if<br />

the normalization has to be employed. The multiplexer select<br />

signal is provided by each ACS block and in case <strong>of</strong><br />

state serial architecture <strong>map</strong>pings (states >8) the select<br />

signal is provided after all the states are processed [5].<br />

The LLR values (L1 or L0) are calculated <strong>using</strong> forward<br />

(α0-7) and backward (β0-7) states and branch metric<br />

(γ0-1) values <strong>of</strong> all states. The LLR computation unit<br />

(LCU) is similar to the SMU which consists <strong>of</strong> 3-stage<br />

compare and select process results long critical path delay.<br />

In order to reduce the critical path delay LCU is pipelined<br />

[6].<br />

E. LLR Output Iterations<br />

The output L (dˆ) <strong>of</strong> the <strong>decoder</strong> in Figure 10 is made<br />

up <strong>of</strong> the LLR from the detector, L′ (dˆ), and the extrinsic<br />

LLR output, Le (dˆ), representing knowledge gleaned<br />

from the decoding process. As illustrated in Figure 10, for<br />

iterative decoding, the extrinsic likelihood is fed back to<br />

the <strong>decoder</strong> input, to serve as a refinement <strong>of</strong> the a priori<br />

probability <strong>of</strong> the data for the next iteration [9].<br />

3. LLR COMPUTATION UNIT:<br />

Fig. 10 LLR iteration output values<br />

ISSN No: 2250-3536 Volume 2, Issue 4, July 2012 249

International Journal <strong>of</strong> Advanced Techno<strong>log</strong>y & Engineering Research (IJATER)<br />

The <strong>log</strong>-MAP algorithm is the most complex <strong>of</strong> the<br />

four algorithms when implemented in s<strong>of</strong>tware, but as will<br />

be shown later, generally <strong>of</strong>fers the best bit error rate<br />

(BER) performance. The <strong>max</strong>-<strong>log</strong>-MAP algorithm is the<br />

least complex <strong>of</strong> the four algorithms (it has twice the<br />

complexity <strong>of</strong> the Viterbi algorithm for each half-iteration)<br />

but <strong>of</strong>fers the worst BER performance [9]. The <strong>max</strong>-<strong>log</strong>-<br />

MAP algorithm has the additional benefit <strong>of</strong> being tolerant<br />

<strong>of</strong> imperfect noise variance estimates when operating on<br />

an AWGN channel.<br />

F. SIMULATION RESULTS<br />

pipelining architecture introducing for performing LLR<br />

value computations, has been shown that <strong>decoder</strong><br />

achieved a slight reduction in power consumption and a<br />

slight increase in area usage, it has achieved 58% speedup<br />

compared to non-pipelined conventional <strong>decoder</strong>.<br />

Therefore, by adopting this kind <strong>of</strong> techniques, the <strong>turbo</strong><br />

<strong>decoder</strong> can be applied to wireless communication systems<br />

requiring high data rates and low power consumption.<br />

Further <strong>implementation</strong> <strong>of</strong> improved techno<strong>log</strong>ies<br />

like “sliding window” can improve the performance with<br />

slight increase in resources.<br />

V. Acknowledgment<br />

The authors would like to thank Dr. A. T. Kalghatgi,<br />

Chief Scientist, Mr. Manoj Jain, Member (Senior Research<br />

Staff), Mrs. A.Thirija Sharmila, Member (Senior<br />

Research Staff) and Mr. Chaitanya Umbare Member (Research<br />

Staff), Central Research Laboratory, Bangalore, for<br />

their constant encouragement and support to carry out this<br />

work.<br />

VI. References<br />

Fig. 7 Branch metric result <strong>using</strong> MODELSIM<br />

The ML-MAP <strong>turbo</strong> SISO <strong>decoder</strong> presented in this<br />

paper was initially simulated at high level to verify its<br />

functionality. In our simulation a 1024 size block type interleaver<br />

has been used.<br />

Fig. 8 State metric result <strong>using</strong> MODELSIM<br />

The figure 7 above represents the branch metric {γ}<br />

and fig 8 represents the state metric {α} for the value <strong>of</strong> k<br />

= 1024 and system and parity bits <strong>of</strong> length 1024.<br />

IV. Conclusion<br />

Normalize operation was applied to branch metric<br />

values instead <strong>of</strong> to state metric values. In addition, with<br />

[1] Mustafa Taskaldiran, Richard C.S. Morling, and<br />

Izzet Kale. “The Modified Max-Log-MAP Turbo<br />

Decoding Algorithm by Extrinsic Information Scal<br />

ing for Wireless Applications”.<br />

[2]. J. H. Han, A. T. Erdogan, and T. Arslan. “A Power<br />

Efficient Reconfigurable Max-Log-MAP Turbo De<br />

coder for Wireless Communication Systems”.<br />

[3]. J. H. Han, A. T. Erdogan, T. Arslan “High Speed<br />

Max-Log-MAP Turbo SISO DecoderImplementtion<br />

Using Branch Metric Normalization”.<br />

[4]. Hirohisa GAMBE, Yoshinori TANAKA, Kazuhisa<br />

OHBUCHI, Teruo ISHIHARA, and Jifeng LI. “An<br />

Improved Sliding Window Algorithm for Max-Log-<br />

MAP Turbo Decoder and Its Programmable LSI Im<br />

plementation”.<br />

[5]. Shivani verma and kumar.s “An FPGA realization<strong>of</strong><br />

simplified <strong>turbo</strong> <strong>decoder</strong> architecture” International<br />

Journal <strong>of</strong> the Physical Sciences.Vol. 6(10), pp.<br />

2338-2347, 18 May, 2011<br />

[6]. J.M.Mathana, Dr.P.Rangarajan “FPGA Implementa<br />

tion <strong>of</strong> High Speed Architecture for Max Log Map<br />

Turbo SISO Decoder.” International Journal <strong>of</strong> Re<br />

cent Trends in Engineering, Vol 2, No. 6, Novem<br />

ber 2009.<br />

[7]. Huili Guo, Juntao Zhao, Jianwen Chen, Xiang Chen,<br />

Jing Wang “High Performance Turbo Decoder on<br />

CELL BE for WiMAX System”.<br />

[8]. Hye-Mi Choi, Ji-Hoon Kim, and In-Cheol Park<br />

“Low- Power Hybrid Turbo Decoding Based on Re<br />

ISSN No: 2250-3536 Volume 2, Issue 4, July 2012 250

verse Calculation”.<br />

[9]. Bernard Sklar “Digital Communications: Fundamen<br />

tals and Applications”, Second Edition (Prentice<br />

Hall,2001, ISBN 0-13-084788-7).<br />

Biographies<br />

International Journal <strong>of</strong> Advanced Techno<strong>log</strong>y & Engineering Research (IJATER)<br />

RAGHUKRISHNA.S received B.E. degree in Electronics<br />

and Communication engineering in 2008 and M.Tech degree<br />

in VLSI Design and Embedded systems in 2012 from<br />

Visveswaraya Techno<strong>log</strong>ical University, Karnataka. His<br />

main area <strong>of</strong> interest includes Error Control Coding and<br />

VLSI Design.<br />

Email: raghukrishnas85@gmail.com<br />

K.N. HARI BHATT received the B.E. degree with honours<br />

from Mysore University in 1966. M.Tech and Ph.D.<br />

degrees in Electronics and Communication Engineering<br />

from Indian Institute <strong>of</strong> Techno<strong>log</strong>y, Kanpur in 1973 and<br />

1986 respectively. He is currently working as Dean Academic<br />

and Head, Department <strong>of</strong> Electronics and Communication<br />

Engineering (P.G.) at Nagarjuna College <strong>of</strong> Engineering<br />

and Techno<strong>log</strong>y, Bangalore, India. He was with<br />

Karnataka Regional Engineering College, Suratkal (now<br />

known as National Institute <strong>of</strong> Techno<strong>log</strong>y, Karnataka) for<br />

more than 30 years up to 2001. He has coauthored three<br />

books in the area <strong>of</strong> Communication. His areas <strong>of</strong> interest<br />

are Ana<strong>log</strong> and Digital communication and Cryptography.<br />

Email: knhari.bhat@gmail.com<br />

ISSN No: 2250-3536 Volume 2, Issue 4, July 2012 251