Chapter 2 Real-Time Systems Concepts Foreground/Background ...

Chapter 2 Real-Time Systems Concepts Foreground/Background ...

Chapter 2 Real-Time Systems Concepts Foreground/Background ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

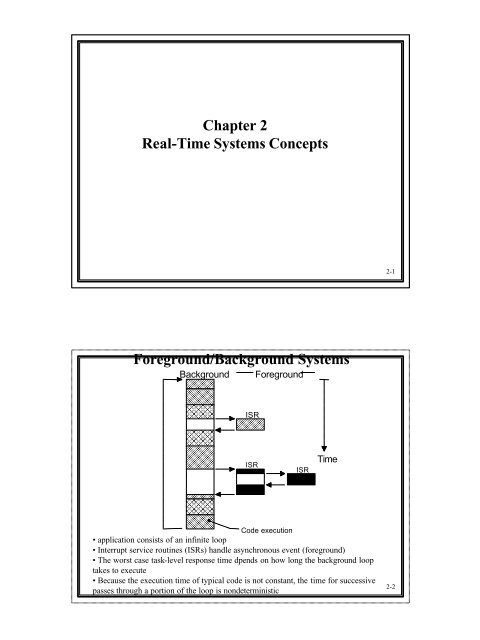

<strong>Chapter</strong> 2<strong>Real</strong>-<strong>Time</strong> <strong>Systems</strong> <strong>Concepts</strong>2-1<strong>Foreground</strong>/<strong>Background</strong> <strong>Systems</strong><strong>Background</strong> <strong>Foreground</strong>ISRISRISR<strong>Time</strong>Code execution•application consists of an infinite loop•Interrupt service routines (ISRs) handle asynchronous event (foreground)•The worst case task-level response time dpends on how long the background looptakes to execute•Because the execution time of typical code is not constant, the time for successivepasses through a portion of the loop is nondeterministic2-2

Critical Section• The critical section– A piece of code which cannot be interrupted during execution• Cases of critical sections– Modifying a block of memory shared by multiple kernel services• Process table• Ready queue, waiting queue, delay queue, etc.– Modifying global variables used by kernel• Entering a critical section– Disable global interrupt - disable()• Leaving a critical section– Enable global interrupt - enable()2-32-4

• Resource– EX: I/O, CPU, Memory, Printer, …• Shared Resource– The resources which are shared among the tasks– Each task should gain exclusive access to the shared resource toprevent data corruption è Mutual exclusion• Task and Thread (herein both terminology represent asame thing)– A simple program that thinks it has the CPU all to itself– Each task is an infinite loop– It has five state: Dormant, Ready, Running, Waiting, and ISR(Interrupted)2-5TASK #1 TASK #2 TASK #nStack Stack StackFigure 2.2Multiple TaskTask Control BlockStatusTask Control BlockStatusTask Control BlockStatusSPSPSPPriorityPriorityPriorityMEMORYCPUCPU RegistersSPContext2-6

Figure 2.3 Task StatesWAITINGOSTaskDel()OSMBoxPost()OSQPost()OSQPostFront()OSSemPost()OSTaskResume()OS<strong>Time</strong>DlyResume()OS<strong>Time</strong>Tick()OSMBoxPend()OSQPend()OSSemPend()OSTaskSuspend()OS<strong>Time</strong>Dly()OS<strong>Time</strong>DlyHMSM()DORMANTOSTaskCreate()OSTaskCreateExt()OSTaskDel()READYOSStart()OSIntExit()OS_TASK_SW()RUNNINGInterruptOSIntExit()ISRTask is PreemptedOSTaskDel()2-7Context Switch (or Task Switch)• Each task has its stack to store the associated information• The purpose of context switch– To make sure that the task, which is forced to give up CPU, canresume operation later without lost of any vital information or data• The procedure of interrupt•••MP_addr(n) : instruction(n)MP_addr(n+1) : instruction(n+1)MP_addr(n+2) : instruction(n+2)•••InterruptreturnfrominterruptPush flagsPush MP_addr(n+1)Push CPU registers•• ; isr codes•pop CPU registersreturn ; jump back to; MP_addr(n+1) 2-8

• <strong>Foreground</strong>/background programming– Context (CPU registers and interrupted program address) save andrestore using one stack• Multi-tasking context switch– Using each task’s own stackCurrent CPU stack pointerTask1’s local variablesReturn address (optional)Task 1 (to be switched from) stackCPU registers whenTask 2 was switchedTask 2’s code addresswhen it was switchedTask 2’s local variableswhen it was switchedReturn address (optional)Task 2 (to be switched to) stack2-9• During context switchTask1’s local variablesReturn address (optional)Task 1 stackCPU registers whenTask 2 was switchedTask 2’s code addresswhen it was switchedTask 2’s local variableswhen it was switchedReturn address (optional)Task 2 stackTask 1 TCBCurrentProgramaddressCurrentCPUregistersTask 2 TCBStack pointerCurrent CPU stack pointerStack pointer2-10

• After context switchCPU registers whenTask 1 was switchedTask 1’s code addresswhen it was switchedTask 1’s local variableswhen it was switchedReturn address (optional)Task 1 (suspended) stackCurrent CPU stack pointerTask1’s local variablesReturn address (optional)Task 2 (current) stack2-11The Operations of Context Switch• Rely Interrupt (hardware or software, into kernel mode) todo context switch– Push return address– Push FLAGS register• ISR (context switch routine)– Push all register– Store sp to TCB (task control block)– Select a ready task which has the highest priority (Scheduler)– Restore the sp from the TCB of the new selected task– Pop all register– iret (interrupt return which will pop FLAGS and return address)• Switch to new task2-12

Scheduler• Also called the dispatcher• Determine which task will run next• In a priority-based kernel, control of the CPU is alwaysgiven to the highest priority task ready to run• Two types of priority-based kernels– Non-preemptive– preemptive2-13Non-preemptive• Task auto gives up the control of the CPU• Also called cooperative multitasking– Tasks cooperate with each other to share the CPU• advantages– Can use non-reentrant function– Without fear of corruption by another task (less need to guard shareddata through the use of semaphores)– Interrupt latency is typically low (don’t need to disable interrupt)– Task-level response time much lower than the foreground/background• Worst case is the longest task time2-14

Figure 2.4 Non-preemptive kernelLow Priority Task(1) (2)ISR(3)(4)(5)ISR makes the highpriority task ready<strong>Time</strong>(6)High Priority TaskLow priority taskrelinquishes the CPU(7)2-15Preemptive Kernel• Used in the high system responsiveness• The highest priority task ready to run is always givencontrol of the CPU– When a task make a higher priority task ready to run, the currenttask is preempted and the higher priority task is immediately givencontrol of the CPU– If an ISR makes a higher priority task ready, when the ISRcompletes, the interrupted task is suspended and the new higherpriority task is resumed• The use of non-reentrant functions requires to cooperatewith mutual exclusion semaphores2-16

Figure 2.5 Preemptive kernelLow Priority TaskISRHigh Priority TaskISR makes the highpriority task ready<strong>Time</strong>2-17Reentrancy• Reentrant function– Can be used by more than one task in concurrent without fear ofdata corruption– Can be interrupted at any time and resumed at a later time withoutloss of data– Use local variablevoid strcpy(char *dest, char *src){while (*dest++ = *src++) {;}*dest = NUL;}Listing 2.1 Reentrant functionint Temp;void swap(int *x, int *y){Temp = *x;*x = *y;*y = Temp;}Listing 2.2 Non-reentrant function 2-18

Figure 2.6 Non-reentrant functionLOW PRIORITY TASKHIGH PRIORITY TASKwhile (1) {x = 1;y = 2;}swap(&x, &y);{Temp = *x;*x = *y;*y = Temp;}..OS<strong>Time</strong>Dly(1);Temp == 1OSIntExit()(2)ISR(1)(5)Temp == 3!O.S.O.S.Temp == 3(3)(4)while (1) {z = 3;t = 4;}swap(&z, &t);{Temp = *z;*z = *t;*t = Temp;}..OS<strong>Time</strong>Dly(1);..2-19Task Priority• Static priorities– The priority of each task does not change during the application’sexecution• Dynamic priorities– The priority of tasks can be changed during the application’sexecution2-20

Figure 2.7 Priority Inversion problemPriority InversionTask 1 (H)(4)(12)Task 2 (M)(8)Task 3 (L)(1)(6)(10)Task 3 Get Semaphore(2)Task 1 Preempts Task 3(3)Task 1 Tries to get Semaphore(5)Task 3 Resumes(9)Task 3 Releases the Semaphore(11)Task 2 Preempts Task 3(7)2-21Figure 2.8 Kernel that supports priority inheritancePriority InversionTask 1 (H)(5)(9)Task 2 (M)(11)Task 3 (L)(1)(3)(7)Task 3 Get Semaphore(2)Task 1 Preempts Task 3(4)Task 1 Completes(10)Task 1 Tries to get Semaphore(Priority of Task 3 is raised to Task 1's)(6)Task 3 Releases the Semaphore(Task 1 Resumes)(8)2-22

Assigning Task Priorities• Rate Monotonic Scheduling (RMS)– The highest rate of execution are given the highest priority• RMS makes a number of assumptions:– All tasks are periodic (they occur at regular intervals).– Tasks do not synchronize with one another, share resources, orexchange data.– The CPU must always execute the highest priority task that is ready torun. In other words, preemptive scheduling must be used.• If meet the following inequality equation, all task HARD real-timedeadlines will be met∑iETii⎛≤ n × ⎜2⎝1n⎟ ⎞−1⎠CPU utilization of all timecriticaltasks should be less than70%Other 30% can be used by nontimecritical tasks2-23Mutual Exclusion• Multiple tasks access same area (critical section) mustensure that each task has exclusive access to the data toavoid contention and data corruption• The method of exclusive access– Disabling interrupts– Performing test-and-set operations– Disabling scheduling– Using semaphores2-24

• Disabling and enabling interruptsDisable interrupts;Access the resource (read/write from/to variables);Reenable interrupts;• uc/OS-II provides two macros to disable/enable interruptvoid Function (void){OS_ENTER_CRITICAL();.. /* You can access shared data in here */.OS_EXIT_CRITICAL();}• Not to disable interrupts for too long– Affect the response of your system to interrupts (interrupt latency)2-25• Test-and-Set (TAS)Disable interrupts;if (‘Access Variable ’ is 0) {Set variable to 1;Reenable interrupts;Access the resource;Disable interrupts;Set the ‘Access Variable’back to 0;Reenable interrupts;} else {Reenable interrupts;/* You don’t have access to the resource, try back later; */}• Some processor actually implement a TAS operation inhardware (e.g., 68000 family)2-26

• Disabling and Enabling the Scheduler– If no shared variables or data structures with an ISR, we candisable and enable schedulingvoid Function (void){OSSchedLock();.. /* You can access shared data in here */.OSSchedUnlock();}– Two or more tasks can share data without contention– While the scheduler is locked, interrupts are enable• If the ISR generates a new event which enables a higherpriority, the higher priority will be run when theOSSchedunlock() is called.2-27Semaphores• Semaphores are used to– Control access to a shared resource (mutual exclusion)– Signal the occurrence of an event– Allow two tasks to synchronize their activities• Two types of semaphores– Binary semaphores– Counting semaphores• Three operations of a semaphore– INITIALIZE (called CREATE)– WAIT (called PEND)– SIGNAL (called POST) --Release semaphore• Highest priority task waiting for the semaphore is activized (uCOS-IIsupports this one)• First task that requested the semaphore is activized (FIFO)2-28

• Accessing shared data by obtaining a semaphoreOS_EVENT *SharedDataSem;void Function (void){INT8U err;OSSemPend(SharedDataSem, 0, &err);.. /* You can access shared data in here (interrupts are recognized) */.OSSemPost(SharedDataSem);}2-29• Control of shared resources (multual exclusion)– e.g., single display devicetask1( ... ){...printf("This is task 1.");...}task2( ... ){...printf("This is task 2.");...}Results may be:ThiThsi siis ttasaks k12..Exclusive usageof certain resources(e.g., shared memory)2-30

• Solution: using a semaphore and initialized it to 1TASK 1"I am task #1!"Acquire SemaphoreSEMAPHOREPRINTERAcquire SemaphoreTASK 2"I am task #2!"• Each task must know about the existence of semaphore inorder to access the resource– Some situations may encapsulate the semaphore is better2-31INT8U CommSendCmd(char *cmd , char *response, INT16U timeout){Acquire port's semaphore;Send command to device;Wait for response (with timeout);if (timed out) {Release semaphore;return (error code);} else {Release semaphore;return (no error);}}Figure 2.11 Hiding a semaphore from tasksTASK1CommSendCmd()DRIVERRS-232CTASK2CommSendCmd()Semaphore2-32

BUF * BufReq(void){BUF *ptr;Acquire a semaphore;Disable interrupts;ptr = BufFreeList;BufFreeList = ptr->BufNext;Enable interrupts;return (ptr);}Counting semaphoreBufFreeListBufReq()Next Next Next 010BufRel()Buffer Managervoid BufRel(BUF *ptr){Disable interrupts;ptr->BufNext = BufFreeList;BufFreeList = ptr;Enable interrupts;Release semaphore;}Task1Task22-33Deadlock• To avoid a deadlock the tasks is– Acquire all resources before proceeding– Acquire the resources in the same order– Release the resources in the reverse order• Using timeout when acquiring a semaphore– When a timeout occur, a return error code prevents the task formthinking it has obtained the resource.• Deadlocks generally occur in large multitasking systems,not in embedded systems2-34

Synchronization• A task can be synchronized with an ISR or a task– A task initiates an I/O operation and waits for the semaphore– When the I/O operation is complete, an ISR (or another task) sig nals thesemaphore and the task is resumedISRPOSTPENDTASKUnilateral rendezvousTASKPOSTPENDTASK• Tasks synchronizing their activitiesPOSTPENDbilateral rendezvousTASKTASKPENDPOST2-35Bilateral rendezvousTask1(){}for (;;) {}Perform operation;Signal task #2; (1)Wait for signal from task #2; (2)Continue operation;Task2(){}for (;;) {}Perform operation;Signal task #1; (3)Wait for signal from task #1; (4)Continue operation;2-36

Event Flags (uCOS-II does not support)• Used in a task needs to synchronize with the occurrence ofmultiple eventsTASKEventsSemaphoreORPOSTPENDTASKISRDISJUNCTIVE SYNCHRONIZATIONTASKEventsSemaphoreANDPOSTPENDTASKISRCONJUNCTIVE SYNCHRONIZATION2-37• Common events can be used to signal multiple tasksTASKISREvents(8, 16 or 32 bits)EventsORPOSTSemaphorePENDTASKEventsANDPOSTSemaphorePENDTASK2-38

Intertask Communication• A task or an ISR to communicate information to anothertask• There are two ways of intertask communication– Through global data (disable/enable interrupts or using semaphore)• Task can only communicate information to an ISR by usingglobal variables• Task can not aware any global variable is changed (unlessusing semaphore or task periodical polling)– Sending messages• Message mailbox or message queue (task can be aware of thedata change)2-39Message MailboxesMailboxTASKPOST PEND10Waiting listTASK• A task desiring a message from an empty mailbox is suspendedand placed on the waiting list until a message is received• Kernel allows the task waiting for a message to specify a timeout• When a message is deposited into the mailbox, how to select atask from the waiting list– Priority based– FIFO2-40

Message queues• Is used to send one or more messages to a task• Is basically an array of mailboxes• The first message inserted in the queue will be the firstmessage extracted from the queue (FIFO) or Last-In_first-Out (LIFO)InterruptQueueISRPOST10PEND0TASK2-41Interrupts• When an interrupt is recognized, the CPU saves– Return address (interrupted task)– Flags• Jump to Interrupt Service Routine (ISR)• Upon completion of the ISR, the program returns to– <strong>Background</strong> for a <strong>Foreground</strong>/background system– The interrupted task for a non-preemptive kernel– The highest priority task ready to run for a preemptive kernelTIMETASKISR #1ISR #2ISR #3Interrupt #1Interrupt #2Interrupt #3Interrupt Nesting2-42

Interrupt latency, Response, and Recovery• The most important specification of a real-time kernel is theamount of time interrupts are disabled– The longer interrupts are disabled , the higher the interrupt latency• Interrupt latency– Maximum amount of time interrupts are disabled + <strong>Time</strong> to startexecuting the first instruction in the ISR• Interrupt response (defined as the time between the reception of theinterrupt and the start of the user code that handles the interrupt)– <strong>Foreground</strong>/background Interrupt latency + <strong>Time</strong> to save the CPU's context– Non-preemptive kernel (don’t need to disable interrupt)– Preemptive kernelInterrupt latency + <strong>Time</strong> to save the CPU's context +Execution time of the kernel ISR entry function• Interrupt recovery (the time required for the processor to return to the interrupted code)– <strong>Foreground</strong>/background <strong>Time</strong> to restore the CPU's context +– Non-preemptive kernel<strong>Time</strong> to execute the return from interrupt instruction– Preemptive kernel<strong>Time</strong> to determine if a higher priority task is ready +<strong>Time</strong> to restore the CPU's context of the highest priority task + 2-43<strong>Time</strong> to execute the return from interrupt instructionFigure 2.20 foreground/backgroundInterrupt RequestTIMEBACKGROUNDBACKGROUNDCPU Context SavedISRUser ISR CodeCPU contextrestoredInterrupt LatencyInterrupt ResponseInterrupt Recovery2-44

Figure 2.21 non-preemptive kernelInterrupt RequestTIMETASKTASKCPU Context SavedISRUser ISR CodeCPU contextrestoredInterrupt LatencyInterrupt ResponseInterrupt Recovery2-45Figure 2.22 preemptive kernelTIMEInterrupt RequestInterrupt RecoveryTASKTASKCPU Context SavedKernel's ISRExit functionAISRKernel's ISREntry functionUser ISR CodeCPU contextrestoredInterrupt LatencyInterrupt ResponseKernel's ISRExit functionCPU contextrestoredBTASKInterrupt Recovery2-46

Nonmaskable Interrupts (NMIs)• NMI cannot be disabled– Interrupt latency, response, and recovery are minimal– Interrupt latency– Interrupt response– Interrupt recovery<strong>Time</strong> to execute longest instruction +<strong>Time</strong> to start executing the NMI ISRInterrupt latency +<strong>Time</strong> to save the CPU's context<strong>Time</strong> to restore the CPU's context +<strong>Time</strong> to execute the return from interrupt instruction• Ex: Used NMI in an application to respond to an interruptoccurred every 150 us. An ISR which will take the processingtime from 80 to 125 us, and the kernel may disable interruptfor about 45 us. Then if we use maskable interrupt , the ISRcould have been late by 20 us.DisableingNonmaskable interruptsNMI Interrupt SourceOutputPortTo Processor's NMI Input2-47• When you are serving an NMI, you cannot use kernelservices to signla a task because NMIs cannot be disabldto access critical sections of code.• You can pass parameters to and from the NMI.– Parameters passed must be global variables and the size of thesevariables must be read or written indivisibly; that is, not as separatebyte read or write instructions.• EX: suppose the NMI service routine needs to signal a taskevery 40 times it executes– If the NMi occurs every 150us, a signal would be required every40 * 150us = 6ms.– From a NMI ISR, you cannot use the kernel to signal the task, butyou can use the following schemeNMI InterruptEvery 150 usIssues interrupt by writingto an output port.NMIISRISRPOSTEvery 150us*40 = 6msSemaphorePENDSignaling a task from a nonmaskable interruptTASK2-48

Clock Tick• A special interrupt that occurs periodically• Allows kernel to delay task for an internal number of clockticks• To provide timeout when task are waiting for event tooccur• The faster the tick rate, the higher the overhead imposed onthe system2-49Figure 2.25 delaying a task for one tick (case 1)Tick Interrupt20 mSTick ISRAll higher priority tasksDelayed TaskCall to delay 1 tick (20 mS)Call to delay 1 tick (20 mS)Call to delay 1 tick (20 mS)t1(19 mS)t2(17 mS)t3(27 mS)Due to the higher priority tasks and the ISRs execute prior to the delayed task, thedelayed task actually executes at varying intervals ( we call this variance is jitter)2-50

Figure 2.26 Delaying a task for one tick (case 2)Tick Interrupt20 mSTick ISRAll higher priority tasksDelayed TaskCall to delay 1 tick (20 mS)Call to delay 1 tick (20 mS)t1t2(6 mS) (19 mS)Call to delay 1 tick (20 mS)t3(27 mS)If the task delays itself just before a clock tick, the task will execute again almostimmediatelyBecause of this, if you need to delay a task at least one clock tick, you must specifyone extra tick.2-51Figure 2.27 delaying a task for one tick (case 3)Tick Interrupt20 mSTick ISRAll higher priority tasksCall to delay 1 tick (20 mS)Call to delay 1 tick (20 mS)Delayed Taskt1(40 mS)t2(26 mS)The task tries to delay for one tick actually executes two ticks later and misses itsdeadline2-52

• Reduce the execution jitter of the task– Increase the clock rate of your microprocessor.– Increase the time between tick interrupts.– Rearrange task priorities.– Avoid using floating-point math (if you must, use single precision).– Get a compiler that performs better code optimization.– Write time-critical code in assembly language.– If possible, upgrade to a faster microprocessor in the same family,e.g., 8086 to 80186, 68000 to 68020, etc.2-53Homework 2• Under 80x86 PC with uCOS-II to design a clock/stopwatchsystem– The clock system and stopwatch system can be operatedconcurrently (i.e., when we are setting the clock time, thestopwatch system also can work normally)HH:MM:SSSS:xxDirection: how to operation the clocksystem and stopwatch system withkeyboard2-54