PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

PIC18F to PIC24F Migration: An Overview - Microchip

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

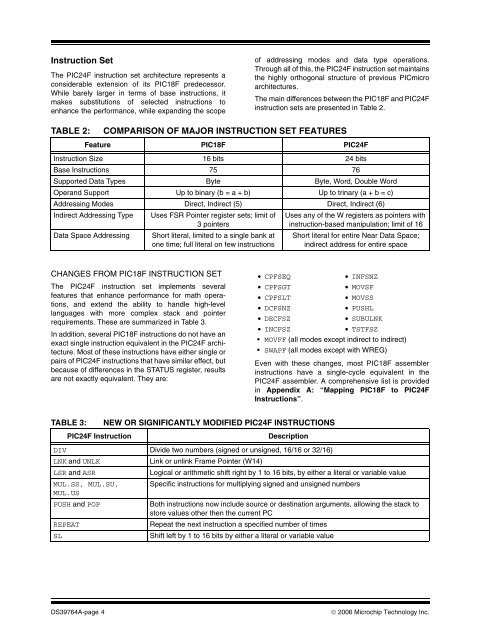

Instruction SetThe <strong>PIC24F</strong> instruction set architecture represents aconsiderable extension of its <strong>PIC18F</strong> predecessor.While barely larger in terms of base instructions, itmakes substitutions of selected instructions <strong>to</strong>enhance the performance, while expanding the scopeof addressing modes and data type operations.Through all of this, the <strong>PIC24F</strong> instruction set maintainsthe highly orthogonal structure of previous PICmicroarchitectures.The main differences between the <strong>PIC18F</strong> and <strong>PIC24F</strong>instruction sets are presented in Table 2.TABLE 2:COMPARISON OF MAJOR INSTRUCTION SET FEATURESFeature <strong>PIC18F</strong> <strong>PIC24F</strong>Instruction Size 16 bits 24 bitsBase Instructions 75 76Supported Data Types Byte Byte, Word, Double WordOperand Support Up <strong>to</strong> binary (b = a + b) Up <strong>to</strong> trinary (a + b = c)Addressing Modes Direct, Indirect (5) Direct, Indirect (6)Indirect Addressing Type Uses FSR Pointer register sets; limit of3 pointersUses any of the W registers as pointers withinstruction-based manipulation; limit of 16Data Space AddressingShort literal, limited <strong>to</strong> a single bank a<strong>to</strong>ne time; full literal on few instructionsShort literal for entire Near Data Space;indirect address for entire spaceCHANGES FROM <strong>PIC18F</strong> INSTRUCTION SETThe <strong>PIC24F</strong> instruction set implements severalfeatures that enhance performance for math operations,and extend the ability <strong>to</strong> handle high-levellanguages with more complex stack and pointerrequirements. These are summarized in Table 3.In addition, several <strong>PIC18F</strong> instructions do not have anexact single instruction equivalent in the <strong>PIC24F</strong> architecture.Most of these instructions have either single orpairs of <strong>PIC24F</strong> instructions that have similar effect, butbecause of differences in the STATUS register, resultsare not exactly equivalent. They are:• CPFSEQ• INFSNZ• CPFSGT• MOVSF• CPFSLT• MOVSS• DCFSNZ• PUSHL• DECFSZ• SUBULNK• INCFSZ• TSTFSZ• MOVFF (all modes except indirect <strong>to</strong> indirect)• SWAPF (all modes except with WREG)Even with these changes, most <strong>PIC18F</strong> assemblerinstructions have a single-cycle equivalent in the<strong>PIC24F</strong> assembler. A comprehensive list is providedin Appendix A: “Mapping <strong>PIC18F</strong> <strong>to</strong> <strong>PIC24F</strong>Instructions”.TABLE 3:NEW OR SIGNIFICANTLY MODIFIED <strong>PIC24F</strong> INSTRUCTIONS<strong>PIC24F</strong> InstructionDescriptionDIV Divide two numbers (signed or unsigned, 16/16 or 32/16)LNK and UNLKLink or unlink Frame Pointer (W14)LSR and ASRLogical or arithmetic shift right by 1 <strong>to</strong> 16 bits, by either a literal or variable valueMUL.SS, MUL.SU, Specific instructions for multiplying signed and unsigned numbersMUL.USPUSH and POPBoth instructions now include source or destination arguments, allowing the stack <strong>to</strong>s<strong>to</strong>re values other then the current PCREPEATRepeat the next instruction a specified number of timesSLShift left by 1 <strong>to</strong> 16 bits by either a literal or variable valueDS39764A-page 4© 2006 <strong>Microchip</strong> Technology Inc.