UDP/IP Stack product brief

UDP/IP Stack product brief

UDP/IP Stack product brief

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

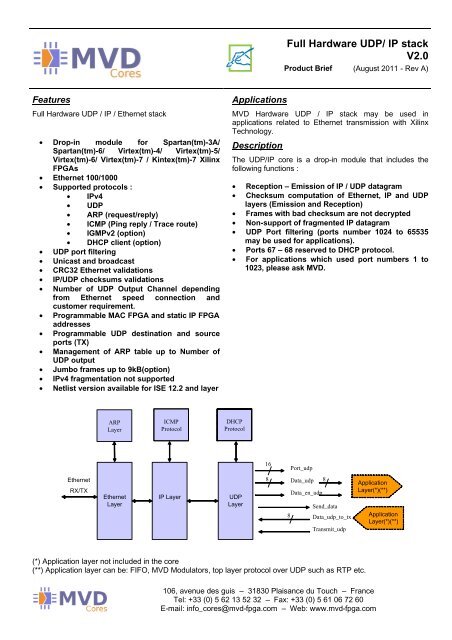

Full Hardware <strong>UDP</strong>/ <strong>IP</strong> stackV2.0Product Brief (August 2011 - Rev A)FeaturesFull Hardware <strong>UDP</strong> / <strong>IP</strong> / Ethernet stack• Drop-in module for Spartan(tm)-3A/Spartan(tm)-6/ Virtex(tm)-4/ Virtex(tm)-5/Virtex(tm)-6/ Virtex(tm)-7 / Kintex(tm)-7 XilinxFPGAs• Ethernet 100/1000• Supported protocols :• <strong>IP</strong>v4• <strong>UDP</strong>• ARP (request/reply)• ICMP (Ping reply / Trace route)• IGMPv2 (option)• DHCP client (option)• <strong>UDP</strong> port filtering• Unicast and broadcast• CRC32 Ethernet validations• <strong>IP</strong>/<strong>UDP</strong> checksums validations• Number of <strong>UDP</strong> Output Channel dependingfrom Ethernet speed connection andcustomer requirement.• Programmable MAC FPGA and static <strong>IP</strong> FPGAaddresses• Programmable <strong>UDP</strong> destination and sourceports (TX)• Management of ARP table up to Number of<strong>UDP</strong> output• Jumbo frames up to 9kB(option)• <strong>IP</strong>v4 fragmentation not supported• Netlist version available for ISE 12.2 and layerApplicationsMVD Hardware <strong>UDP</strong> / <strong>IP</strong> stack may be used inapplications related to Ethernet transmission with XilinxTechnology.DescriptionThe <strong>UDP</strong>/<strong>IP</strong> core is a drop-in module that includes thefollowing functions :• Reception – Emission of <strong>IP</strong> / <strong>UDP</strong> datagram• Checksum computation of Ethernet, <strong>IP</strong> and <strong>UDP</strong>layers (Emission and Reception)• Frames with bad checksum are not decrypted• Non-support of fragmented <strong>IP</strong> datagram• <strong>UDP</strong> Port filtering (ports number 1024 to 65535may be used for applications).• Ports 67 – 68 reserved to DHCP protocol.• For applications which used port numbers 1 to1023, please ask MVD.ARPLayerICMPProtocolDHCPProtocol16Port_udpEthernetRX/TXEthernetLayer<strong>IP</strong> Layer<strong>UDP</strong>Layer8Data_udp 8Data_en_udpSend_data8 Data_udp_to_txTransmit_udpApplicationLayer(*)(**)ApplicationLayer(*)(**)(*) Application layer not included in the core(**) Application layer can be: FIFO, MVD Modulators, top layer protocol over <strong>UDP</strong> such as RTP etc.106, avenue des guis – 31830 Plaisance du Touch – FranceTel: +33 (0) 5 62 13 52 32 – Fax: +33 (0) 5 61 06 72 60E-mail: info_cores@mvd-fpga.com – Web: www.mvd-fpga.com

Resource Utilization (*)Slices BRAMs (18k) (**) MULT BUFGor DSP48Spartan 3 TM 2 800 5 0 3Spartan 6 TM 1 280 5 0 3Virtex 4 TM 2 800 5 0 3Virtex 5 TM 1 500 5 0 3Virtex 6 TM 1 170 5 0 3( These values may vary depending on implementation options)Deliverables :Datasheet and user’s guideNetlist for core generation(*) Values given for Rx_Tx_DHCP version plus one <strong>UDP</strong> output channel.(**) BRAMs to write data in reception or to send data in emission are not take into account.Ordering information and related coresDesignationMVD_<strong>UDP</strong>_<strong>IP</strong>_RX_NETMVD_<strong>UDP</strong>_<strong>IP</strong>_RX_DHCP_NETMVD_<strong>UDP</strong>_<strong>IP</strong>_TX_NETMVD_<strong>UDP</strong>_<strong>IP</strong>_TX_DHCP_NETMVD_<strong>UDP</strong>_<strong>IP</strong>_RX_TX_NETMVD_<strong>UDP</strong>_<strong>IP</strong>_RX_TX_DHCP_NETVersionReceiverReceiver + DHCPTransmitterTransmitter + DHCPReceiver + TransmitterReceiver + Transmitter + DHCPThese cores are all CPU programmable.VHDL source code: Can be delivered as an option under NDA and other specific clauses.Companion cores: Serial Interface for CPU configuration.Related cores: ASI receiver, MVD modulators…Documentation and support: Datasheet and user’s guide. In addition MVD can provide on site or remotecoaching.Please contact us at info_cores@mvd-fpga.com for more information.106, avenue des guis – 31830 Plaisance du Touch – FranceTel: +33 (0) 5 62 13 52 32 – Fax: +33 (0) 5 61 06 72 60E-mail: info_cores@mvd-fpga.com – Web: www.mvd-fpga.com