FDC6320C Dual N & P Channel Digital FET

FDC6320C Dual N & P Channel, Digital FET - Fairchild Semiconductor

FDC6320C Dual N & P Channel, Digital FET - Fairchild Semiconductor

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

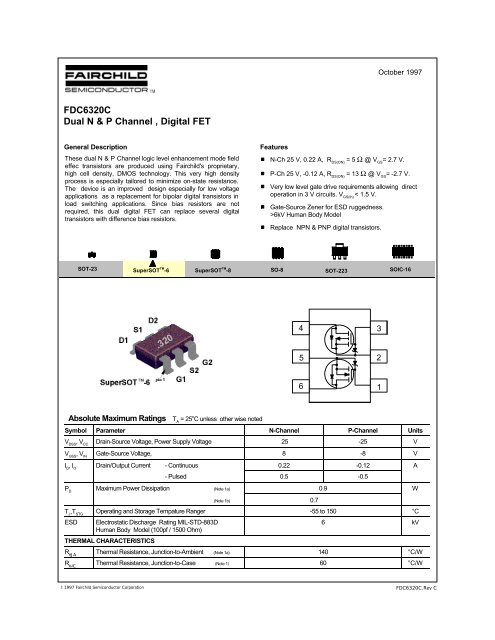

October 1997<br />

<strong>FDC6320C</strong><br />

<strong>Dual</strong> N & P <strong>Channel</strong> , <strong>Digital</strong> <strong>FET</strong><br />

General Description<br />

These dual N & P <strong>Channel</strong> logic level enhancement mode field<br />

effec transistors are produced using Fairchild's proprietary,<br />

high cell density, DMOS technology. This very high density<br />

process is especially tailored to minimize on-state resistance.<br />

The device is an improved design especially for low voltage<br />

applications as a replacement for bipolar digital transistors in<br />

load switching applications. Since bias resistors are not<br />

required, this dual digital <strong>FET</strong> can replace several digital<br />

transistors with difference bias resistors.<br />

Features<br />

N-Ch 25 V, 0.22 A, R DS(ON)<br />

= 5 Ω @ V GS<br />

= 2.7 V.<br />

P-Ch 25 V, -0.12 A, R DS(ON)<br />

= 13 Ω @ V GS<br />

= -2.7 V.<br />

Very low level gate drive requirements allowing direct<br />

operation in 3 V circuits. V GS(th)<br />

< 1.5 V.<br />

Gate-Source Zener for ESD ruggedness.<br />

>6kV Human Body Model<br />

Replace NPN & PNP digital transistors.<br />

SOT-23 SuperSOT TM -6 SuperSOT TM -8 SO-8<br />

SOT-223<br />

SOIC-16<br />

4<br />

3<br />

5<br />

2<br />

6<br />

1<br />

Absolute Maximum Ratings<br />

T A<br />

= 25 o C unless other wise noted<br />

Symbol Parameter N-<strong>Channel</strong> P-<strong>Channel</strong> Units<br />

V DSS<br />

, V CC<br />

Drain-Source Voltage, Power Supply Voltage 25 -25 V<br />

V GSS<br />

, V IN<br />

Gate-Source Voltage, 8 -8 V<br />

I D<br />

, I O<br />

Drain/Output Current - Continuous 0.22 -0.12 A<br />

- Pulsed 0.5 -0.5<br />

P D<br />

Maximum Power Dissipation (Note 1a) 0.9 W<br />

(Note 1b) 0.7<br />

T J<br />

,T STG<br />

Operating and Storage Tempature Ranger -55 to 150 °C<br />

ESD<br />

Electrostatic Discharge Rating MIL-STD-883D<br />

Human Body Model (100pf / 1500 Ohm)<br />

THERMAL CHARACTERISTICS<br />

6 kV<br />

R θJA<br />

Thermal Resistance, Junction-to-Ambient (Note 1a) 140 °C/W<br />

R θJC<br />

Thermal Resistance, Junction-to-Case (Note 1) 60 °C/W<br />

© 1997 Fairchild Semiconductor Corporation<br />

<strong>FDC6320C</strong>.Rev C

DMOS Electrical Characteristics (T A<br />

= 25 O C unless otherwise noted )<br />

Symbol Parameter Conditions Type Min Typ Max Units<br />

OFF CHARACTERISTICS<br />

BV DSS<br />

Drain-Source Breakdown Voltage V GS<br />

= 0 V, I D<br />

= 250 µA N-Ch 25 V<br />

V GS<br />

= 0 V, I D<br />

= -250 µA P-Ch -25<br />

∆BV DSS<br />

/∆T J<br />

Breakdown Voltage Temp. Coefficient I D<br />

= 250 µA, Referenced to 25 o C N-Ch 25 mV / o C<br />

I D<br />

= -250 µA, Referenced to 25 o C P-Ch -20<br />

I DSS<br />

Zero Gate Voltage Drain Current V DS<br />

= 20 V, V GS<br />

= 0 V, N-Ch 1 µA<br />

T J<br />

= 55°C 10<br />

I DSS<br />

Zero Gate Voltage Drain Current V DS<br />

=-20 V, V GS<br />

= 0 V, P-Ch -1 µA<br />

T J<br />

= 55°C -10<br />

I GSS<br />

Gate - Body Leakage Current V GS<br />

= 8 V, V DS<br />

= 0 V N-Ch 100 nA<br />

ON CHARACTERISTICS (Note 2)<br />

V GS<br />

= -8 V, V DS<br />

= 0 V P-Ch -100 nA<br />

∆V GS(th)<br />

/∆T J<br />

Gate Threshold Voltage Temp. Coefficient I D<br />

= 250 µA, Referenced to 25 o C N-Ch -2.1 mV / o C<br />

I D<br />

= -250 µA, Referenced to 25 o C P-Ch 1.9<br />

V GS(th)<br />

Gate Threshold Voltage V DS<br />

= V GS<br />

, I D<br />

= 250 µA N-Ch 0.65 0.85 1.5 V<br />

V DS<br />

= V GS<br />

, I D<br />

= -250 µA P-Ch -0.65 -1 -1.5<br />

R DS(ON)<br />

Static Drain-Source On-Resistance V GS<br />

= 2.7 V, I D<br />

= 0.2 A N-Ch 3.8 5 Ω<br />

T J<br />

=125°C 6.3 9<br />

V GS<br />

= 4.5 V, I D<br />

= 0.4 A 3.1 4<br />

V GS<br />

= -2.7 V, I D<br />

= -0.05 A P-Ch 10.6 13<br />

T J<br />

=125°C 15 21<br />

V GS<br />

= -4.5 V, I D<br />

= -0.2 A 7.9 10<br />

I D(ON)<br />

On-State Drain Current V GS<br />

= 2.7 V, V DS<br />

= 5 V N-Ch 0.2 A<br />

V GS<br />

= -2.7 V, V DS<br />

= -5 V P-Ch -0.05<br />

g FS<br />

Forward Transconductance V DS<br />

= 5 V, I D<br />

= 0.4 A N-Ch 0.2 S<br />

DYNAMIC CHARACTERISTICS<br />

V DS<br />

= -5 V, I D<br />

= -0.2 A P-Ch 0.135<br />

C iss<br />

Input Capacitance N-<strong>Channel</strong><br />

N-Ch 9.5 pF<br />

V DS<br />

= 10 V, V GS<br />

= 0 V,<br />

f = 1.0 MHz<br />

P-Ch 11<br />

C oss<br />

Output Capacitance N-Ch 6 pF<br />

P-<strong>Channel</strong><br />

P-Ch 7<br />

V DS<br />

= -10 V, V GS<br />

= 0 V,<br />

C rss<br />

Reverse Transfer Capacitance f = 1.0 MHz<br />

N-Ch 1.3 pF<br />

P-Ch 1.4<br />

<strong>FDC6320C</strong>.Rev C

DMOS Electrical Characteristics (T A<br />

= 25 O C unless otherwise noted )<br />

Symbol Parameter Conditions Type Min Typ Max Units<br />

SWITCHING CHARACTERISTICS (Note 2)<br />

t D(on)<br />

Turn - On Delay Time N-<strong>Channel</strong> N-Ch 5 11 nS<br />

V DD<br />

= 6 V, I D<br />

= 0.5 A, P-Ch 6 12<br />

t r<br />

Turn - On Rise Time V GS<br />

= 4.5 V, R GEN<br />

= 50 Ω N-Ch 4.5 10 nS<br />

P-Ch 6 12<br />

t D(off)<br />

Turn - Off Delay Time P-<strong>Channel</strong> N-Ch 4 10 nS<br />

V DD<br />

= -6 V, I D<br />

= -0.5 A, P-Ch 7.4 15<br />

t f<br />

Turn - Off Fall Time V GEN<br />

= -4.5 V, R GEN<br />

= 50 Ω N-Ch 3.2 8 nS<br />

P-Ch 4 10<br />

Q g<br />

Total Gate Charge N-<strong>Channel</strong><br />

N-Ch 0.29 0.4 nC<br />

V DS<br />

= 5 V,<br />

I D<br />

= 0.2 A, V GS<br />

= 4.5 V<br />

P-Ch 0.23 0.32<br />

Q gs<br />

Gate-Source Charge N-Ch 0.105 nC<br />

P-<strong>Channel</strong><br />

P-Ch 0.12<br />

V DS<br />

= -5 V,<br />

Q gd<br />

Gate-Drain Charge I D<br />

= -0.2A, V GS<br />

= -4.5 V<br />

N-Ch 0.045 nC<br />

DRAIN-SOURCE DIODE CHARACTERISTICS AND MAXIMUM RATINGS<br />

P-Ch 0.03<br />

I S<br />

Maximum Continuous Drain-Source Diode Forward Current N-Ch 0.5 A<br />

P-Ch -0.5<br />

V SD<br />

Drain-Source Diode Forward Voltage V GS<br />

= 0 V, I S<br />

= 0.5 A (Note 2) N-Ch 0.97 1.3 V<br />

Notes:<br />

V GS<br />

= 0 V, I S<br />

= -0.5 A (Note 2) P-Ch -1 -1.3<br />

1. R θJA<br />

is the sum of the junction-to-case and case-to-ambient thermal resistance where the case thermal reference is defined as the solder mounting surface of the drain pins. R θJC<br />

is guaranteed by<br />

design while R θCA<br />

is determined by the user's board design.<br />

Typical R θJA<br />

using the board layouts shown below on FR-4 PCB in a still air environment:<br />

a. 140 O C/W on a 0.125 in 2 pad of<br />

2oz copper.<br />

b. 180 O C/W on a 0.005 in 2 of pad<br />

of 2oz copper.<br />

Scale 1 : 1 on letter size paper<br />

2. Pulse Test: Pulse Width < 300µs, Duty Cycle < 2.0%.<br />

<strong>FDC6320C</strong>.Rev C

S<br />

D<br />

Typical Electrical Characteristics: N-<strong>Channel</strong><br />

I , DRAIN-SOURCE CURRENT (A)<br />

D<br />

0.5<br />

0.4<br />

0.3<br />

0.2<br />

0.1<br />

V = 4.5V<br />

GS<br />

4.0<br />

3.5<br />

3.0<br />

0<br />

0 0.5 1 1.5 2 2.5 3<br />

V , DRAIN-SOURCE VOLTAGE (V)<br />

DS<br />

2.7<br />

2.5<br />

Figure 1. On-Region Characteristics.<br />

2.0<br />

1.5<br />

R DS(on) , NORMALIZED<br />

DRAIN-SOURCE ON-RESISTANCE<br />

1.4<br />

1.2<br />

1<br />

0.8<br />

V = 2.0V GS<br />

2.5<br />

2.7<br />

0.6<br />

0 0.1 0.2 0.3 0.4 0.5<br />

3.0<br />

3.5<br />

I<br />

D<br />

, DRAIN CURRENT (A)<br />

4.0<br />

4.5<br />

Figure 2. On-Resistance Variation with<br />

Drain Current and Gate Voltage.<br />

R DS(ON) , NORMALIZED<br />

DRAIN-SOURCE ON-RESISTANCE<br />

1.8<br />

1.6<br />

1.4<br />

1.2<br />

1<br />

0.8<br />

I D = 0.2A<br />

V GS = 2.7 V<br />

0.6<br />

-50 -25 0 25 50 75 100 125 150<br />

T , JUNCTION TEMPERATURE (°C)<br />

J<br />

R DS(on) , ON-RESISTANCE (OHM)<br />

15<br />

12<br />

9<br />

6<br />

3<br />

25°C<br />

125°C<br />

0<br />

2 2.5 3 3.5 4<br />

V , GATE TO SOURCE VOLTAGE (V)<br />

GS<br />

I D = 0.2A<br />

Figure 3. On-Resistance Variation<br />

with Temperature.<br />

Figure 4. On Resistance Variation with<br />

Gate-To- Source Voltage.<br />

I , DRAIN CURRENT (A)<br />

0.2<br />

0.15<br />

0.1<br />

0.05<br />

V = 5.0V<br />

DS<br />

T = -55°C<br />

J<br />

25°C<br />

125°C<br />

I , REVERSE DRAIN CURRENT (A)<br />

0.5<br />

0.2<br />

0.1<br />

0.01<br />

0.001<br />

V GS = 0V<br />

T = 125°C J<br />

25°C<br />

-55°C<br />

0<br />

0.5 1 1.5 2 2.5<br />

V , GATE TO SOURCE VOLTAGE (V)<br />

GS<br />

0.0001<br />

0.2 0.4 0.6 0.8 1 1.2<br />

V , BODY DIODE FORWARD VOLTAGE (V)<br />

SD<br />

Figure 5. Transfer Characteristics.<br />

Figure 6. Body Diode Forward Voltage<br />

Variation with Source Current and<br />

Temperature.<br />

<strong>FDC6320C</strong>.Rev C

Typical Electrical Characteristics: N-<strong>Channel</strong> (continued)<br />

CAPACITANCE (pF)<br />

30<br />

20<br />

10<br />

5<br />

3<br />

2<br />

f = 1 MHz<br />

V GS = 0V<br />

1<br />

0.1 0.5 1 2 5 10 25<br />

V , DRAIN TO SOURCE VOLTAGE (V)<br />

DS<br />

C iss<br />

C oss<br />

C rss<br />

V GS , GATE-SOURCE VOLTAGE (V)<br />

5<br />

4<br />

3<br />

2<br />

1<br />

I = 0.2A D V = 5.0V<br />

DS<br />

0<br />

0 0.05 0.1 0.15 0.2 0.25 0.3 0.35<br />

Q<br />

g<br />

, GATE CHARGE (nC)<br />

Figure 7. Capacitance Characteristics.<br />

Figure 8. Gate Charge Characteristics.<br />

I , DRAIN CURRENT (A)<br />

D<br />

0.8<br />

0.5<br />

0.2<br />

0.1<br />

0.05<br />

0.02<br />

RDS(ON) LIMIT<br />

V GS = 2.7V<br />

SINGLE PULSE<br />

R θJA =See note 1b<br />

T A = 25°C<br />

0.01<br />

0.5 1 2 5 10 20 40<br />

DC<br />

1s<br />

100ms<br />

V , DRAI N-SOURCE VOLTAGE (V)<br />

DS<br />

10ms<br />

1ms<br />

POWER (W)<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

0.01 0.1 1 10 100 300<br />

SINGLE PULSE TIME (SEC)<br />

SINGLE PULSE<br />

R θJA =See note 1b<br />

T A = 25°C<br />

Figure 9. Maximum Safe Operating Area.<br />

Figure 10. Single Pulse Maximum Power<br />

Dissipation.<br />

<strong>FDC6320C</strong>.Rev C

S<br />

D<br />

Typical Electrical Characteristics: P-<strong>Channel</strong><br />

-I , DRAIN-SOURCE CURRENT (A)<br />

D<br />

0.2<br />

0.15<br />

0.1<br />

0.05<br />

V GS = -5.0V<br />

-4.5<br />

-4.0<br />

-3.5<br />

-3.0<br />

-2.7<br />

-2.5<br />

0<br />

0 1 2 3 4<br />

-V DS , DRAIN-SOURCE VOLTAGE (V)<br />

Figure 11. On-Region Characteristics.<br />

-2.0<br />

R<br />

DS(ON)<br />

, NORMALIZED<br />

DRAIN-SOURCE ON-RESISTANCE<br />

2<br />

1.5<br />

1<br />

V GS= -2.0 V<br />

-2.5<br />

-2.7<br />

-3.0<br />

0.5<br />

0 0.05 0.1 0.15 0.2<br />

-I D , DRAIN CURRENT (A)<br />

-4.0<br />

-3.5<br />

-4.5<br />

Figure 12. On-Resistance Variation with<br />

Drain Current and Gate Voltage.<br />

1.6<br />

25<br />

R DS(ON) , NORMALIZED<br />

DRAIN-SOURCE ON-RESISTANCE<br />

1.4<br />

1.2<br />

1<br />

0.8<br />

I D = -0.05A<br />

V GS = -2.7V<br />

,DRAIN-SOURCE ON-RESISTANCE<br />

20<br />

15<br />

10<br />

5<br />

T = 25°C<br />

A<br />

125 °C<br />

I D = -0.05A<br />

0.6<br />

-50 -25 0 25 50 75 100 125 150<br />

T , JUNCTION TEMPERATURE (°C)<br />

J<br />

R DS(ON)<br />

0<br />

0 1 2 3 4 5 6 7 8<br />

-V GS ,GATE TO SOURCE VOLTAGE (V)<br />

Figure 13. On-Resistance Variation<br />

with Temperature.<br />

Figure 14. On Resistance Variation with<br />

Gate-To- Source Voltage.<br />

I , DRAIN CURRENT (A)<br />

-1<br />

-0.75<br />

-0.5<br />

-0.25<br />

V = -5V DS<br />

T = -55°C<br />

J<br />

25°C<br />

125°C<br />

-I , REVERSE DRAIN CURRENT (A)<br />

0.5<br />

0.1<br />

0.01<br />

V GS = 0V<br />

T = 125°C J<br />

25°C<br />

-55°C<br />

0<br />

-0.5<br />

-1<br />

-1.5<br />

-2<br />

-2.5<br />

V , GATE TO SOURCE VOLTAGE (V)<br />

GS<br />

-3<br />

0.0001<br />

0 0.2 0.4 0.6 0.8 1 1.2<br />

-V , BODY DIODE FORWARD VOLTAGE (V)<br />

SD<br />

Figure 15. Transfer Characteristics.<br />

Figure 16. Body Diode Forward Voltage<br />

Variation with Source Current and<br />

Temperature.<br />

<strong>FDC6320C</strong>.Rev C

Typical Electrical Characteristics: P-<strong>Channel</strong> (continued)<br />

-V GS , GATE-SOURCE VOLTAGE (V)<br />

8<br />

6<br />

4<br />

2<br />

I D = -0.2A<br />

V = -5V DS<br />

0<br />

0 0.1 0.2 0.3 0.4 0.5<br />

Q g , GATE CHARGE (nC)<br />

-15<br />

-10<br />

-I , DRAIN CURRENT (A)<br />

D<br />

0.8<br />

0.5<br />

0.2<br />

0.1<br />

RDS(ON) LIMIT<br />

0.05<br />

V GS = -2.7V<br />

SINGLE PULSE<br />

0.02 R θJA=See Note 1b<br />

T A= 25°C<br />

0.01<br />

1 2 5 10 20 40<br />

DC<br />

1s<br />

100ms<br />

- V , DRAIN-SOURCE VOLTAGE (V)<br />

DS<br />

1ms<br />

10ms<br />

Figure 17. Gate Charge Characteristics.<br />

Figure 18. Maximum Safe Operating Area.<br />

CAPACITANCE (pF)<br />

25<br />

15<br />

10<br />

5<br />

3<br />

2<br />

f = 1 MHz<br />

V GS = 0 V<br />

1<br />

0.1 0.3 1 2 5 10 15 25<br />

-V<br />

DS<br />

, DRAIN TO SOURCE VOLTAGE (V)<br />

C iss<br />

C oss<br />

C rss<br />

POWER (W)<br />

5<br />

4<br />

3<br />

2<br />

1<br />

0<br />

0.01 0.1 1 10 100 300<br />

SINGLE PULSE TIME (SEC)<br />

SINGLE PULSE<br />

R θJA =See note 1b<br />

T A = 25°C<br />

Figure 19. Capacitance Characteristics.<br />

Figure 20. Single Pulse Maximum Power<br />

Dissipation.<br />

r(t), NORMALIZED EFFECTIVE<br />

TRANSIENT THERMAL RESISTANCE<br />

1<br />

0.5<br />

0.2<br />

0.1<br />

0.05<br />

0.02<br />

D = 0.5<br />

0.2<br />

0.1<br />

0.05<br />

0.02<br />

0.01<br />

Single Pulse<br />

0.01<br />

0.0001 0.001 0.01 0.1 1 10 100 300<br />

t 1, TIME (sec)<br />

P(pk)<br />

R θJA (t) = r(t) * R θJA<br />

R = See Note 1b<br />

θJA<br />

t 1 t 2<br />

T J - T = P * R (t)<br />

A θJA<br />

Duty Cycle, D = t 1/ t 2<br />

Figure 21. Transient Thermal Response Curve.<br />

Note: Thermal characterization performed using the conditions described in note 1b.Transient thermal<br />

response will change depending on the circuit board design.<br />

<strong>FDC6320C</strong>.Rev C

TRADEMARKS<br />

The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is<br />

not intended to be an exhaustive list of all such trademarks.<br />

ACEx<br />

Bottomless<br />

Cool<strong>FET</strong><br />

CROSSVOLT<br />

DenseTrench<br />

DOME<br />

EcoSPARK<br />

E 2 CMOS TM<br />

EnSigna TM<br />

FACT<br />

FACT Quiet Series<br />

STAR*POWER is used under license<br />

DISCLAIMER<br />

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER<br />

NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD<br />

DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT<br />

OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT<br />

RIGHTS, NOR THE RIGHTS OF OTHERS.<br />

LIFE SUPPORT POLICY<br />

FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT<br />

DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.<br />

As used herein:<br />

1. Life support devices or systems are devices or<br />

systems which, (a) are intended for surgical implant into<br />

the body, or (b) support or sustain life, or (c) whose<br />

failure to perform when properly used in accordance<br />

with instructions for use provided in the labeling, can be<br />

reasonably expected to result in significant injury to the<br />

user.<br />

PRODUCT STATUS DEFINITIONS<br />

Definition of Terms<br />

®<br />

FAST<br />

FASTr<br />

FR<strong>FET</strong><br />

GlobalOptoisolator<br />

GTO<br />

HiSeC<br />

ISOPLANAR<br />

Little<strong>FET</strong><br />

Micro<strong>FET</strong><br />

MicroPak<br />

MICROWIRE<br />

OPTOLOGIC<br />

OPTOPLANAR<br />

PACMAN<br />

POP<br />

Power247<br />

PowerTrench ®<br />

Q<strong>FET</strong><br />

QS<br />

QT Optoelectronics<br />

Quiet Series<br />

SILENT SWITCHER<br />

®<br />

SMART START<br />

STAR*POWER<br />

Stealth<br />

SuperSOT-3<br />

SuperSOT-6<br />

SuperSOT-8<br />

Sync<strong>FET</strong><br />

TinyLogic<br />

TruTranslation<br />

UHC<br />

Ultra<strong>FET</strong><br />

®<br />

2. A critical component is any component of a life<br />

support device or system whose failure to perform can<br />

be reasonably expected to cause the failure of the life<br />

support device or system, or to affect its safety or<br />

effectiveness.<br />

Datasheet Identification Product Status Definition<br />

VCX<br />

Advance Information<br />

Preliminary<br />

No Identification Needed<br />

Formative or<br />

In Design<br />

First Production<br />

Full Production<br />

This datasheet contains the design specifications for<br />

product development. Specifications may change in<br />

any manner without notice.<br />

This datasheet contains preliminary data, and<br />

supplementary data will be published at a later date.<br />

Fairchild Semiconductor reserves the right to make<br />

changes at any time without notice in order to improve<br />

design.<br />

This datasheet contains final specifications. Fairchild<br />

Semiconductor reserves the right to make changes at<br />

any time without notice in order to improve design.<br />

Obsolete<br />

Not In Production<br />

This datasheet contains specifications on a product<br />

that has been discontinued by Fairchild semiconductor.<br />

The datasheet is printed for reference information only.<br />

Rev. H4