Annual report 2000 - Europractice

Annual report 2000 - Europractice

Annual report 2000 - Europractice

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Low cost IC prototyping<br />

The cost of producing a new ASIC<br />

for a dedicated application within a<br />

small market can be high, if directly<br />

produced by a commercial foundry.<br />

This is largely due to the<br />

4<br />

NRE (Non-Recurring Engineering)<br />

overheads associated with design,<br />

manufacturing and test.<br />

EUROPRACTICE has reduced the<br />

NRE, especially for ASIC prototyping,<br />

by two techniques:<br />

(i) Multi Project Wafer Runs or<br />

(ii) Multi Level Masks.<br />

Multi Project Wafer Runs<br />

By combining several designs from<br />

different customers onto one mask<br />

set and prototype run, known as<br />

Multi Project Wafer (MPW) runs,<br />

the high NRE costs of a mask set is<br />

shared among the participating<br />

customers.<br />

Fabrication of prototypes can thus<br />

be as low as 5% to 10% of the cost<br />

of a full prototyping wafer run. A<br />

limited number of tested or untested<br />

ASIC prototypes, typically<br />

10-20, are delivered to the customer<br />

for evaluation, either as<br />

naked dies or as encapsulated devices.<br />

Only prototypes from fully<br />

qualified wafers are taken to ensure<br />

that the chips delivered<br />

will function “right first<br />

time”.<br />

In order to achieve<br />

this, extensive Design<br />

Rule and Electrical<br />

Rule Checkings<br />

are performed<br />

on all designs submitted<br />

to the Service.<br />

EUROPRACTICE is<br />

organising about 130 MPW runs<br />

per year in various technologies.<br />

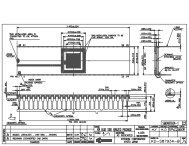

Multi Level Mask<br />

Single User Runs<br />

Another technique to reduce the<br />

high mask costs is called Multi<br />

Level Mask (MLM). With this<br />

technique the available mask area<br />

(20 mm x 20 mm field) is typically<br />

divided in four quadrants (4L/R :<br />

four layer per reticle) whereby<br />

each quadrant is filled with one design<br />

layer. As an example : one<br />

mask can contain four layers such<br />

as nwell, poly, ndiff and active. The<br />

total number of masks is thus reduced<br />

by a factor of four. By adapting<br />

the lithographical procedure it<br />

is possible to use one mask four<br />

times for the different layers by<br />

using the appropriate quadrants.<br />

Using this technique the mask<br />

costs can be reduced by about<br />

60%.<br />

The advantages of using MLM single<br />

user runs are : (i) lower mask<br />

costs, (ii) can be started any date<br />

and not restricted to scheduled<br />

MPW runs, (iii) single user and<br />

(iv) customer receives minimal a<br />

few wafers, so a few hundreds of<br />

prototypes.<br />

This technique is preferred over<br />

MPW runs when the chip area becomes<br />

large and when the customer<br />

wants to get a higher number<br />

of prototypes or preserie.<br />

When the prototypes are successful,<br />

this mask set can be used