Simulação de Circuitos e Dispositivos Programáveis - PCS - USP

Simulação de Circuitos e Dispositivos Programáveis - PCS - USP

Simulação de Circuitos e Dispositivos Programáveis - PCS - USP

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital<br />

SIMULAÇÃO DE CIRCUITOS E<br />

DISPOSITIVOS PROGRAMÁVEIS<br />

Edson T. Midorikawa / 2007<br />

E.T.M./2011<br />

RESUMO<br />

Nesta experiência será discutido o procedimento <strong>de</strong> simulação <strong>de</strong> circuitos digitais, em particular sua<br />

importância <strong>de</strong>ntro <strong>de</strong> uma metodologia para projeto <strong>de</strong> sistemas digitais. Serão abordados também<br />

princípios <strong>de</strong> dispositivos programáveis, como as CPLDs e FPGAs. A parte experimental consiste na<br />

aplicação <strong>de</strong> técnicas <strong>de</strong> simulação em alguns circuitos com o auxílio da ferramenta <strong>de</strong> software para<br />

projeto <strong>de</strong> sistemas digitais Quartus II da Altera e a programação <strong>de</strong> projetos em dispositivos<br />

programáveis.<br />

O objetivo principal <strong>de</strong>sta experiência é a familiarização com os procedimentos <strong>de</strong> simulação com uma<br />

ferramenta <strong>de</strong> software e uma breve introdução aos dispositivos programáveis.<br />

1. PARTE TEÓRICA<br />

1.1. Metodologia <strong>de</strong> Projeto <strong>de</strong> Sistemas Digitais<br />

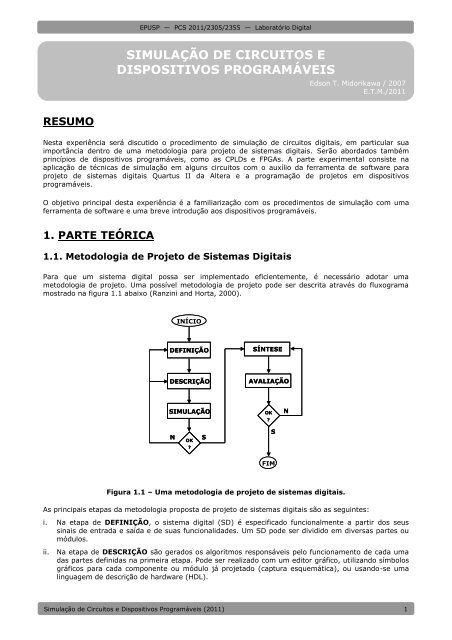

Para que um sistema digital possa ser implementado eficientemente, é necessário adotar uma<br />

metodologia <strong>de</strong> projeto. Uma possível metodologia <strong>de</strong> projeto po<strong>de</strong> ser <strong>de</strong>scrita através do fluxograma<br />

mostrado na figura 1.1 abaixo (Ranzini and Horta, 2000).<br />

INÍCIO<br />

DEFINIÇÃO<br />

SÍNTESE<br />

DESCRIÇÃO<br />

AVALIAÇÃO<br />

SIMULAÇÃO<br />

OK<br />

?<br />

N<br />

N<br />

OK<br />

?<br />

S<br />

S<br />

FIM<br />

Figura 1.1 – Uma metodologia <strong>de</strong> projeto <strong>de</strong> sistemas digitais.<br />

As principais etapas da metodologia proposta <strong>de</strong> projeto <strong>de</strong> sistemas digitais são as seguintes:<br />

i. Na etapa <strong>de</strong> DEFINIÇÃO, o sistema digital (SD) é especificado funcionalmente a partir dos seus<br />

sinais <strong>de</strong> entrada e saída e <strong>de</strong> suas funcionalida<strong>de</strong>s. Um SD po<strong>de</strong> ser dividido em diversas partes ou<br />

módulos.<br />

ii.<br />

Na etapa <strong>de</strong> DESCRIÇÃO são gerados os algoritmos responsáveis pelo funcionamento <strong>de</strong> cada uma<br />

das partes <strong>de</strong>finidas na primeira etapa. Po<strong>de</strong> ser realizado com um editor gráfico, utilizando símbolos<br />

gráficos para cada componente ou módulo já projetado (captura esquemática), ou usando-se uma<br />

linguagem <strong>de</strong> <strong>de</strong>scrição <strong>de</strong> hardware (HDL).<br />

<strong>Simulação</strong> <strong>de</strong> <strong>Circuitos</strong> e <strong>Dispositivos</strong> <strong>Programáveis</strong> (2011) 1

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital<br />

iii. A etapa seguinte (SIMULAÇÃO) envolve a execução <strong>de</strong> uma simulação do SD, com o objetivo <strong>de</strong><br />

verificar possíveis erros <strong>de</strong> concepção do projeto. Procura-se aqui encontrar erros, e em caso<br />

afirmativo, uma ação corretiva po<strong>de</strong> ser tomada.<br />

iv. Na SÍNTESE, cada um dos módulos do SD é transformado em elementos <strong>de</strong> hardware, para serem<br />

implementados fisicamente.<br />

v. Na AVALIAÇÃO, estes elementos <strong>de</strong> hardware são testados para verificar se a implementação do SD<br />

está funcionando <strong>de</strong> acordo com a especificação do projeto. Caso for encontrada qualquer<br />

discordância, uma nova síntese po<strong>de</strong> ser elaborada.<br />

1.2. <strong>Simulação</strong> <strong>de</strong> <strong>Circuitos</strong> Digitais<br />

O objetivo da simulação é verificar se o projeto do circuito digital, especificado via captura esquemática<br />

ou via linguagem <strong>de</strong> <strong>de</strong>scrição <strong>de</strong> hardware (HDL), executa corretamente <strong>de</strong> acordo com as suas<br />

especificações. Há duas categorias <strong>de</strong> simulação, funcional e temporizada.<br />

A simulação funcional simula a operação do circuito a partir <strong>de</strong> uma perspectiva lógica apenas, sem se<br />

preocupar com os atrasos <strong>de</strong> propagação dos sinais pelos componentes. Todos os dispositivos operam<br />

com tempos <strong>de</strong> atraso, setup e hold iguais a zero. Ela apenas verifica as equações booleanas e o<br />

seqüenciamento da máquina <strong>de</strong> estados. De uma maneira geral, é mais rápida que a simulação<br />

temporizada, permitindo assim encontrar erros <strong>de</strong> projeto mais rapidamente.<br />

A simulação temporizada simula a operação do circuito sob uma perspectiva <strong>de</strong> propagação <strong>de</strong> sinais<br />

pelos componentes. Todos os dispositivos operam com tempos <strong>de</strong> atraso, setup e hold reais. Ou seja,<br />

circuitos logicamente corretos, mas que não obe<strong>de</strong>cem, por exemplo, o tempo <strong>de</strong> setup <strong>de</strong> um dos<br />

componentes po<strong>de</strong> produzir resultados diferentes do esperado. Geralmente, esta simulação usa atrasos<br />

do pior caso (worst-case <strong>de</strong>lays), <strong>de</strong> modo que um circuito real <strong>de</strong>ve operar mais rápido que o simulado.<br />

Ela é usada para verificar problemas <strong>de</strong> temporização, mas po<strong>de</strong> também ser usada para re-verificar as<br />

equações booleanas e o seqüenciamento da máquina <strong>de</strong> estados. Por se tratar <strong>de</strong> um processo mais<br />

<strong>de</strong>morado, é normalmente usado <strong>de</strong>pois <strong>de</strong> uma simulação funcional.<br />

Várias ferramentas dispõem do recurso <strong>de</strong> simulação. O Quartus II 9.1 oferece este recurso com auxílio<br />

do editor <strong>de</strong> formas <strong>de</strong> onda, como ilustrado na figura 1.2 abaixo.<br />

Figura 1.2 - Editor <strong>de</strong> formas <strong>de</strong> onda do Quartus II 9.1.<br />

Detalhes e mais informações sobre a ferramenta <strong>de</strong> simulação disponível no Quartus II 9.1 po<strong>de</strong>m ser<br />

encontrados no documento ―Quartus II Simulation‖ disponível na página da Internet da Altera.<br />

<strong>Simulação</strong> <strong>de</strong> <strong>Circuitos</strong> e <strong>Dispositivos</strong> <strong>Programáveis</strong> (2011) 2

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital<br />

1.3. <strong>Dispositivos</strong> <strong>Programáveis</strong><br />

Os dispositivos lógicos programáveis representam uma nova abordagem no processo <strong>de</strong> <strong>de</strong>senvolvimento<br />

<strong>de</strong> sistemas digitais. No passado, os projetistas tinham <strong>de</strong> usar apenas componentes digitais com<br />

"funções fixas" disponibilizados no mercado (contadores, <strong>de</strong>codificadores, <strong>de</strong>slocadores, etc). Os<br />

dispositivos programáveis permitem ao usuário <strong>de</strong>finir uma função a ser <strong>de</strong>sempenhado por um ou vários<br />

chips. As características mais marcantes <strong>de</strong>stes dispositivos são a programabilida<strong>de</strong> e a alta capacida<strong>de</strong>,<br />

o que aumenta a eficiência e a flexibilida<strong>de</strong> dos projetos e, também, diminui o tempo <strong>de</strong> <strong>de</strong>senvolvimento<br />

do produto. (Dueck, 2001)<br />

Lógica Programável<br />

Os projetistas <strong>de</strong> circuitos digitais têm à sua disposição uma gran<strong>de</strong> varieda<strong>de</strong> <strong>de</strong> CIs padronizados, com<br />

as mais variadas funções. O fato <strong>de</strong>stes CIs serem fabricados por várias empresas e em gran<strong>de</strong> volume<br />

fazem com que tenham um custo relativamente baixo. Por esta razão, a técnica muito comum para a<br />

implementação <strong>de</strong> projetos <strong>de</strong> sistemas digitais é a interconexão <strong>de</strong>stes CIs padronizados. (Tocci, 2007)<br />

Apesar <strong>de</strong> ser amplamente empregada, a utilização <strong>de</strong> CIs padronizados na implementação <strong>de</strong> sistemas<br />

tem alguns problemas. Primeiro, alguns sistemas po<strong>de</strong>m precisar <strong>de</strong> centenas ou milhares <strong>de</strong> CIs. Este<br />

gran<strong>de</strong> número <strong>de</strong> CIs necessita <strong>de</strong> um espaço consi<strong>de</strong>rável em uma placa <strong>de</strong> circuito impresso, sem<br />

levar em conta o consumo <strong>de</strong> energia necessária para alimentá-las. Um segundo aspecto diz respeito<br />

com o tempo necessário para a montagem e testes das placas.Uma gran<strong>de</strong> quantida<strong>de</strong> <strong>de</strong> CIs<br />

necessários em um sistema resultam em um tempo maior para colocar e soldar estes componentes na <strong>de</strong><br />

circuito impresso. E a manutenção é o terceiro aspecto. Quanto maior o número <strong>de</strong> componentes, menor<br />

é a confiabilida<strong>de</strong> do sistema. Assim, o fabricante do equipamento <strong>de</strong>ve manter um estoque consi<strong>de</strong>rável,<br />

dispondo <strong>de</strong> toda a varieda<strong>de</strong> <strong>de</strong> CIs utilizados no circuito.<br />

Uma solução para estas questões é reduzir o número <strong>de</strong> CIs usados no projeto. Com isto teremos uma<br />

série <strong>de</strong> vantagens: um menor espaço na placa, um menor consumo <strong>de</strong> energia (fontes <strong>de</strong> alimentação<br />

menores), processos <strong>de</strong> fabricação mais rápidos e baratos, maior confiabilida<strong>de</strong> e uma manutenção mais<br />

fácil.<br />

Para reduzir o número <strong>de</strong> CIs a serem usados no projeto é necessário colocar mais e mais funções nos<br />

chips. É claro que isso tem sido feito com as tecnologias LSI, VLSI, ULSI e, mais recentemente, GSI ,<br />

para funções padronizadas como memórias, microprocessadores, sintetizadores <strong>de</strong> voz, entre outros.<br />

Esses dispostivos contêm milhares a alguns milhões <strong>de</strong> portas lógicas conectadas para operar <strong>de</strong> um<br />

modo pré-<strong>de</strong>terminado. Existem muitas situações para as quais não existem soluções LSI, VLSI, ULSI e<br />

GSI. Nesses casos, o projetista se vê obrigado a recorrer aos dispositivos SSI e MSI padrões para obter<br />

as funções necessárias.<br />

O recente <strong>de</strong>senvolvimento <strong>de</strong> uma nova categoria <strong>de</strong> dispositivos, conhecidos como dispositivos lógicos<br />

programáveis (PLD), ofereceu aos projetistas uma alternativa para substituir um gran<strong>de</strong> número <strong>de</strong> CIs<br />

padronizados por um único CI. Esses dispositivos permitem especificar a sua operação lógica através <strong>de</strong><br />

um processo chamado ―programação‖ (Tocci, 2007).<br />

Tipos <strong>de</strong> <strong>Dispositivos</strong> Lógicos <strong>Programáveis</strong><br />

Uma gran<strong>de</strong> varieda<strong>de</strong> <strong>de</strong> dispositivos programáveis foi <strong>de</strong>senvolvida nos últimos tempos. Po<strong>de</strong>mos citar,<br />

por exemplo, os seguintes: (Tocci, 2007), (Wakerly, 2006), (Fregni e Saraiva, 1995)<br />

<br />

<br />

<br />

<br />

<br />

PROM (Programmable Read-Only Memory) – precursor dos PLDs, a PROM po<strong>de</strong> gerar qualquer<br />

função lógica possível das variáveis <strong>de</strong> entrada. Contudo é usada apenas para um pequeno<br />

número <strong>de</strong> variáveis <strong>de</strong> entrada;<br />

PLA (Programmable Logic Array) – <strong>de</strong>senvolvido em meados da década <strong>de</strong> 70, foi o primeiro<br />

dispositivo programável sem a estrutura interna da PROM, pois tanto a matriz das portas AND<br />

como a matriz das portas OR po<strong>de</strong>m ser programadas. Não teve boa aceitação por parte dos<br />

projetistas;<br />

PAL (Programmable Array Logic) – contém uma arquitetura interna similar a da PROM, sendo<br />

uma simplificação da PLA, pois apenas as conexões das entradas da matriz das portas AND são<br />

programáveis (a matriz das portas OR é fixa). É há muito tempo o tipo <strong>de</strong> dispositivo<br />

programável mais utilizado;<br />

GAL (Generic Array Logic) – tipo <strong>de</strong> dispositivo programável que permite a implementação <strong>de</strong><br />

circuitos sequenciais, pois introduz a possibilida<strong>de</strong> <strong>de</strong> emular flip-flops;<br />

CPLD (Complex Programmable Logic Device) – combina vários dispositivos do tipo PAL em uma<br />

estrutura em forma <strong>de</strong> matriz. Os blocos lógicos têm conexões AND programáveis e conexões OR<br />

fixas. Quando necessário, vários blocos lógicos po<strong>de</strong>m ser combinados para implementar;<br />

<strong>Simulação</strong> <strong>de</strong> <strong>Circuitos</strong> e <strong>Dispositivos</strong> <strong>Programáveis</strong> (2011) 3

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital<br />

<br />

FPGA (Field Programmable Gate Array) – contém um gran<strong>de</strong> número <strong>de</strong> blocos lógicos que<br />

po<strong>de</strong>m ser programados in<strong>de</strong>pen<strong>de</strong>ntemente. Esses blocos contêm lógica combinatória e<br />

registradores para circuitos sequenciais;<br />

A Altera produz a famíla <strong>de</strong> CPLDs MAX7000S, cujo diagrama <strong>de</strong> blocos é apresentado na figura 1.3. A<br />

principal estrutura do MAX7000S é uma série <strong>de</strong> Blocos <strong>de</strong> Matriz Lógica (LABs - logic array blocks),<br />

interconectados entre si por uma Matriz <strong>de</strong> Interconexão Programável (PIA - programmable interconnect<br />

array). Cada LAB é, na realida<strong>de</strong>, composto por um grupo <strong>de</strong> 16 macrocélulas, que po<strong>de</strong>m compartilhar<br />

os termos-produto das suas variáveis. (Duech, 2001)<br />

O CPLD EPM7128S84 é um membro da família da Altera e sua i<strong>de</strong>ntificação tem o seguinte significado:<br />

EPM7 família MAX7000<br />

128 número <strong>de</strong> macrocélulas<br />

S programação "in-circuit" (quando instalado na placa do circuito)<br />

LC84 empacotamento PLCC <strong>de</strong> 84 pinos<br />

O EPM7128SLC84 contém 2.500 portas utilizáveis, 128 macrocélulas, 8 LABs, 8 pinos <strong>de</strong> I/O por LAB<br />

(totalizando 64 pinos <strong>de</strong> I/O).<br />

Na prática o EPM7128SLC84 <strong>de</strong>ve ser programado na própria placa <strong>de</strong> circuito, através <strong>de</strong> quatro pinos<br />

<strong>de</strong>dicados para a interface <strong>de</strong> programação. As macrocélulas que não forem conectados a um pino <strong>de</strong> I/O<br />

<strong>de</strong> usuário apenas po<strong>de</strong>rão ser usadas como um módulo <strong>de</strong> lógica interna da PLD. Uma macrocélula é<br />

similar a um GAL, pois ela fornece uma função <strong>de</strong> soma <strong>de</strong> produtos como sinal <strong>de</strong> saída.<br />

Figura 1.3 - Diagrama <strong>de</strong> Blocos do CPLD MAX7000S da Altera.<br />

<strong>Simulação</strong> <strong>de</strong> <strong>Circuitos</strong> e <strong>Dispositivos</strong> <strong>Programáveis</strong> (2011) 4

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital<br />

2. PARTE EXPERIMENTAL<br />

2.1. Ativida<strong>de</strong>s Pré-Laboratório<br />

Nesta experiência será usado o software Quartus II da Altera para a simulação dos circuitos abaixo.<br />

Consulte as seções relevantes da apostila "Quartus II Simulation Using VHDL Designs" (disponível na<br />

página Internet do curso ou da Altera) para instruções <strong>de</strong> uso do programa (criação <strong>de</strong> um projeto <strong>de</strong><br />

circuito, compilação, simulação e programação).<br />

Circuito Assíncrono<br />

a) Seja o circuito da figura 2.1 abaixo. Analise sua estrutura e i<strong>de</strong>ntifique seus componentes e sinais.<br />

D<br />

C K<br />

1<br />

Q<br />

Q<br />

Q 1<br />

D<br />

Q<br />

D<br />

2 3<br />

C K<br />

Q<br />

C K<br />

Q 2<br />

Q<br />

Q<br />

Q 3<br />

A<br />

D<br />

C K<br />

4<br />

Q<br />

Q<br />

Q 4<br />

Figura 2.1 - Circuito a ser simulado.<br />

b) Desenhe este circuito no Quartus II usando o editor gráfico (captura esquemática), não se<br />

esquecendo <strong>de</strong> criar um projeto 1 para ele. Especifique os sinais Q1, Q2, Q3, Q4 e A como sinais <strong>de</strong><br />

saída para po<strong>de</strong>rem ser analisados na simulação. Em seguida, salve, compile o projeto e verifique a<br />

presença <strong>de</strong> erros.<br />

<strong>Simulação</strong> funcional<br />

c) Simule o comportamento funcional do circuito, conforme <strong>de</strong>scrito na apostila "Quartus II Simulation<br />

Using VHDL Designs" (seção 5.1). Imprima as formas <strong>de</strong> onda obtidas para ser anexada no relatório.<br />

d) Explique as formas <strong>de</strong> onda obtidas a partir da simulação funcional.<br />

<strong>Simulação</strong> temporizada<br />

e) Execute em seguida uma simulação temporizada do circuito, conforme <strong>de</strong>scrito na seção 5.2 do<br />

documento "Quartus II Simulation Using VHDL Designs". Anexe também as formas <strong>de</strong> onda obtidas.<br />

f) Analise as formas <strong>de</strong> onda obtidas a partir da simulação temporizada.<br />

Comparação e análise das simulações<br />

g) Compare as formas <strong>de</strong> onda analisadas nos itens (d) e (f). Qual a conclusão <strong>de</strong>sta comparação?<br />

h) Qual foi a influência dos atrasos nos componentes na diferença nas formas <strong>de</strong> onda do sinal Q4 dos<br />

itens (c) e (e)? Explique.<br />

i) Repita a simulação temporizada para um "grid size" maior (por exemplo, 1 ms) 2 . Houve alguma<br />

mudança nas formas <strong>de</strong> onda? Analise.<br />

1 Durante a criação do projeto, especifique o dispositivo programável correto: família MAX7000S e componente<br />

EPM7128SLC84-7 ou -15, conforme disponível no painel <strong>de</strong> montagens da bancada.<br />

2 Não esqueça também <strong>de</strong> alterar o valor do parâmetro ―end time‖, que especifica o tempo <strong>de</strong> fim <strong>de</strong> simulação (por<br />

exemplo, 1 seg).<br />

<strong>Simulação</strong> <strong>de</strong> <strong>Circuitos</strong> e <strong>Dispositivos</strong> <strong>Programáveis</strong> (2011) 5

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital<br />

2.2. Montagem Experimental do Circuito<br />

j) Execute uma montagem do circuito lógico da figura 2.1 no painel <strong>de</strong> montagens experimentais.<br />

Anexe um diagrama lógico.<br />

k) Analise as formas <strong>de</strong> onda dos sinais Q1, Q2, Q3, Q4 e A, monitoradas com auxilio <strong>de</strong> um<br />

osciloscópio. Anexe uma cópia das formas <strong>de</strong> onda.<br />

l) Compare as formas <strong>de</strong> onda obtidas experimentalmente com as simulações da seção 2.1. Analise.<br />

2.3. Programação <strong>de</strong> Dispositivo Programável<br />

m) Com o projeto do circuito da figura 2.1 disponível no Quartus II, realize a programação do circuito no<br />

dispositivo programável da placa MAX7-<strong>PCS</strong> disponível no painel <strong>de</strong> montagens experimentais. Use o<br />

documento ―Quartus II Introduction Using Schematic Design‖ (seção 9.1) para auxiliá-los neste item.<br />

n) Teste o funcionamento do circuito na placa MAX7-<strong>PCS</strong> monitorando os sinais <strong>de</strong> saída no osciloscópio.<br />

o) Compare as formas <strong>de</strong> onda obtidas experimentalmente com as simulações da seção 2.1 e a<br />

montagem da seção 2.2. Comente eventuais acontecimentos no uso do Quartus II e na montagem<br />

experimental.<br />

2.4. Perguntas<br />

p) Qual é o papel da simulação no processo <strong>de</strong> <strong>de</strong>senvolvimento <strong>de</strong> circuitos digitais? Escreva com suas<br />

próprias palavras.<br />

q) Quais as vantagens do uso <strong>de</strong> ferramentas <strong>de</strong> simulação no processo <strong>de</strong> <strong>de</strong>senvolvimento <strong>de</strong> circuitos<br />

digitais?<br />

r) Exemplifique outros usos possíveis da simulação.<br />

s) Como o uso <strong>de</strong> dispositivos lógicos programáveis facilita o projeto <strong>de</strong> circuitos digitais?<br />

3. BIBLIOGRAFIA<br />

ALTERA. Quartus II Simulation Using VHDL Designs. July, 2010.<br />

ALTERA. Quartus II Introduction Using Schematic Design. September, 2010.<br />

DUECK, R. K. Digital Design with CPLD Applications and VHDL. Delmar, 2001.<br />

<br />

<br />

<br />

<br />

<br />

<br />

FREGNI, E. & SARAIVA, A. M. Engenharia do Projeto Lógico Digital: conceitos e prática. Edgard<br />

Blücher, 1995.<br />

KIME, C. R.; MANO, M. M. Logic and computer <strong>de</strong>sign fundamentals. 3 rd ed., New Jersey:<br />

Prentice Hall, 2004.<br />

MIDORIKAWA, E. T., et al. Projeto <strong>de</strong> circuitos com MAX+PLUS II. Apostila <strong>de</strong> Laboratório<br />

Digital. Escola Politécnica da <strong>USP</strong>, 2002.<br />

ORDONEZ, E.D.M.; PEREIRA, F.D.; PENTEADO, G.; PERICINI, R.A. Projeto, Desempenho e<br />

Aplicações <strong>de</strong> Sistemas Digitais em <strong>Circuitos</strong> <strong>Programáveis</strong> (FPGAs). Bless Gráfica e Editora<br />

Ltda., 2003.<br />

RANZINI, E.; HORTA, E. L. Lógica programável. Apostila <strong>de</strong> Laboratório Digital. Escola Politécnica<br />

da <strong>USP</strong>, 2000.<br />

TOCCI, R. J.; WIDMER, N. S.; MOSS, G. L. Digital Systems: principles and applications.<br />

10 th ed., Prentice-Hall, 2007.<br />

WAKERLY, J. F. Digital <strong>de</strong>sign: principles and practice. 4 th ed., New Jersey: Prentice- Hall, 2006.<br />

<strong>Simulação</strong> <strong>de</strong> <strong>Circuitos</strong> e <strong>Dispositivos</strong> <strong>Programáveis</strong> (2011) 6

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital<br />

4. MATERIAL DISPONÍVEL<br />

<strong>Circuitos</strong> Integrados TTL: 7400, 7410, 7474.<br />

5. RECURSOS NECESSÁRIOS<br />

1 painel <strong>de</strong> montagens experimentais.<br />

1 fonte <strong>de</strong> alimentação fixa, 5V 5%, 4A.<br />

1 placa MAX7-<strong>PCS</strong>, com cabo para interface paralela.<br />

1 computador tipo IBM-PC com software Quartus II.<br />

1 impressora.<br />

<strong>Simulação</strong> <strong>de</strong> <strong>Circuitos</strong> e <strong>Dispositivos</strong> <strong>Programáveis</strong> (2011) 7