1. Prelazak sa RISC na CISC koncept

1. Prelazak sa RISC na CISC koncept

1. Prelazak sa RISC na CISC koncept

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>1.</strong> <strong>Prelazak</strong> <strong>sa</strong> <strong>RISC</strong> <strong>na</strong> <strong>CISC</strong> <strong>koncept</strong><br />

Zadnjih 25 godi<strong>na</strong> prelazak <strong>sa</strong> <strong>CISC</strong> <strong>na</strong> <strong>RISC</strong> <strong>koncept</strong> doveo je do radikalnih prome<strong>na</strong><br />

kod ISA (Instruction Set Architecture). U cilju boljeg <strong>sa</strong>gledavanja ove problematike u daljem<br />

tekstu ukazaćemo <strong>na</strong> ključne razlike izmedju ove dve arhitekture.<br />

Kao što smo ranije ukazali ISA raču<strong>na</strong>r specificira primitivne komande koje se direktno<br />

izvršavaju od strane hardvera. Drugim rečima, ISA specificira izvršive mašinske instrukcije<br />

za dati tip procesora. Kompleksnost ISA zavisi od formata instrukcija, formata podataka,<br />

adresnih <strong>na</strong>či<strong>na</strong> rada, registara opšte <strong>na</strong>mene, specifikacije opkoda, i mehanizmima za<br />

upravljanje tokom izvr{enja programa. U zavisnosti od različitih izbora koji se tiču ovih<br />

osobi<strong>na</strong>, <strong>RISC</strong> i <strong>CISC</strong> <strong>koncept</strong>i predstavljaju dve škole koje se odnose <strong>na</strong> ISA. Tekuće <strong>na</strong><br />

tržištu postoji oko 60 različitih arhitektura, koji su plod razvoja velikih kompanija, i <strong>na</strong> stotinu<br />

implementacija koje se izradjuju (fabrikuju) <strong>na</strong> osnovu licenci ovih arhitektura.<br />

<strong>1.</strong>1 Arhitekturne razlike<br />

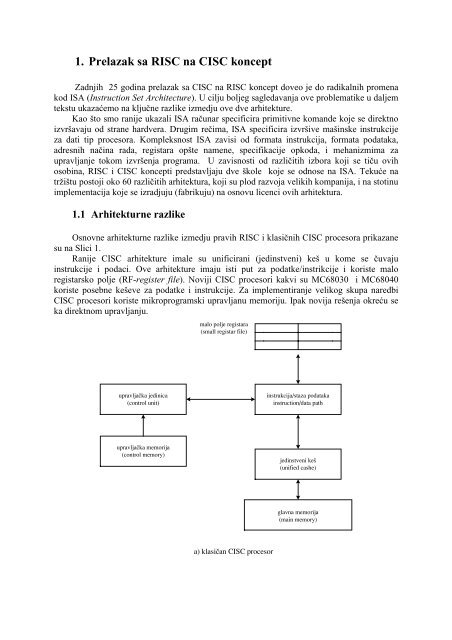

Osnovne arhitekturne razlike izmedju pravih <strong>RISC</strong> i klasičnih <strong>CISC</strong> procesora prikazane<br />

su <strong>na</strong> Slici <strong>1.</strong><br />

Ranije <strong>CISC</strong> arhitekture imale su unificirani (jedinstveni) keš u kome se čuvaju<br />

instrukcije i podaci. Ove arhitekture imaju isti put za podatke/instrikcije i koriste malo<br />

registarsko polje (RF-register file). Noviji <strong>CISC</strong> procesori kakvi su MC68030 i MC68040<br />

koriste posebne keševe za podatke i instrukcije. Za implementiranje velikog skupa <strong>na</strong>redbi<br />

<strong>CISC</strong> procesori koriste mikroprogramski upravljanu memoriju. Ipak novija rešenja okreću se<br />

ka direktnom upravljanju.<br />

malo polje registara<br />

(small registar file)<br />

upravlja~ka jedinica<br />

(control unit)<br />

instrukcija/staza podataka<br />

instruction/data path<br />

upravlja~ka memorija<br />

(control memory)<br />

jedinstveni ke{<br />

(unified cashe)<br />

glav<strong>na</strong> memorija<br />

(main memory)<br />

a) klasi~an <strong>CISC</strong> procesor

veliko polje registara<br />

(large registar file)<br />

upravlja~ka jedinica <strong>sa</strong><br />

direktnim upravljanjem<br />

(hardwired control unit)<br />

staza podataka<br />

(data path)<br />

instrukcioni ke{<br />

(instruction cashe)<br />

ke{ podataka<br />

(data cashe)<br />

instrukcije<br />

(instruction)<br />

glav<strong>na</strong> memorija (main memory)<br />

podaci<br />

(data)<br />

a) pravi <strong>RISC</strong> procesor<br />

Slika 1 Arhitekturne razlike izmedju <strong>RISC</strong> i <strong>CISC</strong> procesora<br />

Kod <strong>RISC</strong> procesora, keševi za podatke i instrukcije su izdvojeni, a takodje su različiti i<br />

putevi preko kojih se pristupa ovim memorijama. Naglasimo da se kod <strong>RISC</strong>-ova koristi<br />

registarsko polje nešto većeg obima. Upravljačka jedinica <strong>RISC</strong>-a je bazira<strong>na</strong> <strong>na</strong> direktnom<br />

upravljanju. Ovakvim pristupom, za slučaj da u programskom toku ne postoji veliki broj<br />

instrukcija gra<strong>na</strong>nja ili prekida (interrupts), moguće je postići CPI reda jedan ciklus.<br />

<strong>1.</strong>2 Smernice razvoja kod <strong>CISC</strong>-ova<br />

Prvi raču<strong>na</strong>ri bili su veoma jednostavni i posedovali su ograničeni skup <strong>na</strong>redbi. Tokom<br />

vreme<strong>na</strong>, i usled brzog razvoja raču<strong>na</strong>ra, kompleksnost instrukcija se povećavala čini se još<br />

brže, ili kako se to popularno ka`e ''koracima od sedam milja''. Razlog ovome, za duži<br />

vremenski period, je bio <strong>na</strong>gli pad cene hardvera, <strong>sa</strong> jedne, a poveća<strong>na</strong> ce<strong>na</strong> softvera, <strong>sa</strong> druge<br />

strane. Krajnji efekat ovog trenda je bio takav da se sve veći broj funkcija podržavao od strane<br />

hardvera, što je dovelo do toga da je skup instrukcija kod ovih procesora postao ogroman, a<br />

takodje se z<strong>na</strong>čajno povećao i broj složenih instrukcija koje ti procesori mogu da izvršavaju.<br />

Najbolji reprezenti <strong>CISC</strong> kocepta su procesori iz serije Intel x86, Motorola MC 68xxx, Digital<br />

VAX serija, i neke IBM mašine. Porast skupa instrukcija je bio stimuli<strong>sa</strong>n popularnošću<br />

mikroprogramskog upravljanja 60-tih i 70-tih godi<strong>na</strong> prošlog veka. Jedan tipičan <strong>CISC</strong><br />

procesor ima više od 300 instrukcija. Pri ovome treba <strong>na</strong>glasiti i korišćenje promenljivih<br />

formata instrukcija/podataka, pri čemu obim tipičnih reči mo`e biti 8-, 16-, 32-, i 64-bita.<br />

Relativno mali skup registara opšte <strong>na</strong>mene, od 8 do 24, se koristi kod <strong>CISC</strong>-ova. Kod<br />

<strong>CISC</strong>-ova postoji veliki broj operacija obraćanja (referenciranja) memoriji, koje koriste <strong>na</strong><br />

desetinu adresnih <strong>na</strong>či<strong>na</strong> rada (oko 20), uključujući indeksno i indirektno adresiranje. Skoro<br />

svi veliki proizvodjači mikroprocesorskih čipova imali su z<strong>na</strong>čajne investicije u razvoju <strong>CISC</strong>

arhitektura od kasnih 60-tih do pojave prvih <strong>RISC</strong> čipova, a to je bilo ranih 80-tih godi<strong>na</strong><br />

prošlog veka.<br />

<strong>1.</strong>3. <strong>RISC</strong> izazovi<br />

Nakon takoreći, tri decenije razvoja <strong>CISC</strong> arhitektura, korisnici raču<strong>na</strong>ra su počeli da<br />

procenjuju (evaluiraju) odnos izmedju ISA i dostupnih hardversko/softverskih tehnologija. Na<br />

osnovu a<strong>na</strong>liza programa (uglavnom sprovedenih trasiranjem) ustanovljeno je da <strong>sa</strong>mo 25%<br />

od svih raspoloživih kompleksnih instrukcija troši 95% od ukupnog vreme<strong>na</strong> potrebnog za<br />

izvršenje programa. To, drugim rečima, z<strong>na</strong>či da se ostalih 75% hardversko-podr`avanih<br />

instrukcija retko koristi u toku izvršenja programa (manje od 5%). Tako se i rodila ideja o<br />

<strong>RISC</strong>-ovima koja se bazira <strong>na</strong> sledećoj činjenici: Učini ono što se <strong>na</strong>jviše koristi <strong>na</strong>jbr`im.<br />

Kao posledica ovakvog pristupa ostvarilo se dramatično povećanje performansi u odnosu <strong>na</strong><br />

<strong>CISC</strong> dizajn. Klasično pitanje koje se, projektantima <strong>RISC</strong>-ova, <strong>sa</strong>da postavlja je sledeće:<br />

Zbog čega tro{iti veliki deo površine čipa <strong>na</strong> instrukcije koje se retko koriste Odgovor bi bio<br />

sledeći: Kompleksne instrukcije, <strong>na</strong>kon procene njihovog pojavljivanja u programima, treba<br />

kada je njihov proce<strong>na</strong>t mali implementirati softverski (u vidu potprograma), a ne hardverski<br />

kakva je bila dotada{nja prak<strong>sa</strong> kod <strong>CISC</strong> procesora. Implementacija retko korišćenih<br />

instrukcija u softveru omogućava da se skoro svi gradivni blokovi procesora smeste <strong>na</strong><br />

jedinstveni VLSI čip. Šta više, u okviru jednog <strong>RISC</strong> procesorskog čipa, <strong>na</strong> da<strong>na</strong>{njem nivou<br />

tehnologije, moguće je ugraditi <strong>sa</strong>da on-chip keš kao i ve}i broj FP jedinica. Obično, skup<br />

instrukcija <strong>RISC</strong> procesora je manji od 100 instrukcija, pri čemu su instrukcije obima 32- ili<br />

64- bita, ali ne oba formata istovremeno. U principu se koriste od tri do pet adresnih <strong>na</strong>či<strong>na</strong><br />

rada. Arhitektura <strong>RISC</strong>-a je tipa Load/Store. To z<strong>na</strong>či da sve instrukcije pribavljaju operande<br />

iz registara i smeštaju rezultate i registre (register-based), a da su Load i Store jedine dve<br />

<strong>na</strong>redbe pomoću kojih se procesor obraća memoriji.<br />

<strong>RISC</strong> procesor često koristi dva poseb<strong>na</strong> registarska polja. Jedno polje čine 32 registra<br />

za manipuli<strong>sa</strong>nje <strong>sa</strong> celobrojnim vrednostima i adre<strong>sa</strong>ma (integer register file), a drugo polje<br />

se <strong>sa</strong>stoji od 32 registra koji se koriste kod manipuli<strong>sa</strong>nja brojeva u pokretnom zarezu<br />

(floating point register file). Neki od <strong>RISC</strong> procesora koriste i više od 100 registara. Pored<br />

korišćenja registarskih polja velikog obima, podeljeni keševi za instrukcije i podaci dodatno i<br />

z<strong>na</strong>čajno skraćuju vreme pristupa memoriji.<br />

Osnov<strong>na</strong> ideja <strong>RISC</strong>-a je da se <strong>na</strong>jveći broj instrukcija izvrši za jedan ciklus što se<br />

postiže pribavljanjem operanda direktnim putem iz registara, bafera preuredjenja ili keša<br />

podataka, a ne kao kod <strong>CISC</strong>-ova iz memorije. Na Slici 2 uporedno su prikazane ključne<br />

karakteristike pravih <strong>RISC</strong> i klasičnih <strong>CISC</strong> procesora. Napredkom tehnologije, u budućnosti,<br />

neke arhitekturne razlike <strong>sa</strong> Slike 2 sigurno će nestati.

karakteristike klasi~<strong>na</strong> <strong>CISC</strong> arhitektura prava <strong>RISC</strong> arhitektura<br />

format instrukcije promenljivi format 8,16,32i fiks<strong>na</strong> 32-bitne instrukcije<br />

64 bita<br />

takt<strong>na</strong> frekvencija 100-500 MHz 200-400 MHz<br />

polje registara<br />

8-24 registara op{te nemene 32-192 registara op{te<br />

<strong>na</strong>mene, izdvojeni integer i<br />

FP registri<br />

broj instrukcija i tipovi<br />

oko 300, <strong>sa</strong> preko<br />

~etrdesetak varijanti<br />

instrukcionih tipova<br />

oko 100, <strong>na</strong>jve}i broj su<br />

registarsko zasnovani <strong>sa</strong><br />

izuzetkom Load/Store<br />

adresni <strong>na</strong>~ini rada<br />

dizajn ke{a<br />

CPI, i prose~ni CPI<br />

upravlja~ka jedinica CPU-a<br />

tipi~ni reprezentativni<br />

rocesori<br />

<strong>na</strong> desetinu (reda 20)<br />

uklju~uju}i indeksno/<br />

indirektno adresiranje<br />

raniji modeli su koristili<br />

jedinstveni ke{, noviji<br />

koriste razdvojene ke{eve za<br />

instrukcije i podatke<br />

1-20 ciklu<strong>sa</strong>, u proseku 4<br />

ciklu<strong>sa</strong><br />

<strong>na</strong>jve}i broj koristi<br />

mikroprogramsko<br />

upravljanje, a kod nekih<br />

imamo i direktno<br />

Intel x86, VAX 8600,<br />

IBM 390, MC 68040,<br />

Intel Pentium, AMD 486,<br />

Cyrix 686<br />

ograni~eno <strong>na</strong> 3-5, <strong>sa</strong>mo<br />

Load/Store adresiraju<br />

meoriju<br />

<strong>na</strong>jve}i broj koristi podeljeni<br />

ke{ za instrukcije i podatke<br />

1 ciklus za jednostavne<br />

operacije, 1,5 ciklus u<br />

proseku<br />

<strong>na</strong>jve}i broj koristi direktno<br />

upravljanje bez upravlja~ke<br />

memorije<br />

Sun UltraSparc,<br />

MIPS R10000,<br />

Power PC 604, HP PA-<br />

8000, Digital 21264<br />

Slika 2. Karakteristike klasičnih <strong>CISC</strong> i pravih <strong>RISC</strong> arhitektura<br />

<strong>1.</strong>3 Šta je donela dvo-decenijska ISA debata<br />

Korišćenjem velikog registarskog polja, bafera podataka, i izdvojenih keševa za<br />

instrukcije i podatke, imalo je povoljan efekat <strong>na</strong> interno prosledjivanje podataka kroz CPU,<br />

kao i elimini<strong>sa</strong>nju nepotrebnih memori<strong>sa</strong>nja (pamćenja) medjurezultata operacija. Sa z<strong>na</strong>čajno<br />

smanjenom kompleksnošću skupa instrukcija, <strong>RISC</strong> procesor se može lakše projektovati i<br />

realizovati kao jedinstveni VLSI čip. Prednost ovog pristupa su rad <strong>na</strong> višim frekvencijama,<br />

niži prosečni CPI koji se mo`e posti}i, ni`i proce<strong>na</strong>t keš promašaja koji se može ostvariti, i<br />

bolje mogućnosti koje stoje <strong>na</strong> raspolaganju za optimizaciju kompilatora.<br />

Ipak prelazak <strong>sa</strong> <strong>CISC</strong> <strong>na</strong> <strong>RISC</strong> <strong>koncept</strong> predstavljao je radikalan preokret u arhitekturi.<br />

Glav<strong>na</strong> žrtva je predstavljala gubitak bi<strong>na</strong>rne kompatibilnosti <strong>sa</strong> tradicio<strong>na</strong>lnim <strong>CISC</strong><br />

aplikacionim programima. Naime, postoje}i programi kreirani za neku od <strong>CISC</strong> ma{i<strong>na</strong> nisu<br />

mogli vi{e da se <strong>sa</strong>da izvršavaju <strong>na</strong> <strong>RISC</strong> maši<strong>na</strong>ma. Sprovede<strong>na</strong> istra`ivanja koja su se<br />

odnosila <strong>na</strong> trasiranje osobi<strong>na</strong> programa pokazala su da konverzija <strong>sa</strong> <strong>CISC</strong> programa <strong>na</strong><br />

ekvivalnetni <strong>RISC</strong> program podrazumeva povećanje dužine programa (broj instrukcija) za<br />

oko 40%. Negativni efekat povećanja dužine <strong>RISC</strong> programa, <strong>sa</strong> aspekta vreme<strong>na</strong> izvršenja,

je ipak ~ini se manji u odnosu <strong>na</strong> pozitivne efekte koji se postižu povećanjem taktne<br />

frekvencije i smanjenjem prosečnog broja CPI-a kod <strong>RISC</strong> procesora.<br />

Debata izmedju projekta<strong>na</strong>ta <strong>RISC</strong> i <strong>CISC</strong> procesora, oko toga koji je pristup bolji, po<br />

svemu izgleda je <strong>sa</strong>da završe<strong>na</strong>. Obe strane u proteklom periodu <strong>na</strong>učile su i prihvatile jed<strong>na</strong><br />

od druge puno dobrih i korisnih sugestija i rešenja. Na da<strong>na</strong>šnjem nivou razvoja po svemu<br />

sude}i te granice su postale takoreći nevidljive. Veliki broj procesora da<strong>na</strong>s se implementira u<br />

istoj tehnologiji ugradjivanjem hibridnih rešenja koje uzimaju u obzir dobre osobine kako<br />

<strong>RISC</strong> tako i <strong>CISC</strong> procesora. Verovatno je kompromis, kao i uvek, <strong>na</strong>jboje rešenje.