- Page 1 and 2: PROCESSEURS DÉDIÉS AU TRAITEMENT

- Page 3: CONTEXTE

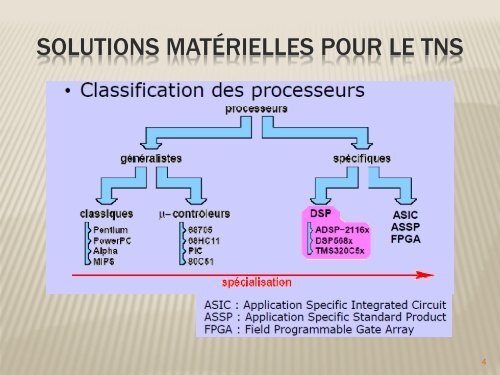

- Page 7 and 8: SOLUTIONS MATÉRIELLES POUR LE TNS

- Page 9 and 10: SOLUTIONS MATÉRIELLES POUR LE TNS

- Page 11 and 12: LES CONTRAINTES EN TNS 11

- Page 13 and 14: APPLICATIONS DES DSP 13

- Page 15 and 16: CONSTRUCTEURS DE DSP 15

- Page 17 and 18: OPÉRATION MAC L’opération clas

- Page 19 and 20: FILTRE FIR y( n) N 1 i0 a( i) x(

- Page 21 and 22: SPÉCIFICITÉS DES DSP Objectifs:

- Page 23 and 24: ARCHITECTURE VON NEUMAN CPU BUS Mé

- Page 25 and 26: ARCHITECTURE HARVARD CPU Mémoire P

- Page 27 and 28: CACHE D'INSTRUCTIONS cache d’inst

- Page 29 and 30: MODE D’ADRESSAGE - L’ ADRESSAGE

- Page 31 and 32: SUPER HARVARD ARCHITECTURE: LE DSP

- Page 33 and 34: UNITÉ DE COMMANDE Chef d’orches

- Page 35 and 36: UNITÉS DE GÉNÉRATION D’ADRESSE

- Page 37 and 38: CONSÉQUENCES- EXEMPLE 37

- Page 39 and 40: PIPELINE 39

- Page 41 and 42: PROCESSEURS DSP CONVENTIONNELS AMÉ

- Page 43 and 44: PROCESSEURS DSP CONVENTIONNELS MULT

- Page 45 and 46: HISTORIQUE DES DSP 1 e génératio

- Page 47: Performance FAMILLE DSP ANALOG DEVI

- Page 50 and 51: FORMAT DE CALCUL DANS LES DSP Deux

- Page 52 and 53: DSP EN VIRGULE FIXE (FIXED POINT) E

- Page 54 and 55:

Exemple :N=8 k=5 • Format Q 5 sur

- Page 56 and 57:

REPRÉSENTATION EN NON-SIGNÉ (“U

- Page 58 and 59:

REPRÉSENTATION EN VIRGULE FIXE 58

- Page 60 and 61:

EXERCICE on est en format 1.2 fixe

- Page 62 and 63:

SHARC ADSP21065L 62

- Page 64 and 65:

FORMAT VIRGULE FLOTTANTE IEEE 754

- Page 66 and 67:

EXERCICE On veut représenter -7.5

- Page 68 and 69:

BORNES IEEE 754 • Plus grande val

- Page 70 and 71:

IEEE 754: RÉSUMÉ Normalisé: Dén

- Page 72 and 73:

SHARC ADSP21065L 72

- Page 74 and 75:

OPÉRATIONS EN VIRGULE FIXE Pour l

- Page 76 and 77:

SOLUTION 1.3 SIGNED -2 0 B 3+2 -1 B

- Page 78 and 79:

EXEMPLE : 1 + 0.75 1= 1/ 2 0 E=0

- Page 80 and 81:

OPÉRATIONS EN VIRGULE FLOTTANTE L

- Page 82 and 83:

PERFORMANCES Les unités de mesure

- Page 84 and 85:

EXEMPLE Soit un DSP ayant une perf

- Page 86 and 87:

PERFORMANCES Inconvénient: Ce ty

- Page 88 and 89:

EXEMPLE ADSP21065L 88

- Page 90 and 91:

SHARC ARCHITECTURE 90

- Page 92 and 93:

LES REGISTRES DE DONNÉES Pour le

- Page 94 and 95:

LES DONNÉES Les opérations sont

- Page 96 and 97:

FORMAT FLOTTANT 96

- Page 98 and 99:

EXERCICE Utilisation de l’enviro

- Page 100 and 101:

L’UNITÉ DE CALCUL ALU 100

- Page 102 and 103:

ALU INSTRUCTIONS Rn = Rx + Ry Fn =

- Page 104 and 105:

LES BITS DE CONTRÔLE : LES « FLAG

- Page 106 and 107:

INTRODUCTION AUX TD/TP R0=0.5; R1

- Page 108 and 109:

LE MULTIPLIEUR 108

- Page 110 and 111:

LE MULTIPLIEUR MAC en « fixed-poi

- Page 112 and 113:

MULTIPLICATION - FIXED-POINT Soit

- Page 114 and 115:

INTRODUCTION AUX TD/TP - MULTIPLICA

- Page 116 and 117:

LES BITS DE CONTRÔLE : LES « FLAG

- Page 118 and 119:

LES INSTRUCTIONS PARALLÈLES 118

- Page 120 and 121:

LE SHIFTER Le shifter travaille su

- Page 122 and 123:

LE SHIFTER - LES FLAGS Registre As

- Page 124 and 125:

EXERCICE debut: r0=0xff; r2=0x210;

- Page 126 and 127:

LE SHIFTER - DÉPÔT /EXTRACTION 12

- Page 128 and 129:

LE SHIFTER - DÉPÔT /EXTRACTION E

- Page 130 and 131:

EXERCICE r11=fext r10 by 24:8; 130

- Page 132 and 133:

EXERCICE R13= 0001101000; btst r1

- Page 134 and 135:

GÉNÉRATEURS D’ADRESSE 134

- Page 136 and 137:

GÉNÉRATEURS D’ADRESSE Exemple

- Page 138 and 139:

GÉNÉRATEURS D’ADRESSE Il est p

- Page 140 and 141:

SÉQUENCEUR DE PROGRAMME 140

- Page 142 and 143:

SÉQUENCEUR DE PROGRAMME Boucle :

- Page 144 and 145:

SÉQUENCEUR DE PROGRAMME 144

- Page 146 and 147:

SÉQUENCEUR DE PROGRAMME - PIPELINE

- Page 148 and 149:

SÉQUENCEUR DE PROGRAMME - INSTRUCT

- Page 150 and 151:

LE SHIFTER Instruction conditionne

- Page 152:

IMPACT DU PIPELINE SUR LA PROGRAMMA