Beovision 9 50 MKII FHD-D9 Type 9720-9730 - abo - center

Beovision 9 50 MKII FHD-D9 Type 9720-9730 - abo - center

Beovision 9 50 MKII FHD-D9 Type 9720-9730 - abo - center

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

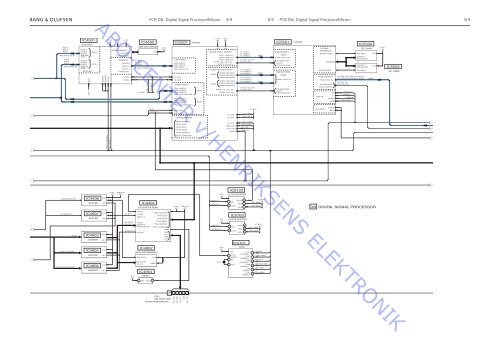

PCB DN, Digital Signal Processor/Micom 8. 8. PCB DN, Digital Signal Processor/Micom<br />

8.<br />

1<br />

RE0-9<br />

GE0-9<br />

BE0-9<br />

HDE,VDE,CLKE-57<br />

RO0-9<br />

GO0-9<br />

BO0-9<br />

HDO,VDO,CLKO<br />

IC4<strong>50</strong>1<br />

LSI57Plus<br />

RVIA0-9<br />

GYIA0-9<br />

BUIA0-9<br />

DHA,DVA,<br />

DCKA<br />

RVIB0-9<br />

GYIB0-9<br />

BUIB0-9<br />

DHB,DVB,<br />

DCKB<br />

RV,GY,BU<br />

NRST<br />

NRST<br />

[EVEN]<br />

[ODD]<br />

SCKREF<br />

MCKREF<br />

+1.5V +2.5V +3.3V<br />

REFCK<br />

OCKREF<br />

DDR-SDRAM I/F<br />

DQ0-DQ31<br />

ADRS0-ADRS11<br />

RGB OUT<br />

ROUT0-9<br />

GOUT0-9<br />

BOUT0-9<br />

HP,VP,OCKO<br />

I2CSCL<br />

I2CSDA<br />

57_R0-9<br />

57_G0-9<br />

57_B0-9<br />

IC4<strong>50</strong>2<br />

32M DDR SDRAM<br />

57_HD,57_VD,57_CLK<br />

IIC_BUS<br />

P3V_SDA2<br />

P3V_SCL2<br />

VDD<br />

+2.5V<br />

IC5201<br />

LSI57 INPUT<br />

LSI57_RIN0-9<br />

LSI57_GIN0-9<br />

LSI57_BIN0-9<br />

LSI57-HP,-VP,-CLK<br />

IIC_SCL<br />

IIC_SDA<br />

FPGA1 INPUT<br />

FPGA_RINE0-9<br />

FPGA_GINE0-9<br />

FPGA_BINE0-9<br />

FPGA_HDE,VDE,CLKE<br />

FPGA_RINO0-9<br />

FPGA_GINO0-9<br />

FPGA_BINO0-9<br />

FPGA2<br />

[EVEN]<br />

[ODD]<br />

+1.5V<br />

VCC<br />

+3.3V<br />

VCC<br />

I-CHIPS PORT1 OUTPUT<br />

PORT1_ROUT0-9<br />

PORT1_GOUT0-9<br />

PORT1_BOUT0-9<br />

PORT1_HS,_VS,_CLK<br />

PORT1_FLD,_ACT<br />

I-CHIPS PORT2 OUTPUT<br />

[EVEN]<br />

[ODD]<br />

PORT2_ROUTE0-9<br />

PORT2_GOUTE0-9<br />

PORT2_BOUTE0-9<br />

PORT2_ROUTO0-9<br />

PORT2_GOUTO0-9<br />

PORT2_BOUTO0-9<br />

PORT2_HS,_VS,_CLK<br />

PORT2_FLD,_ACT<br />

P1_Y/G0-9<br />

P1_PB/B0-9<br />

P1_PR/R0-9<br />

P1_HS,_VS,_CLK<br />

P1_FLD,_ACT<br />

P2_Y/GE0-9<br />

P2_PB/BE0-9<br />

P2_PR/RE0-9<br />

P2_Y/GO0-9<br />

P2_PB/BO0-9<br />

P2_PR/RO0-9<br />

P2_HS,_VS,_CLK<br />

P2_FLD,_ACT<br />

(30bit)<br />

(30bit)<br />

(30bit)<br />

IC5<strong>50</strong>1<br />

RGB IN PORT1<br />

PI1CLK<br />

(30bit)<br />

PI1DO_0-PI1D_29<br />

PI1HSB,PI1VSB,<br />

PI1FLD,PI1ACTB<br />

RGB IN PORT2<br />

(60bit)<br />

PI2DO_0-PI2D_29<br />

PI2HSB,PI2VSB,<br />

PI2CLK<br />

PI2FLD,PI2ACTB<br />

I-CHIPS<br />

SD-RAM<br />

SD RAM2 DATA<br />

POHSB,POVSB<br />

POFLD,POAVTB<br />

CPU I/F<br />

INTERFACE<br />

SD-RAM1 DATA<br />

ADDRESS<br />

FPGA3 OUTPUT<br />

POD_0-POD_59<br />

SO<br />

SI<br />

SCLKB<br />

RSTB<br />

PO_HS,_VS<br />

PO_FLD,_ACT<br />

DQ1-DQ31<br />

DQ1-DQ31<br />

PO_RE0-9,PO_GE0-9,PO_BE0-9<br />

PO_RO0-9,PO_GO0-9,PO_BO0-9<br />

MCDATA-0<br />

ICHIPS-SI<br />

MCCLK<br />

ICHIPS-RST<br />

IC5<strong>50</strong>2<br />

SD_RAM1<br />

ADDR0-11<br />

WE,CAS,RAS<br />

ADDR0-11<br />

WE,CAS,RAS<br />

(60bit)<br />

VCC<br />

VCC<br />

+3.3V<br />

IC5<strong>50</strong>3<br />

SD_RAM2<br />

FPGA_HDO,VDO,CLKO<br />

3<br />

FLD<br />

CLK2X_E<br />

FPGA_FLD<br />

CLK2X_E<br />

CONFIGURATION<br />

IIC_SDA<br />

IIC_SCL<br />

P3V_SDA2<br />

P3V_SCL2<br />

IIC_BUS<br />

CLK INPUT<br />

POCLK<br />

MCLK<br />

FPGA_NCONFIG<br />

FPGA_DCLK<br />

FPGA_DCLK<br />

FPGA_DATA0<br />

FPGA_NSTATUS<br />

IIC_CLK<br />

OSD_CLKI<br />

OSD_CLKO<br />

RESET<br />

CLKM_20MHz<br />

OSD_72MHz<br />

PO_CLK<br />

NRST-FP<br />

21<br />

23<br />

REFCK_39.5MHz<br />

OCK-90MHz<br />

FPGA_CONFDONE<br />

25<br />

5<br />

7<br />

27<br />

D0,D5-D7,D12-D15<br />

IC4906<br />

BUFFER<br />

VCC<br />

DIR<br />

+3.3V<br />

STB+3.3V<br />

IC4302<br />

CPLD(FPGA ROM)<br />

+3.3V<br />

STB+3.3V<br />

CBCLK_A<br />

X2CBCLK_A<br />

+3.3V<br />

1<br />

IC5103<br />

CLOCK BUFFER<br />

7<br />

XIN<br />

LCLK1<br />

LCLK2<br />

SDAT<br />

SCLK<br />

8<br />

5<br />

6<br />

P3V_SDA2<br />

P3V_SCL2<br />

IIC_BUS<br />

DN<br />

DIGITAL SIGNAL PROCESSOR<br />

9<br />

D1-D4,D8-D11<br />

A8-A15<br />

IC4907<br />

BUFFER<br />

IC4903<br />

VCC<br />

DIR<br />

VCC<br />

D1-D15<br />

WE,CE,OE<br />

A0-A18<br />

CONFIG-OE<br />

GCLK2<br />

FLASH<br />

DATA0-15<br />

FLASH<br />

ADDR0-18<br />

NWE,NCE,NOE<br />

DEV-OE<br />

FPGA_NCONFIG<br />

FPGA_DCLK<br />

FPGA_DCLK<br />

FPGA_DATA0<br />

FPGA_NSTATUS<br />

FPGA_CONFDONE<br />

NRST<br />

TDO<br />

TDI<br />

TMS<br />

CBCLK_B<br />

+3.3V<br />

X2CBCLK_B<br />

1<br />

7<br />

IC5103<br />

CLOCK BUFFER<br />

XIN<br />

LCLK1<br />

LCLK2<br />

SDAT<br />

SCLK<br />

8<br />

5<br />

6<br />

P3V_SDA3<br />

P3V_SCL3<br />

IIC_BUS<br />

11<br />

A3-A7,A17,A18WE<br />

A0-A2,A16,A19,CE2,OE<br />

BUFFER<br />

IC4905<br />

BUFFER<br />

IC4908<br />

BUFFER<br />

OE1<br />

VCC<br />

OE1<br />

VCC<br />

OE1<br />

+3.3V<br />

IC4902<br />

8M FLASH MEMORY<br />

DQ1-DQ15<br />

WE,CE,OE<br />

A0-A18<br />

IC4904<br />

RESET<br />

VCC<br />

RESET<br />

TCK<br />

+3.3V<br />

X5701<br />

ABO-CENTER v/HENRIKSENS ELEKTRONIK<br />

8<br />

1<br />

20<br />

VDD<br />

XT<br />

XTN<br />

IC5701<br />

CLK2<br />

(40MHz)<br />

CPG<br />

CLK7<br />

(4.25MHz)<br />

CLK1<br />

(2088MHz)<br />

CLK3<br />

(74.25MHz)<br />

CLK6<br />

(39.5MHz)<br />

CLK5<br />

(72MHz)<br />

CLK4<br />

(90MHz)<br />

8<br />

7<br />

9<br />

12<br />

13<br />

14<br />

CLK7425<br />

CLKM_20MHz<br />

CLK7425-1<br />

REFCK39.5MHz<br />

OSD_72MHz<br />

OCK_90MHz<br />

2<br />

VDD<br />

VOUT<br />

1<br />

DN<br />

10<br />

FOR<br />

FACTORY USE<br />

(FPGA ROM WRITER)<br />

1<br />

FPGA-TCK<br />

2<br />

FPGA-TMS<br />

3<br />

FPGA-TDI<br />

4<br />

GND<br />

5<br />

FPGA-TDO