Diseño de un Algoritmo en Hardware para la ... - Iberchip.net

Diseño de un Algoritmo en Hardware para la ... - Iberchip.net

Diseño de un Algoritmo en Hardware para la ... - Iberchip.net

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

System G<strong>en</strong>erador. Finalm<strong>en</strong>te, <strong>la</strong> sección 6 pres<strong>en</strong>ta <strong>la</strong>s<br />

conclusiones y el trabajo futuro.<br />

2. TRABAJOS PREVIOS<br />

Des<strong>de</strong> <strong>la</strong> aparición <strong>de</strong> Radio Software se han propuesto<br />

varias alternativas <strong>para</strong> <strong>la</strong> implem<strong>en</strong>tación <strong>de</strong> radios<br />

digitales empleando circuitos programables como<br />

Microprocesadores <strong>de</strong> Propósito G<strong>en</strong>eral (G<strong>en</strong>eral<br />

Purpose Processors, GPPs), Procesadores Digitales <strong>de</strong><br />

Señales (Digital Signal Processors, DSPs), FPGAs (Field<br />

Programmable Gate Arrays) y ASICs (Application<br />

Specific Integrated Circuits).<br />

Los fabricantes <strong>de</strong> FPGAs están ori<strong>en</strong>tando esfuerzos<br />

hacia <strong>la</strong> implem<strong>en</strong>tación <strong>de</strong> RS <strong>en</strong> FPGAs. Este es el caso<br />

<strong>de</strong> Altera y Xilinx, los dos más gran<strong>de</strong>s v<strong>en</strong><strong>de</strong>dores <strong>de</strong><br />

FPGAs <strong>en</strong> el m<strong>un</strong>do, están proponi<strong>en</strong>do soluciones <strong>para</strong><br />

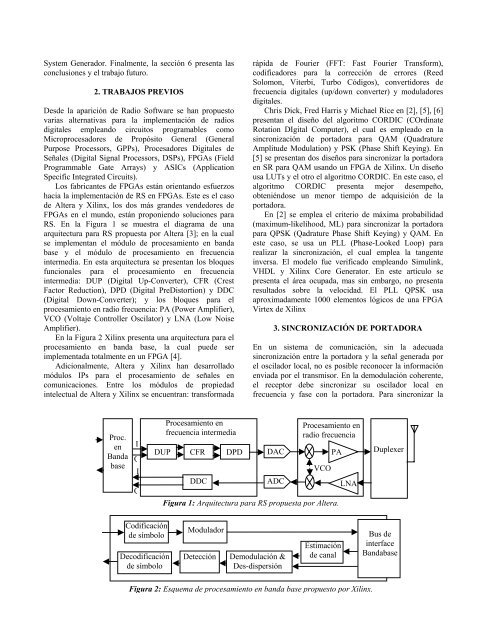

RS. En <strong>la</strong> Figura 1 se muestra el diagrama <strong>de</strong> <strong>un</strong>a<br />

arquitectura <strong>para</strong> RS propuesta por Altera [3]; <strong>en</strong> <strong>la</strong> cual<br />

se implem<strong>en</strong>tan el módulo <strong>de</strong> procesami<strong>en</strong>to <strong>en</strong> banda<br />

base y el módulo <strong>de</strong> procesami<strong>en</strong>to <strong>en</strong> frecu<strong>en</strong>cia<br />

intermedia. En esta arquitectura se pres<strong>en</strong>tan los bloques<br />

f<strong>un</strong>cionales <strong>para</strong> el procesami<strong>en</strong>to <strong>en</strong> frecu<strong>en</strong>cia<br />

intermedia: DUP (Digital Up-Converter), CFR (Crest<br />

Factor Reduction), DPD (Digital PreDistortion) y DDC<br />

(Digital Down-Converter); y los bloques <strong>para</strong> el<br />

procesami<strong>en</strong>to <strong>en</strong> radio frecu<strong>en</strong>cia: PA (Power Amplifier),<br />

VCO (Voltaje Controller Osci<strong>la</strong>tor) y LNA (Low Noise<br />

Amplifier).<br />

En <strong>la</strong> Figura 2 Xilinx pres<strong>en</strong>ta <strong>un</strong>a arquitectura <strong>para</strong> el<br />

procesami<strong>en</strong>to <strong>en</strong> banda base, <strong>la</strong> cual pue<strong>de</strong> ser<br />

implem<strong>en</strong>tada totalm<strong>en</strong>te <strong>en</strong> <strong>un</strong> FPGA [4].<br />

Adicionalm<strong>en</strong>te, Altera y Xilinx han <strong>de</strong>sarrol<strong>la</strong>do<br />

módulos IPs <strong>para</strong> el procesami<strong>en</strong>to <strong>de</strong> señales <strong>en</strong><br />

com<strong>un</strong>icaciones. Entre los módulos <strong>de</strong> propiedad<br />

intelectual <strong>de</strong> Altera y Xilinx se <strong>en</strong>cu<strong>en</strong>tran: transformada<br />

rápida <strong>de</strong> Fourier (FFT: Fast Fourier Transform),<br />

codificadores <strong>para</strong> <strong>la</strong> corrección <strong>de</strong> errores (Reed<br />

Solomon, Viterbi, Turbo Códigos), convertidores <strong>de</strong><br />

frecu<strong>en</strong>cia digitales (up/down converter) y modu<strong>la</strong>dores<br />

digitales.<br />

Chris Dick, Fred Harris y Michael Rice <strong>en</strong> [2], [5], [6]<br />

pres<strong>en</strong>tan el diseño <strong>de</strong>l algoritmo CORDIC (COrdinate<br />

Rotation DIgital Computer), el cual es empleado <strong>en</strong> <strong>la</strong><br />

sincronización <strong>de</strong> portadora <strong>para</strong> QAM (Quadrature<br />

Amplitu<strong>de</strong> Modu<strong>la</strong>tion) y PSK (Phase Shift Keying). En<br />

[5] se pres<strong>en</strong>tan dos diseños <strong>para</strong> sincronizar <strong>la</strong> portadora<br />

<strong>en</strong> SR <strong>para</strong> QAM usando <strong>un</strong> FPGA <strong>de</strong> Xilinx. Un diseño<br />

usa LUTs y el otro el algoritmo CORDIC. En este caso, el<br />

algoritmo CORDIC pres<strong>en</strong>ta mejor <strong>de</strong>sempeño,<br />

obt<strong>en</strong>iéndose <strong>un</strong> m<strong>en</strong>or tiempo <strong>de</strong> adquisición <strong>de</strong> <strong>la</strong><br />

portadora.<br />

En [2] se emplea el criterio <strong>de</strong> máxima probabilidad<br />

(maximum-likelihood, ML) <strong>para</strong> sincronizar <strong>la</strong> portadora<br />

<strong>para</strong> QPSK (Qadrature Phase Shift Keying) y QAM. En<br />

este caso, se usa <strong>un</strong> PLL (Phase-Looked Loop) <strong>para</strong><br />

realizar <strong>la</strong> sincronización, el cual emplea <strong>la</strong> tang<strong>en</strong>te<br />

inversa. El mo<strong>de</strong>lo fue verificado empleando Simulink,<br />

VHDL y Xilinx Core G<strong>en</strong>erator. En este artículo se<br />

pres<strong>en</strong>ta el área ocupada, mas sin embargo, no pres<strong>en</strong>ta<br />

resultados sobre <strong>la</strong> velocidad. El PLL QPSK usa<br />

aproximadam<strong>en</strong>te 1000 elem<strong>en</strong>tos lógicos <strong>de</strong> <strong>un</strong>a FPGA<br />

Virtex <strong>de</strong> Xilinx<br />

3. SINCRONIZACIÓN DE PORTADORA<br />

En <strong>un</strong> sistema <strong>de</strong> com<strong>un</strong>icación, sin <strong>la</strong> a<strong>de</strong>cuada<br />

sincronización <strong>en</strong>tre <strong>la</strong> portadora y <strong>la</strong> señal g<strong>en</strong>erada por<br />

el osci<strong>la</strong>dor local, no es posible reconocer <strong>la</strong> información<br />

<strong>en</strong>viada por el transmisor. En <strong>la</strong> <strong>de</strong>modu<strong>la</strong>ción coher<strong>en</strong>te,<br />

el receptor <strong>de</strong>be sincronizar su osci<strong>la</strong>dor local <strong>en</strong><br />

frecu<strong>en</strong>cia y fase con <strong>la</strong> portadora. Para sincronizar <strong>la</strong><br />

Proc.<br />

<strong>en</strong><br />

Banda<br />

base<br />

I<br />

Q<br />

I<br />

Q<br />

Procesami<strong>en</strong>to <strong>en</strong><br />

frecu<strong>en</strong>cia intermedia<br />

DUP CFR DPD<br />

DDC<br />

DAC<br />

ADC<br />

Procesami<strong>en</strong>to <strong>en</strong><br />

radio frecu<strong>en</strong>cia<br />

VCO<br />

Figura 1: Arquitectura <strong>para</strong> RS propuesta por Altera.<br />

PA<br />

LNA<br />

Duplexer<br />

Codificación<br />

<strong>de</strong> símbolo<br />

Decodificación<br />

<strong>de</strong> símbolo<br />

Modu<strong>la</strong>dor<br />

Detección<br />

Demodu<strong>la</strong>ción &<br />

Des-dispersión<br />

Estimación<br />

<strong>de</strong> canal<br />

Bus <strong>de</strong><br />

interface<br />

Bandabase<br />

Figura 2: Esquema <strong>de</strong> procesami<strong>en</strong>to <strong>en</strong> banda base propuesto por Xilinx.