Una MetodologÃa Integral de Diseño Digital con CPLDs, VHDL y C

Una MetodologÃa Integral de Diseño Digital con CPLDs, VHDL y C

Una MetodologÃa Integral de Diseño Digital con CPLDs, VHDL y C

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

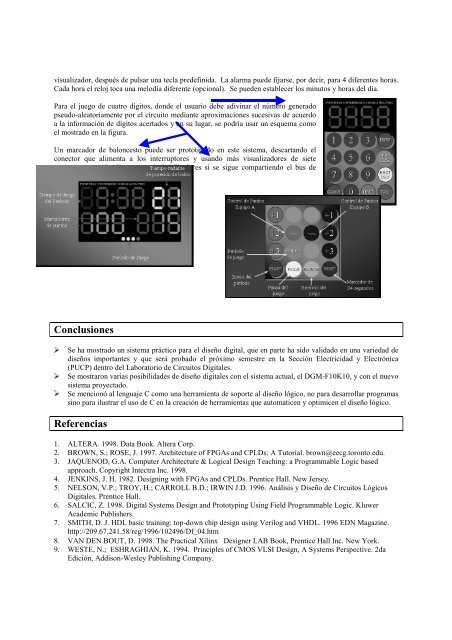

visualizador, <strong>de</strong>spués <strong>de</strong> pulsar una tecla pre<strong>de</strong>finida. La alarma pue<strong>de</strong> fijarse, por <strong>de</strong>cir, para 4 diferentes horas.<br />

Cada hora el reloj toca una melodía diferente (opcional). Se pue<strong>de</strong>n establecer los minutos y horas <strong>de</strong>l día.<br />

Para el juego <strong>de</strong> cuatro dígitos, don<strong>de</strong> el usuario <strong>de</strong>be adivinar el número generado<br />

pseudo-aleatoriamente por el circuito mediante aproximaciones sucesivas <strong>de</strong> acuerdo<br />

a la información <strong>de</strong> dígitos acertados y en su lugar, se podría usar un esquema como<br />

el mostrado en la figura.<br />

Un marcador <strong>de</strong> baloncesto pue<strong>de</strong> ser prototipado en este sistema, <strong>de</strong>scartando el<br />

<strong>con</strong>ector que alimenta a los interruptores y usando más visualizadores <strong>de</strong> siete<br />

segmentos, que implica usar más habilitadores si se sigue compartiendo el bus <strong>de</strong><br />

datos.<br />

Conclusiones<br />

Se ha mostrado un sistema práctico para el diseño digital, que en parte ha sido validado en una variedad <strong>de</strong><br />

diseños importantes y que será probado el próximo semestre en la Sección Electricidad y Electrónica<br />

(PUCP) <strong>de</strong>ntro <strong>de</strong>l Laboratorio <strong>de</strong> Circuitos <strong>Digital</strong>es.<br />

Se mostraron varias posibilida<strong>de</strong>s <strong>de</strong> diseño digitales <strong>con</strong> el sistema actual, el DGM-F10K10, y <strong>con</strong> el nuevo<br />

sistema proyectado.<br />

Se mencionó al lenguaje C como una herramienta <strong>de</strong> soporte al diseño lógico, no para <strong>de</strong>sarrollar programas<br />

sino para ilustrar el uso <strong>de</strong> C en la creación <strong>de</strong> herramientas que automaticen y optimicen el diseño lógico.<br />

Referencias<br />

1. ALTERA. 1998. Data Book. Altera Corp.<br />

2. BROWN, S.; ROSE, J. 1997. Architecture of FPGAs and <strong>CPLDs</strong>: A Tutorial. brown@eecg.toronto.edu.<br />

3. JAQUENOD, G.A. Computer Architecture & Logical Design Teaching: a Programmable Logic based<br />

approach. Copyright Intectra Inc. 1998.<br />

4. JENKINS, J. H. 1982. Designing with FPGAs and <strong>CPLDs</strong>. Prentice Hall. New Jersey.<br />

5. NELSON, V.P.; TROY, H.; CARROLL B.D.; IRWIN J.D. 1996. Análisis y Diseño <strong>de</strong> Circuitos Lógicos<br />

<strong>Digital</strong>es. Prentice Hall.<br />

6. SALCIC, Z. 1998. <strong>Digital</strong> Systems Design and Prototyping Using Field Programmable Logic. Kluwer<br />

Aca<strong>de</strong>mic Publishers.<br />

7. SMITH, D. J. HDL basic training: top-down chip <strong>de</strong>sign using Verilog and <strong>VHDL</strong>. 1996 EDN Magazine.<br />

http://209.67.241.58/reg/1996/102496/Df_04.htm<br />

8. VAN DEN BOUT, D. 1998. The Practical Xilinx � Designer LAB Book, Prentice Hall Inc. New York.<br />

9. WESTE, N.; ESHRAGHIAN, K. 1994. Principles of CMOS VLSI Design, A Systems Perspective. 2da<br />

Edición, Addison-Wesley Publishing Company.