You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

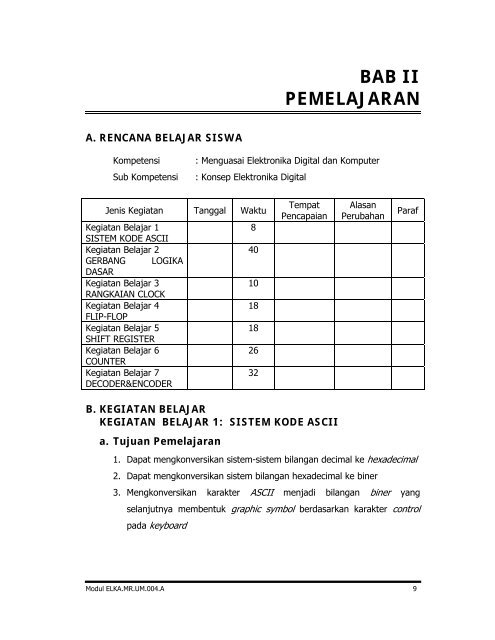

A. RENCANA BELAJAR SISWA<br />

BAB II<br />

PEMELAJARAN<br />

Kompetensi : Menguasai Elektronika Digital <strong>dan</strong> Komputer<br />

Sub Kompetensi : Konsep Elektronika Digital<br />

Jenis Kegiatan Tanggal Waktu<br />

Kegiatan Belajar 1<br />

SISTEM KODE ASCII<br />

Kegiatan Belajar 2<br />

GERBANG LOGIKA<br />

DASAR<br />

Kegiatan Belajar 3<br />

RANGKAIAN CLOCK<br />

Kegiatan Belajar 4<br />

FLIP-FLOP<br />

Kegiatan Belajar 5<br />

SHIFT REGISTER<br />

Kegiatan Belajar 6<br />

COUNTER<br />

Kegiatan Belajar 7<br />

DECODER&ENCODER<br />

8<br />

40<br />

10<br />

18<br />

18<br />

Tempat<br />

Pencapaian<br />

B. KEGIATAN BELAJAR<br />

KEGIATAN BELAJAR 1: SISTEM KODE ASCII<br />

a. Tujuan Pemelajaran<br />

26<br />

32<br />

Alasan<br />

Perubahan Paraf<br />

1. Dapat mengkonversikan sistem-sistem bilangan decimal ke hexadecimal<br />

2. Dapat mengkonversikan sistem bilangan hexadecimal ke biner<br />

3. Mengkonversikan karakter ASCII menjadi bilangan biner yang<br />

selanjutnya membentuk graphic symbol berdasarkan karakter control<br />

pada keyboard<br />

Modul ELKA.MR.UM.004.A 9

. Uraian Materi<br />

ASCII (American Standar Code For Information Interchange) adalah juga<br />

sering disebut dengan sandi ASCII yang sering digunakan untuk<br />

memproses sistem informasi, komunikasi, <strong>dan</strong> peralatan yang saling<br />

berhubungan biasanya berupa keypad (papan ketik) atau lebih lengkap<br />

disebut keyboard. Peraturan FCC memberikan para pengguna ASCII<br />

amatir agar dapat menyesuaikan pada ASCII yang diartikan oleh American<br />

National Standar Institute (ANSI) Standar X3.4-1968.ANSI telah membuat<br />

perbaikan menjadi X3.4-1977.ANSI yang menggunakan istilah yang<br />

berbeda misalnya dari dua pilihan output untuk graphic tertentu. ANSI<br />

adalah rekan usaha Internasional dengan Organisasi Internasional dalam<br />

memberlakukan standart ISO 646-1973 <strong>dan</strong> Internasional Alphabet no.5<br />

(IA5) yang secara spesifik direkomendasikan dalam CCITT (International<br />

Telegraph and Telephone Consultative Commitee). ASCII menyajikan<br />

sebuah karakter dengan 7 bit bilangan biner yang memungkinkan<br />

kombinasi 128 karakter yang berbeda. Dari 128 karakter ini 96 karakter<br />

diantaranya merupakan printable character (termasuk huruf besar <strong>dan</strong><br />

kecil). Sisa karakter yang lain sebanyak 32 buah digunakan untuk karakter<br />

khusus seperti carriage Return, Line Feed, Back Space, Delete.<br />

Tidak seperti (Bandot), ASCII telah lebih tinggi <strong>dan</strong> memiliki noise kasusu<br />

yang rendah dalam penulisannya. Sekumpulan Code ASCII dapat dilihat<br />

pada tabeh 1 berikut ini:<br />

Tabel 1<br />

Penempatan Character Code ASCII<br />

Bit<br />

Number<br />

6 0 0 0 0 1 1 1 1<br />

5 0 0 1 1 0 0 1 1<br />

4 0 1 0 1 0 1 0 1<br />

Hex 1 st 0 1 2 3 4 5 6 7<br />

3 2 1 0 2 nd<br />

0 0 0 0 0 NUL DLE SP 0 @ P ‘ p<br />

Modul ELKA.MR.UM.004.A 10

0 0 0 1 1 SOH DC1 ! 1 A Q a q<br />

0 0 1 0 2 STX DC2 “ 2 B R b r<br />

0 0 1 1 3 ETX DC3 # 3 C S c s<br />

0 1 0 0 4 EOT DC4 $ 4 D T d t<br />

0 1 0 1 5 ENQ NAK & 5 E U e u<br />

0 1 1 0 6 ACK SYN % 6 F V f v<br />

0 1 1 1 7 BEL ETB ‘ 7 G W g w<br />

1 0 0 0 8 BS CAN ( 8 H X h x<br />

1 0 0 1 9 HT EM ) 9 I Y i y<br />

1 0 1 0 A LF SUB * : J Z j z<br />

1 0 1 1 B VT ESC + ; K [ k {<br />

1 1 0 0 C FF FS ‘ < L \ l |<br />

1 1 0 1 D CR GS - = M ] m }<br />

1 1 1 0 E SO RS . > N ^ n ~<br />

1 1 1 1 F SI US / ? O _ o DEL<br />

ACK = acknowledge<br />

BEL = bell<br />

BS = backspace<br />

CAN = cancel<br />

CR = carriage return<br />

DC1 = device control 1<br />

DC2 = device control 2<br />

DC3 = device control 3<br />

DC4 = device control 4<br />

DEL = delete<br />

DLE =data link escape<br />

ENQ = enquiry<br />

EM = end of medium<br />

EOT = end of transmission<br />

ESC = escape<br />

ETB = end of block<br />

ETX = end of text<br />

Note : “1”= mark, “0”= space<br />

Bit 6 is the most significant bit (MSB)<br />

Bit 0 is tme least significant bit (LSB)<br />

FF = form feed<br />

FS = file separator<br />

GS =group separator<br />

HT = horizontal tab<br />

LF = line feed<br />

NAK = negative acknoweledge<br />

NUL = null<br />

RS = record separator<br />

SI = shift in<br />

SO = shift out<br />

SOH = start of heading<br />

SP = space<br />

STX = start of text<br />

SUB = substitute<br />

SYN = synchronous idle<br />

US = unit separator<br />

VT = vertical tab<br />

Nomor bit didalam table disusun sesuai pasangan gambar dari b6-b0.<br />

Dalam code internasional £, selalu menempati # <strong>dan</strong> $ mungkin untuk<br />

menandai kata uang internasional ¤<br />

Sementara pada awalnya misalnya pada terminal video display <strong>dan</strong><br />

teleprinter seperti teletype corp model 33, selalu diimplementasikan pada<br />

kenaiakan kasus huruf atau lambing. Mereka selalu menggambarkan<br />

kenaikan kasus huruf saat menerima kasus/huruf yanf lebih rendah. Dalam<br />

terminal CAPS LOCK, dalam keyboard mungkin dapat digunakan untuk<br />

mengubah semua huruf ke kenaikan kasus.<br />

Modul ELKA.MR.UM.004.A 11

Karakter Control:<br />

ASCII telah memiliki 32 karakter khusus yang berfungsi sebagi karakter<br />

control ditambah dengan karakter istimewa. Mereka tidak konsisten dalam<br />

menggunakan spesifikasi pada standart ANSI X3.4. Bagaimanapun ini kakan<br />

banyak membantu untuk mengetahui penggunaan sesuai standart.<br />

Terdapat 5 kelompok dalam rangkaian control yaitu:<br />

a. Logical Communication<br />

b. Device Control<br />

c. Information Separator<br />

d. Code Extention<br />

e. Physical Communication<br />

Dibawah ini adalah contoh penjelasan dari karakter control yang berbeda.<br />

Penjelasan ini dapat dibaca dari table yang sudah dilengkapi dengan<br />

karakter ASCII, Code Hexadecimal, Code biner <strong>dan</strong> symbol graphic sebagai<br />

berikut:<br />

Modul ELKA.MR.UM.004.A 12

ASCII Keyboard Decimal Hexadecimal Binary Graphic<br />

Char Char<br />

Symbol<br />

LOGICAL COMMUNICATION CONTROL<br />

SOH Control A 1 01 0000001 ⎡<br />

STX Control B 2 02 0000010 ⊥<br />

ETX Control C 3 03 0000011 ⎦<br />

ACK Control F 6 06 0000110 ∨<br />

ASCII<br />

Char<br />

Keyboard<br />

Char<br />

Decimal Hexadecimal Binary Graphic<br />

Symbol<br />

PHYSICAL COMMUNICATION<br />

NUL Control @ 0 00 0000000<br />

CAN Control x 24 18 0011000 Χ<br />

EM Control y 25 19 0011001 Φ<br />

SUB Control z 26 1A 0011010 ς<br />

DEVICE CONTROL<br />

BEL Control G 7 07 0000111<br />

BS Control H 8 08 0001000<br />

HT Control I 9 09 0001001 →<br />

VT Control K 11 0B 0001011 ↓<br />

INFORMATION SEPARATOR<br />

FS Control \ 28 1C 0011100<br />

GS Control | 29 1D 0011101<br />

RS Control ^ 30 1E 0011110<br />

US Control - 31 1F 0011111<br />

CODE EXTENTION<br />

SO Control N 14 0E 0001110<br />

SI Control O 15 0F 0001111<br />

ESC ESC 7 0B 0011011<br />

Keseimbangan (Parity)<br />

Saat a<strong>dan</strong>ya ke tidak tepatan penempatan ASCII disimpan 8 bit dengan<br />

menambahkan angka 0 sebagai bit bersignifikasi paling tinggi<br />

(diletakkan pada pada bit paling kiri). Sebagai contoh karakter R akan<br />

tersimpan sebagai 0101000, <strong>dan</strong> seterusnya. Bit tambahan ini sering<br />

digunakan untuk uji paritas. Penambahan ini mungkin untuk<br />

pemeriksaan keseimbangan/sama rata. Untuk membedakan data<br />

Modul ELKA.MR.UM.004.A 13

komunikasi <strong>dan</strong> pengertian parity dapat juga mengamankan data<br />

komunikasi.<br />

Code Tambahan (Code Extention)<br />

Dengan tambahan parity menjadi 8 bit, dapat digunakan sebagai balas<br />

tingkat code character. Pekerjaan yang sekarang dijalani untuk<br />

menghasilkan standar internasional dalam batas tingkat kumpulan code<br />

character. Untuk komunikasi teks yang akan memberikan sekumpulan<br />

tambahan karakter grafik.<br />

ASCII SERIAL TRANSMISSION<br />

Serial transmission dari karakter ASCII dapat menjadi penurunan bit<br />

pertama ke kenaikan bit yang paling penting (MSB) atau b0 menjadi b6<br />

ditambah dengan keseimbangan bit parity jika diperlukan.<br />

Tabel berikut ini merupakan tampilan kelengkapan perangkat karakter<br />

ASCII untuk melengkapai tabel diatas.<br />

ASCII Karakter ASCII Karakter ASCII Karakter ASCII Karakter<br />

000 NUL 032 Blank 064 @ 096<br />

001 SOH 033 ! 065 A 097 a<br />

002 STX 034 “ 066 B 098 b<br />

003 ETX 035 # 067 C 099 c<br />

004 EOT 036 $ 068 D 100 d<br />

005 ENQ 037 % 069 E 101 e<br />

006 ACK 038 & 070 F 102 f<br />

007 BEL 039 ‘ 071 G 103 g<br />

008 BS 040 ( 072 H 104 h<br />

009 HT 041 ) 073 I 105 i<br />

010 LF 042 * 074 J 106 j<br />

011 VT 043 + 075 K 107 k<br />

012 FF 044 ‘ 076 L 108 l<br />

013 CR 045 - 077 M 109 m<br />

014 SO 046 ‘ 078 N 110 n<br />

015 SI 047 / 079 O 111 o<br />

016 DLE 048 0 080 P 112 p<br />

017 DC1 049 1 081 Q 113 q<br />

Modul ELKA.MR.UM.004.A 14

ASCII Karakter ASCII Karakter ASCII Karakter ASCII Karakter<br />

018 DC2 050 2 082 R 114 r<br />

019 DC3 051 3 083 S 115 s<br />

020 DC4 052 4 084 T 116 t<br />

021 NAK 053 5 085 U 117 u<br />

022 SYN 054 6 086 V 118 v<br />

023 ETB 055 7 087 W 119 w<br />

024 CAN 056 8 088 X 120 x<br />

025 EM 057 9 089 Y 121 y<br />

026 SUB 058 : 090 Z 122 z<br />

027 ESC 059 ; 091 [ 123 {<br />

028 FS 060 < 092 \ 124 |<br />

029 GS 061 = 093 ] 125 }<br />

030 RS 062 > 094 ↑ 126 ~<br />

031 US 063 ? 095 _ 127 DEL<br />

Catatan:<br />

Karakter pertama <strong>dan</strong> terakhir adalah karakter control. Mereka tidak<br />

boleh dicetak.<br />

c. Rangkuman<br />

Code ASCII merupakan sandi yang paling penting. ASCII menyajikan 7<br />

bit bilangan biner, yang memungkinkan kombinasi 128 karakter yang<br />

berbeda. Dari 128 karakter yang berbeda ini 96 karakter diantaranya<br />

berupa printable character, <strong>dan</strong> 32 karakter pertama <strong>dan</strong> terakhir<br />

adalah control character. Pada tabel 1 diatas menunjukkan sandi ASCII<br />

lengkap yang disusun dalam sejumlah kolom <strong>dan</strong> baris. Sebagai contoh,<br />

karakter R terdapat pada kolom 101 <strong>dan</strong> baris 0010 sehingga sandi<br />

ASCII dari karakter R adalah 1010010. Dengan cara yang sama<br />

karakter carriage return (CR) mempunyai sandi 0001101. ASCII<br />

disimpan sebagai sandi 8 bit dengan menambakan satu angka 0<br />

sebagai bit significant paling tinggi. Bit tambahan ini sering dgunakan<br />

untuk uji prioritas. Karakter control pada ASCII dibedakan menjadi 5<br />

kelompok sesuai dengan penggunaan yaitu berturut-turut meliputi<br />

logical communication, Device control, Information separator, Code<br />

extention, <strong>dan</strong> physical communication. Code ASCII ini banyak dijumpai<br />

Modul ELKA.MR.UM.004.A 15

pada papan ketik (keyboard) computer atau instrument-instrument<br />

<strong>digital</strong>. Di pasaran terdapat sejumlah papan ketik yang keypad<br />

hexadecimal terdiri atas 16 kunci untuk 16 karakter hexadecimal yang<br />

sering digunakan pada sistem-sistem sederhana.<br />

d. Tugas<br />

Dari pembacaan pada tabel, buatlah daftar table yang terdiri atas:<br />

Kolom 1: Bilangan decimal 0 sampai dengan 64<br />

Kolom 2: Character ASCII<br />

Kolom 3: Bilangan Decimal<br />

Kolom 4: Bilangan binernya<br />

e. Test Formatif<br />

1. Sebutkan kegunaan dari kode ASCII!<br />

2. Kharakter control dalam kode ASCII dibedakan menjadi 5 kelompok.<br />

Sebutkan!<br />

3. Konversikan kode ASCII berikut menjadi bilangan biner!<br />

a. (127)10 = (7F)16 = 2<br />

b. (0E)16 = 2 = 10<br />

c. (1A)16 = 2 = 10<br />

f. Kunci Jawaban<br />

1. Kegunaan kode ASCII untuk memproses system informasi,<br />

komunikasi <strong>dan</strong> peralatan yang saling berhubungan yang biasanya<br />

berupa keyboard <strong>dan</strong> keypad.<br />

2. Karakter Control pada ASCII dibedakan menjadi:<br />

Modul ELKA.MR.UM.004.A 16

ASCII<br />

character<br />

4<br />

9<br />

G<br />

P<br />

R<br />

X<br />

M<br />

Nul<br />

ACK<br />

BEL<br />

FF<br />

CR<br />

CAN<br />

ESC<br />

a. Logical communication<br />

b. Device control<br />

c. Information separator<br />

d. Code extention<br />

e. Physical communication<br />

3. a. (127)10 = (7F)16 = (1111111)2<br />

b. (0E)16 = (0001110)2 = 1410<br />

c. (1A)16 = (0011010)2 = 2610<br />

g. Lembar Kerja<br />

Jika ditentukan:<br />

Perangkat character code ASCII seperti pada tabel dibawah ini.<br />

Lengkapilah tabel dibawah ini:<br />

Decimal Hexa Decimal<br />

Biner<br />

6 5 4 3 2 1 0<br />

Keterangan<br />

Modul ELKA.MR.UM.004.A 17

KEGIATAN BELAJAR 2: GERBANG LOGIKA DASAR<br />

a. Tujuan Pemelajaran<br />

1. Menjelaskan konsep dasar <strong>dan</strong> fungsi berbagai gerbang logika dasar<br />

dengan benar.<br />

2. Menjelaskan hukum-hukum penjalinan (Aljabar Boo lean) dengan<br />

bemar.<br />

3. Mengkombinasikan beberapa gerbang logika dasar dengan benar.<br />

4. Menjelaskan jenis-jenis IC untuk implementasi gerbang logika<br />

dengan benar.<br />

Modul ELKA.MR.UM.004.A 18

. Uraian Materi<br />

Gerbang logika merupakan dasar pembentuk system <strong>digital</strong>. Gerbang<br />

logika beroperasi pada bilangan biner 1 <strong>dan</strong> 0. Gerbang logika<br />

digunakan dalam berbagai rangkaian elektronik dengan system <strong>digital</strong>.<br />

Berkaitan dengan tegangan yang digunakan maka tegangan tinggi<br />

berarti 1 <strong>dan</strong> tegangan rendah adalah 0.<br />

Semua sistem <strong>digital</strong> disusun hanya menggunakan tiga gerbang yaitu:<br />

NOT, AND <strong>dan</strong> OR.<br />

1. Fungsi AND gate<br />

Fungsi AND dapat digambarkan dengan rangkaian listrik<br />

menggunakan saklar seperti dibawah ini:<br />

Keterangan:<br />

A & B adalah saklar<br />

Y adalah lampu<br />

Jika saklar dibuka maka berlogika 0, jika saklar ditutup disebut<br />

berlogika 1. Fungsi logika yang dijalankan rangkaian AND adalah<br />

sebagai berikut:<br />

1. Jika kedua saklar A & B dibuka maka lampu padam<br />

2. Jika salah satu dalam keadaan tertutup maka lampu padam<br />

3. Jika kedua saklar tertutup maka lampu nyala<br />

Simbol Gerbang AND Tabel Kebenaran<br />

A<br />

B<br />

A B<br />

Y=A.B<br />

=AB<br />

Y<br />

INPUT OUTPUT<br />

A B Y<br />

0 0 0<br />

0 1 0<br />

1 0 0<br />

1 1 1<br />

Modul ELKA.MR.UM.004.A 19

Karakteristik: Jika A da B adalah input, se<strong>dan</strong>gkan Y adalah Output,<br />

maka output gerbangnya AND berlogika 1 jika semua inputnya<br />

berlogika 1. Dan output berlogika 0 jika kedua atau salah satu<br />

inputnya berlogika 0.<br />

2. Fungsi OR gate<br />

Funsi OR dapat digambarkan dengan rangkaian seperti dibawah ini.<br />

Keterangan:<br />

A <strong>dan</strong> B =Saklar<br />

Y= lampu<br />

Jika saklar dibuka maka berlogika 0, jika saklar ditutup disebur<br />

berlogika 1.<br />

Simbol Gerbang OR Tabel kebenaran<br />

A<br />

B<br />

INPUT OUTPUT<br />

A B Y<br />

0 0 0<br />

0 1 1<br />

1 0 1<br />

1 1 1<br />

Karakteristik: Jika A <strong>dan</strong> B adalah input se<strong>dan</strong>gkan Y output maka<br />

output gerbang OR akan berlogika 1 jika salah satu atau kedua input<br />

adalah berlogika 1.<br />

3. Fungsi NOT gate<br />

Fungsi NOT dapat digambarkan dengan rangkaian seperti gambar<br />

dibawah ini:<br />

A<br />

B<br />

Y=A+B<br />

Y<br />

Modul ELKA.MR.UM.004.A 20

A<br />

Jika saklar dibuka maka berlogika 0,<br />

jika saklar ditutup disebut berlogika 1.<br />

Simbol Fungsi NOT Tabel Kebenaran<br />

INPUT OUTPUT<br />

A<br />

Y<br />

A<br />

0<br />

Y<br />

1<br />

1 0<br />

Karakteristik: Jika adalah input, output adalah kebalikan dari input.<br />

Artinya Jika input berlogika 1 maka output akan berlogika 0 <strong>dan</strong><br />

sebaliknya.<br />

4. Fungsi NAND gate<br />

NAND adalah rangkaian dari NOT AND. Gerbang NAND merupakan<br />

gabungan dari NOR <strong>dan</strong> AND digambarkan sebagai berikut:<br />

A<br />

B<br />

Menjadi:<br />

A<br />

B<br />

A<br />

B<br />

Y<br />

AND NOT<br />

NAND<br />

Y<br />

Y = AB<br />

Y = AB<br />

NAND sebagai sakelar<br />

Modul ELKA.MR.UM.004.A 21

Dari Gambar diatas dapat dibuat tabel kebenaran sebagai berikut:<br />

C Output<br />

A B Y<br />

0 0 1<br />

0 1 1<br />

1 0 1<br />

1 1 0<br />

Karakteristiknya: Jika A <strong>dan</strong> B input se<strong>dan</strong>gkan Y adalah output<br />

maka output gerbang NAND akan berlogika 1 jika salah satu<br />

inputnya berlogika 0. Dan output akan berlogika 0 jika kedua<br />

inputnya berlogika 1. Atau output gerbang NAND adalah komplemen<br />

output gerbang AND.<br />

5. Fungsi NOR gate<br />

NOR adalah singkatan dari NOT OR. Gerbang NOR merupakan<br />

gabungan dari gerbang NOT <strong>dan</strong> OR. Digambarkan sebagai berikut:<br />

A<br />

B<br />

menjadi:<br />

A<br />

B<br />

A B<br />

Y<br />

Y = A+B<br />

Y = A+B<br />

NOR dengan saklar<br />

Modul ELKA.MR.UM.004.A 22

Dari rangkaian diatas dapat dibuat tabel kebenaran sebagai berikut:<br />

Input Output<br />

A B Y<br />

0 0 0<br />

0 1 0<br />

1 0 0<br />

1 1 1<br />

Karakteristik: jika A <strong>dan</strong> B adalah input <strong>dan</strong> Y adalah output maka<br />

output gerbang NOR berlogika 1 jika semua input berlogika 1 <strong>dan</strong><br />

output akan berlogika 0 jika salah satu atau semua inputnya<br />

berlogika 0. Atau output gerbang NOR merupakan output gerbang<br />

OR<br />

6. Fungsi EX-OR (Exlusive OR)<br />

Gerbang X-OR akan memberikan output berlogika 1 jika jumlah<br />

logika jumlah logika 1 pada inputnya ganjil. Rangkaian EX-OR<br />

disusun dengan menggunkan gerbang AND, OR, NOT seperti<br />

dibawah ini.<br />

Simbol Gerbang EX-OR<br />

A<br />

B<br />

Y = A + B<br />

Dari gambar diatas dapat dibuat tabel kebenaran sebagai berikut:<br />

Input Output<br />

Y= A.B + A.B<br />

= A + B<br />

Modul ELKA.MR.UM.004.A 23

A B Y<br />

0 0 0<br />

0 1 1<br />

1 0 1<br />

1 1 0<br />

7. Fungsi EX-NOR<br />

Gerbang X-NOR akan memberikan output berlogika 0 jika jumlah<br />

logika 1 pada inputnya ganjil. Dan akan berlogika 1 jika kedua<br />

inputnya sama. Rangkaian EX-NOR disusun dengan menggunka<br />

gerbang AND, OR, NOT seperti dibawah ini.<br />

Simbol Gerbang EX-NOR<br />

A<br />

B<br />

Y = A + B<br />

Dari gambar diatas dapat dibuat tabel kebenaran sebagai berikut:<br />

Input Output<br />

A B Y<br />

0 0 1<br />

0 1 0<br />

1 0 0<br />

1 1 1<br />

8. Sifat-Sifat Aljabar Boolean<br />

Aljabar Boolean memuat variable <strong>dan</strong> simbul operasi untuk gerbang<br />

logika. Simbol yang digunakan pada aljabar Boolean adalah: (.)<br />

untuk AND, (+) untuk OR, <strong>dan</strong> ( ) untuk NOT. Rangkaian logika<br />

merupakan gabungan beberapa gerbang, untuk mempermudah<br />

penyeleseian perhitungan secara aljabar <strong>dan</strong> pengisian tabel<br />

kebenaran digunakan sifat-sifat aljabar Boolean:<br />

Modul ELKA.MR.UM.004.A 24

a. Teori IDENTITAS<br />

A.1 = A A+1 = 1<br />

A.0 = 0 A+0 = A<br />

A.A = A A+A = A<br />

A.A = A A+A = 1<br />

b. Teori KOMUTATIF<br />

A.B.C = C.B.A<br />

A+B+C = C+B+A<br />

c. Teori ASOSIATIF<br />

A.(B.C) = (A.B).C = A.B.C<br />

A + ( B + C ) = ( A + B ) + C = A + B + C<br />

d. Teori DISTRIBUTIF<br />

A.B + A.C = A (B+C)<br />

e. Teori DE MORGAN<br />

A . B = A + B<br />

A + B = A . B<br />

9. Kombinasi Gerbang Logika<br />

Untuk memenuhi kebutuhan akan input yang lebih dari 2 di dalam<br />

suatu rangkaian logika, maka digabungkan beberapa gerbang logika<br />

. Hal ini biasa dilakukan jika faktor delay tidak diperhitungkan.<br />

Contoh:<br />

a) Gerbang logika AND 3 input<br />

A<br />

B<br />

C<br />

banyaknya input.<br />

Kemungkkinan tabel<br />

kebenaran untuk<br />

inputnya yaitu 2<br />

dimana n adalah<br />

Modul ELKA.MR.UM.004.A 25<br />

Y

NOT<br />

A<br />

AND<br />

Tabel kebenaran AND 3 input<br />

Jadi 2 = 8<br />

INPUT OUTPUT<br />

A B C Y<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

1<br />

0<br />

0<br />

1<br />

0<br />

0<br />

0<br />

1<br />

1<br />

0<br />

1<br />

0<br />

0<br />

0<br />

1<br />

0<br />

1<br />

0<br />

1<br />

1<br />

0<br />

0<br />

1<br />

1<br />

1<br />

1<br />

b) Gerbang NAND sebagai gerbang universal<br />

Gerbang NAND disebut gerbang logika universal karena dapat<br />

digunakan untuk membuat gerbang logika yang lain, sehingga<br />

dapat meminimalkan penggunaan gerbang dasar untuk<br />

membentuk suatu gerbang logika tertentu.<br />

Rangkaian Ekivalen gerbang NAND<br />

JENIS GERBANG EKIVALEN<br />

A<br />

Modul ELKA.MR.UM.004.A 26

OR<br />

NOR<br />

EX-OR<br />

EX-NOR<br />

JENIS GERBANG EKIVALEN<br />

10. TEORI DE MORGAN<br />

Digunakan untuk mengubah bolak–balik dari bentuk minterm<br />

(bentuk penjumlahan dari pada hasil kali/SOP) ke maksterm<br />

(bentuk perkallian dari pada penjumlahan/POS) dari pernyataan<br />

Boolean.<br />

Teori De Morgan dapat ditulis:<br />

a. A + B = A . B<br />

Mengubah keadaan OR dasar menjadi AND dasar<br />

Modul ELKA.MR.UM.004.A 27

. A . B = A + B<br />

Mengubah keadaan OR dasar menjadi AND dasar<br />

Penyederhanaan fungsi logika dengan aljabar Boolean contoh:<br />

1. Y = A.B …………………………..Y = A + B = A + B<br />

2. Y = A + B ……………………….Y = A.B<br />

3. Y = AB + A.B + A.B<br />

Y = A + B + A.B + A.B<br />

Y = A + A.B + B + A.B<br />

Y = A(1+B) + B(1 + A)<br />

Y = A + B = A.B<br />

Penyederhanaan fungsi logika dengan sistem Sum Of Product (SOP)<br />

<strong>dan</strong> Product Of Sum (POS)<br />

1. Penyederhanaan dengan sistem SOP/penjumlahan dari pada hasil<br />

kali.<br />

Sifat: Untuk sistem SOP digunakan output 1<br />

Contoh:<br />

=<br />

=<br />

INPUT OUTPUT<br />

A B C Y<br />

0 0 0 1<br />

0 0 1 0<br />

0 1 0 0<br />

0 1 1 1<br />

1 0 0 0<br />

1 0 1 0<br />

1 1 0 1<br />

1 1 1 1<br />

Persamaan SOP<br />

Y = A.B.C + A.B.C + A.B.C + A.B.C<br />

Modul ELKA.MR.UM.004.A 28

A<br />

B<br />

C<br />

Gambar rangkaian:<br />

Penyederhanaan dengan aljabar Boolean<br />

Y = A.B.C + A.B.C + A.B.C + A.B.C<br />

Y = A.B.C + A.B.C + A.B.C + A.B.C<br />

Y = A.B (C+C) + A.B.C + A.B.C<br />

Y = A.B + A.B.C + A.B.C<br />

Penyederhanaan dengan POS/perkalian dari pada penjumlahan<br />

Sifat: Untuk sistem POS digunakan output 0<br />

Contoh:<br />

Input Output<br />

A B Y<br />

0 0 1<br />

0 1 1<br />

1 0 0<br />

1 1 0<br />

Persamaan POS: Y = ( A + B ) . ( A + B )<br />

Modul ELKA.MR.UM.004.A 29<br />

Y

11. Penyederhanaan fungsi logika dengan Karnaugh Map.<br />

Metoda Karnaugh Map adalah suatu teknik penyederhanaan fungsi<br />

logika denngan cara pemetaan K-Map terdiri dari kotak-kotak<br />

(bujur sangkar) yang jumlahnya tergantung dari jumlah variabel<br />

dari fungsi logika atau jumlah input dari rangkaian logika.<br />

Rumus menentukan jumlah kotak dalam K–Map<br />

N = 2 dimana N = jumlah kotak dalam K-Map<br />

N = banyaknya variabel/input<br />

Langkah-langkah pemetaan Karnaugh Map secara umum.<br />

1. Menyusun aljabar Boolean minterm (dari suatu taaabel<br />

kebenaran)<br />

2. Menggambarkan satuan dalam peta Karnaugh Map.<br />

3. Membuat kelompok dua-an, empat-an, delapan-an satuan <strong>dan</strong><br />

seterusnya dimana satuan tersebut berdekatan satu sama lain.<br />

4. Menghilangkan variabel-variabel dengan rumus bila suatu<br />

variabel <strong>dan</strong> inversinya terdapat didalam suatu kelompok<br />

lingkaran maka variabel tersebut dihilangkan.<br />

5. Meng-OR-kan variabel yang tersisa.<br />

a) Macam Karnaugh Map<br />

Contoh:<br />

a. Karnaugh Map dengan 2 variabel<br />

Input Output<br />

A B Y<br />

0 0 1<br />

0 1 0<br />

1 0 1<br />

1 1 1<br />

Langkah Pertama<br />

Modul ELKA.MR.UM.004.A 30

Y = A.B + A.B + A.B<br />

Langkah ke Dua<br />

A<br />

A<br />

A<br />

B<br />

B<br />

1<br />

B<br />

1 1<br />

Langkah ke Tiga<br />

A<br />

A<br />

A<br />

B<br />

B<br />

1<br />

1<br />

B<br />

1<br />

Langkah ke Empat<br />

Y = A. B + A.B + A.B<br />

Y = B ( A +A ) + AB<br />

Y = B + A.B<br />

Contoh:<br />

b. Karnaugh Map dengan 3 variabel<br />

INPUT OUTPUT<br />

A B C Y<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

1<br />

1<br />

0<br />

1<br />

0<br />

1<br />

0<br />

1<br />

1<br />

1<br />

1<br />

0<br />

0<br />

0<br />

1<br />

0<br />

1<br />

1<br />

Modul ELKA.MR.UM.004.A 31

1<br />

1<br />

1<br />

1<br />

Penyederhanaan dengan K-Map<br />

Langkah pertama:<br />

Modul ELKA.MR.UM.004.A 32<br />

0<br />

1<br />

Y=A.B.C+A.B.C+A.B.C+A.B.C+A.B.C<br />

Langkah kedua:<br />

C<br />

AB<br />

A B<br />

A B<br />

A B<br />

A B<br />

C<br />

1<br />

Langkah ketiga:<br />

C<br />

1<br />

1<br />

1<br />

1<br />

Penyederhanaan dengan Aljabar Boolean<br />

Y = A.B.C+ A.B.C+ A.B.C+ A.B.C+ A.B.C<br />

Y = B.C (A+A)+A.B (C+C)+ A.B.C<br />

Y = B.C+A.B+ A.B.C<br />

Y = B.C+B(A+AC)<br />

Y = B.C+B(A+C)<br />

Y = B.C+A.B+B.C<br />

Y = A.B+C(B+B)<br />

Y = A.B+C<br />

c. Karnaugh Map dengan 4 variabel<br />

0<br />

1

Contoh:<br />

INPUT OUTPUT<br />

A B C D Y<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

0<br />

1<br />

1<br />

0<br />

0<br />

1<br />

0<br />

0<br />

0<br />

0<br />

1<br />

1<br />

1<br />

0<br />

1<br />

0<br />

0<br />

0<br />

0<br />

1<br />

0<br />

1<br />

1<br />

0<br />

1<br />

1<br />

0<br />

1<br />

0<br />

1<br />

1<br />

1<br />

1<br />

1<br />

0<br />

0<br />

0<br />

0<br />

1<br />

0<br />

0<br />

1<br />

1<br />

1<br />

0<br />

1<br />

0<br />

0<br />

1<br />

0<br />

1<br />

1<br />

1<br />

1<br />

1<br />

0<br />

0<br />

0<br />

1<br />

1<br />

0<br />

1<br />

1<br />

1<br />

1<br />

1<br />

0<br />

0<br />

1<br />

1<br />

1<br />

1<br />

1<br />

Penyelesaian:<br />

Penyederhanaan dengan Karnaugh Map<br />

Langkah pertama:<br />

Y = A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D + A.B.C.D +<br />

A.B.C.D + A.B.C.D + A.B.C.D<br />

Langkah kedua:<br />

AB<br />

A B<br />

A B<br />

A B<br />

CD<br />

CD<br />

CD<br />

1<br />

1<br />

1<br />

CD<br />

1<br />

1<br />

1<br />

CD<br />

1<br />

Modul ELKA.MR.UM.004.A 33

A B<br />

Langkah ketiga:<br />

1<br />

Penyederhanaan dengan Aljabar Boolean:<br />

1<br />

Y = A.B.C.D+ A.B.C.D+ A.B.C.D+ A.B.C.D+ A.B.C.D+ A.B.C.D+<br />

A.B.C.D<br />

+ A.B.C.D+ A.B.C.D<br />

Y = A.B.D(C+C)+ A.B.C.D+A.B.C(D+D)+ A.B.D(C+C)+ A.B.D(C+C)<br />

Y = A.B.D+ A.B.C.D+ A.B.C+ A.B.D+ A.B.D<br />

Y = B.D(A+A)+A.B(C+CD)+ A.B.D<br />

Y = B.D+A.B(C+D)+ A.B.D<br />

Y = B.D+A.B.C+ A.B.D+ A.B.D<br />

Y = B.D+ A.B.C+B.D(A+A)<br />

Y = B.D+ A.B.C+B.D<br />

Y = D(B+B)+ A.B.C<br />

Y = D+ A.B.C<br />

Variasi pelingkaran yang tidak biasa<br />

a. Tidak dapat disederhanakan b. Satu variabel dapat dihilangkan<br />

1 1<br />

1<br />

1 1<br />

c. Dua variabel dapat dihilangkan<br />

1 1 1 1<br />

1 1 1 1<br />

12. Aplikasi Gerbang Logika Dasar<br />

Modul ELKA.MR.UM.004.A 34

Contoh: Sebagai rangkaian ARITMATIKA BINER yang dapat<br />

melakukan Operasi aritmatik penjumlahan (+) <strong>dan</strong> pengurangan (-<br />

)<br />

a) Half Adder<br />

Adalah suatu rangkaian penjumlah sistem bilangan biner yang<br />

paling sederhana. Rangkaian ini memiliki 2 terminal input <strong>dan</strong> 2<br />

terminal output yang disebut Summary Out (Sum) <strong>dan</strong> Carry<br />

Out (Carry).<br />

Gambar rangkaian logika untuk Half Adder Simbol<br />

A<br />

B<br />

Sum<br />

A<br />

H A<br />

Sum<br />

Tabel Kebenarannya:<br />

Carry<br />

B C<br />

INPUT OUTPUT<br />

Persamaan logika:<br />

A B SUM CARRY Sum = A.B+A.B<br />

0<br />

0<br />

0<br />

1<br />

0<br />

1<br />

0<br />

0<br />

Carry = A.B<br />

1 0 1 0<br />

1 1 0 1<br />

b) Full Adder<br />

Adalah penjumlah lengkap (penuh) yang memiliki 3 input A, B,<br />

Carry Input (Cin) dengan 2 output Sum <strong>dan</strong> Carry Output<br />

(Cout=Co).<br />

Gambar rangkaian logika untuk Full Adder<br />

Modul ELKA.MR.UM.004.A 35

Carry in<br />

A<br />

B<br />

Simbol<br />

Cin<br />

A<br />

B<br />

Tabel Kebenarannya:<br />

INPUT OUTPUT<br />

A B Cin Sum Co<br />

0 0 0 0 0<br />

0 0 1 1 0<br />

0 1 0 1 0<br />

0 1 1 0 1<br />

1 0 0 1 0<br />

1 0 1 0 1<br />

1 1 0 0 1<br />

1 1 1 1 1<br />

Persamaan logika:<br />

F A<br />

Sum = A.B.C+ A.B.C+ A.B.C+ A.B.C<br />

Co = A.B.C+ A.B.C+ A.B.C+ A.B.C<br />

c) Half Subtractor<br />

Sum<br />

Carry out<br />

Adalah suatu rangkaian pengurang sistem bilangan biner yang<br />

paling sederhana, ini memiliki 2 input <strong>dan</strong> 2 output yang<br />

disebut differensi (Di) <strong>dan</strong> Borrow (Bo).<br />

Gambar rangkaian logika untuk Half Subtractor<br />

Modul ELKA.MR.UM.004.A 36<br />

Sum<br />

Co

A<br />

B<br />

Simbol<br />

A<br />

B<br />

Tabel Kebenarannya:<br />

Modul ELKA.MR.UM.004.A 37<br />

Di<br />

Bo<br />

INPUT OUTPUT<br />

A B Di Bo<br />

0 0 0 0<br />

0 1 1 1<br />

1 0 1 0<br />

1 1 0 0<br />

Persamaan logika:<br />

Di = A.B+A.B<br />

= A + B<br />

Bo = A.B<br />

H S<br />

d) Full Subtractor<br />

Adalah rangkaian pengurang biner yang lengkap (penuh).<br />

Rangkaian ini memliki 3 terminal input <strong>dan</strong> 2 terminal output,<br />

yaitu Borrow <strong>dan</strong> Differensi.<br />

Gambar rangkaian logika untuk Full Subtractor:<br />

Di<br />

Bo

A<br />

B<br />

Bin<br />

Simbol<br />

A<br />

B<br />

Bin<br />

Tabel kebenarannya:<br />

INPUT OUTPUT<br />

A B Bin Di Bo<br />

0 0 0 0 0<br />

0 0 1 1 1<br />

0 1 0 1 1<br />

0 1 1 0 1<br />

1 0 0 1 0<br />

1 0 1 0 0<br />

1 1 0 0 1<br />

1 1 1 1 1<br />

Persamaan logikanya:<br />

F S<br />

Di = A.B.C+ A.B.C+ A.B.C+ A.B.C<br />

Bo = A.B.C+ A.B.C+ A.B.C+ A.B.C<br />

13. Keluarga IC Digital<br />

Modul ELKA.MR.UM.004.A 38<br />

Di<br />

Bo<br />

Bo<br />

Di

Perkembangan teknologi elektronik diawali dengan penggunaan<br />

Tabung hampa sebagai bagian pokok suatu alat elektronik.<br />

Kemudian temukanlah Transistor sebagai pengganti Tabung<br />

hampa. Perkembangan selanjutnya adalah munculnya rangkaian<br />

terpadu (Integrated Circuit) yang mengkombinasikan berbagai<br />

komponen bipolar (resistor, transistor) dalam satu chip.<br />

Berdasarkan kepadatan komponen keluarga IC dibagi menjadi 4<br />

kelompok yaitu:<br />

1. SSI ( Small Scale Integration)<br />

2. MSI ( Medium Scale Integration)<br />

3. LSI ( Large Scale Integration )<br />

4. VLSI ( Very Large Scale Integration )<br />

Berdasarkan penggunaan, IC dibagi menjadi 2 keluarga besar yaitu<br />

keluarga IC analog <strong>dan</strong> keluarga IC <strong>digital</strong>. Keluarga IC <strong>digital</strong><br />

lebih umum digunakan mengingat berbagai macam peralatan telah<br />

beroperasi secara <strong>digital</strong>.<br />

Keluarga IC <strong>digital</strong> sendiri dibuat dengan menggunakan teknologi<br />

semikonduktor (MOS = Metal Oxide Semiconductor) <strong>dan</strong> teknologi<br />

bipolar.<br />

Macam keluarga bipolar adalah<br />

1. RTL (Resistor Transistor Logic)<br />

2. DTL (Diode Transistor Logic)<br />

3. TTL (Transistor Transistor Logic)<br />

4. ECL (Emitter Coupled Logic)<br />

5. HTL (High Treshold Logic)<br />

6. IIL (Integrated Injection Logic)<br />

Macam keluarga Unipolar ( MOS ) adalah<br />

1. P MOS (P- Channel Metal Oxide Semikonductor)<br />

2. N MOS (N- Channel Metal Oxide Semikonductor)<br />

Modul ELKA.MR.UM.004.A 39

3. C MOS (Complementary Channel Metal Oxide Semikonductor)<br />

14. Keluarga IC TTL<br />

IC Bipolar yang banyak dijumpai di pasaran adalah IC TTL<br />

(Transistor Transistor Logic) yang terkenal dengan seri 74XX atau<br />

74XXX. Keluarga IC TTL digunakan paling luas pada rangkaian<br />

logika. IC TTL dibuat dalam variasi yang luas dari rangkaian<br />

terpadu MSI <strong>dan</strong> SSI. Peningkatan dalam rangkaian logika terus<br />

berkembang. Terlebih pada keluarga TTL. Enam IC TTL berikut<br />

adalah tersedia saat ini dari National Semiconductor Corporation.<br />

1. Logika TTL Standar<br />

2. Logika TTL daya rendah<br />

3. Logika TTL Schottky daya rendah<br />

4. Logika TTL Schottky<br />

5. Logika TTL Schottky daya rendah maju<br />

6. Logika TTL Schottky maju<br />

15. Rangkaian Terpadu CMOS<br />

Complementary Metal Oxide Semikonductor (CMOS) menjadi<br />

terkenal sejak tahun 1968 <strong>dan</strong> berkembang dengan cepat dengan<br />

seri 40XX atau 40XXX. Keuntungan IC CMOS dibanding TTL adalah<br />

tingkat derau yang rendah <strong>dan</strong> fungsi yang digunakan banyak<br />

jenisnya. IC Logika jenis C MOS juga mempunyai keluarga yang<br />

tidak sedikit. Namun jumlahnya tidak sebanyak IC TTL. Berbeda<br />

dengan IC TTL yang bekerja dengan tegangan supply 5 volt. IC<br />

CMOS dapat beroperasi pada berbagai tegangan supply DC.<br />

Tegangan supplynya bisa mencapai 15 volt. Tetapi CMOS<br />

mempunyai kecepatan kerja yang lebih rendah daripada TTL.<br />

Setelah IC TTL <strong>dan</strong> IC CMOS, muncul IC-IC logic PLD (Programmable<br />

Logic Device). Kelebihan PLD adalah sifatnya yang programable<br />

Modul ELKA.MR.UM.004.A 40

karena mengandung jenis <strong>dan</strong> jumlah gerbang lebih banyak pada<br />

tiap-tiap chip nya. Pemakaian PLD dapat mengurangi jumlah chip<br />

yang digunakan. Yang termasuk jenis IC PLD antara lain sebagai<br />

berikut:<br />

a. PLA (Programmable Logic Array)<br />

Berisi sejumlah gerbang AND, OR, NOT, yang masukan <strong>dan</strong><br />

keluarannya dapat kita hubungkan sehingga membentuk<br />

rangkaian yang diinginkan.<br />

b. PAL (Programmable AND-Array Logic)<br />

c. GAL (Generic Array Logic)<br />

d. PALCE (PAL Configurable and Erasable)<br />

Yang koneksinya dapat diprogram <strong>dan</strong> dihapus berulang kali. GAL<br />

<strong>dan</strong> PALCE dilengkapi dengan flip-flop yang memudahkan kita<br />

untuk menyusun rangkaian logika sekuensial seperti Counter <strong>dan</strong><br />

Shift Register.<br />

e. FPGA (Field Programmable Gate Array)<br />

c. Rangkuman<br />

Merupakan jenis PLD terbaru yang mulai populer saat ini. FPGA<br />

mempunyai beberapa kelebihan, diantaranya adalah jenis <strong>dan</strong><br />

jumlah gerbangnya yang sangat banyak (ribuan hingga ratusan<br />

ribu). Kecepatannya sangat tinggi, mudah diprogram <strong>dan</strong> dapat<br />

diprogram berkali-kali.<br />

Gerbang (gate) dalam rangkaian logika merupakan fungsi yang<br />

menggambarkan hubungan antara masukan <strong>dan</strong> keluaran. Untuk<br />

menyatakan gerbang-gerbang tersebut digunakan simbol-simbol<br />

tertentu. Untuk menunjukan prinsip kerja tiap gerbang (rangkaian<br />

logika yang lebih kompleks) dapat digunakan beberapa cara. Cara yang<br />

umum dipakai antara lain adalah tabel kebearan (truth table) <strong>dan</strong><br />

Modul ELKA.MR.UM.004.A 41

diagram waktu (timing chart). Karena merupakan rangkaian <strong>digital</strong>,<br />

tentu saja level kondisi yang ada dalam tabel atau diagram waktu hanya<br />

2 macam yaitu logika 0 (low atau false) <strong>dan</strong> logika 1 (high atau true).<br />

Jenis gerbang yang dipakai dalam rangkaian logika cukup banyak .<br />

Namun semuanya disusun atas kombinasi dari tiga gerbang dasar.<br />

Ketiga gerbang dasar itu adalah gerbang AND, OR <strong>dan</strong> NOT. Seperti<br />

contoh sebelumnya, gerbang AND identik dengan rangkaian seri dari<br />

beberapa saklar (yang berfungsi sebagai masukan) <strong>dan</strong> sebuah lampu<br />

(yang berfungsi sebagai keluaran). Pada rangkaian seri, lampu hanya<br />

dapat menyala (berlogika 1) jika semua saklar dalam keadaan tertutup<br />

(berlogika 1). Jika ada satu saklar (berlogika 0), lampu akan padam<br />

(berlogika 0).<br />

Dengan penggambaran diatas gerbang AND memiliki minimal 2<br />

masukan <strong>dan</strong> hanya satu keluaran. Gerbang OR identik dengan<br />

rangkaian paralel dari beberapa saklar. Pada rangkaian paralel, lampu<br />

sudah dapat menyala (berlogika 1), jika salah satu saklar ditutup<br />

(berlogika 1). Lampu hanya padam (berlogika 0), jika semua saklar<br />

dalam kondisi terbuka (berlogika 0). Jadi gerbang OR juga memiliki<br />

minimal 2 masukan <strong>dan</strong> hanya satu keluaran.<br />

Gerbang NOT sedikit berbeda dengan 2 gerbang sebelumnya. Ia hanya<br />

memiliki satu masukan <strong>dan</strong> satu keluaran. Jika masukan berlogika,<br />

keluaranya akan berlogika 0. Sebaliknya jika masukan berlogika 0,<br />

keluaranya akan berlogika 1. Kaarena itulah gerbang NOT sering<br />

disebut sebagai gerbang pembalik (inverter) logika.<br />

Dalam bentuk nyata rangkaian dapat disusun dari sebuah relay dengan<br />

kontak NC (Normally Closed/dalam keadaan normal tertutup) yang<br />

kontaknya tertutup saat arus listrik tidak melalui kumparan relay. Saat<br />

saklar dibuka (berlogika 0), kontak relay NC akan tertutup, sehingga<br />

arus listrik mengalir ke lampu <strong>dan</strong> membuatnya menyala (berlogika 1).<br />

Modul ELKA.MR.UM.004.A 42

Sebaliknya saat di tutup (berlogika 1), kumparan relay yang dialiri arus<br />

akan menarik kontak NC <strong>dan</strong> membuatnya terbuk. Akibatnya tidak ada<br />

arus yag mengalir ke lampu <strong>dan</strong> lampu menjadi padam (berlogika 0).<br />

Ketiga gerbang tersebut diatas dapat digabung-gabungkan menjadi<br />

gerbang lain, misalnya gerbang NAND, NOR, EX-OR, EX-NOR <strong>dan</strong> lain<br />

sebagaiya. Untuk rangkaian yang lebih kompleks, gerbang-gerbang<br />

dasar dapat disusun menjadi rangkaian Adder (penjumlah),<br />

Demultiplekser (pengubah data dari serial input menjadi paralel output,<br />

Multiplekser (pengubah data dari paralel input menjadi serial output).<br />

Selain itu rangkaian logika juga dapat di implementasikan dalam bentuk<br />

IC (Integrated Circuit) dalam jenis TTL (Transistor-transistor Logik)<br />

maupun CMOS (Complementary Metal Oxide Semikonduktor). Tiap-tiap<br />

anggota keluarga mempunyai konfigurasi sendiri-sendiri. Misalnya IC<br />

TTL 7404 mengandung 6 gerbang NOT, IC TTL 7432 mengandung 4<br />

gerbang OR. Selain gerbang-gerbang tunggal semacam itu ada juga yag<br />

konfigurasinya lebih komplek <strong>dan</strong> berisi rangkaian-rangkaian seperti<br />

Flip-flop, Counter, Encoder, Decoder, yang masing-masing mempunyai<br />

banyak varian dengan masing-masing spesifikasinya.<br />

d. Tugas<br />

1. Buatlah tabel kebenaran untuk gerbang AND 3 input?<br />

2. Buktikan persamaan Boolean dengan tabel kebenaranya untuk<br />

persamaan A . B = A + B?<br />

3. Bedakan antara gerbang NAND dengan gerbang NOR?<br />

4. Sederhanakan persamaan dibawah ini dengan menggunakan peta<br />

Karnaugh Map <strong>dan</strong> Aljabar Boolean:<br />

Y =A B C D + A B C D + A B C D + A B C D + A B C D + A B C D+A<br />

B C D<br />

5. Perhatikan <strong>dan</strong> analisalah rangkaian berikut:<br />

Modul ELKA.MR.UM.004.A 43

A<br />

B<br />

6. Rencanakan sebuah Half Adder dengan menggunakan gabungan<br />

gerbang logika dasar?<br />

Modul ELKA.MR.UM.004.A 44<br />

Y1<br />

Y2<br />

7. Jumlahkan data biner 1 1 0 1 dengan 0 1 1 0?<br />

8. Sebutkan 3 jenis IC TTL lengkap dengan kharakteristiknya masing-<br />

masing?<br />

9. Seb utkan 5 buah tipe dari IC TTL yang merupakan implementasi<br />

gerbang logika dasar!<br />

10. Sebutkan perbedaan antara IC TTL dengan CMOS?<br />

e. Test Formatif<br />

1. Perhatikan gambar dibawah ini:<br />

S1<br />

S2<br />

S3<br />

Jelaskan prinsip kerjanya <strong>dan</strong> fungsi logika apa yang dijalankan?<br />

2. Dengan menggunakan sifat-sifat Aljabar Boolean buktikan bahwa<br />

output dari rangkaian ini adalah Y = A + B<br />

A<br />

B<br />

Y

3. Bagaimanakah deretan pulsa yang terlihat pada keluaran gerbang<br />

EX-OR gambar dibawah ini:<br />

A 01100111<br />

B 11000100<br />

C 00101101<br />

f. Kunci Jawaban<br />

Modul ELKA.MR.UM.004.A 45<br />

Y<br />

1. Prinsip kerjanya:jika S1 =terbuka ;S2=S3=tertutup maka lampu<br />

akan menyala jika salah satu saklar atau semua saklar dalam<br />

keadaan tertutup. Sebaliknya lampu akan padam jika semua saklar<br />

dalam keadaan terbuka. Maka rangkaian tersebut melakukan fungsi<br />

gerbang OR.<br />

2. Pembuktian:<br />

Y = A.A.B.B.AB<br />

Y = A.AB + B.AB<br />

Y = A.AB +B.AB<br />

Y = A(A+B) +B(A+B)<br />

Y = AA + A.B +B.A + BB<br />

Y = A.B + A.B<br />

Y = A + B (terbukti)<br />

3. Deretan angka biner yang terlihat pada keluaran gerbang EX-OR<br />

adalah<br />

Y = 101011000<br />

g. Lembar Kerja<br />

Judul: GERBANG LOGIKA DASAR<br />

Alat <strong>dan</strong> bahan<br />

1. Power supply 5 volt DC 1buah<br />

2. Trainer Digital 1buah

3. IC TTL tipe7400 (NAND gate) 1buah<br />

4. IC TTL tipe7402 (NOR gate) 1buah<br />

5. IC TTL tipe7404 (NOT gate) 1buah<br />

6. IC TTL tipe7408 (AND gate) 1buah<br />

7. IC TTL tipe7432 (OR gate) 1buah<br />

8. IC TTL tipe7486 (Ex-OR gate) 1buah<br />

9. Jumper secukupnya<br />

Langkah kerja<br />

1. Siapkan power supply 5 volt DC<br />

2. Hubungkan terminal Vcc dari semua modul pada tegangan 5 volt<br />

DC<br />

3. Hubungkan terminal ground dari semua modul<br />

4. Buatlah rangkaian gerbang seperti gambar 1<br />

5. Berikan kondisi logik sesuai pada tabel 1<br />

6. Catat hasilnya pada kolom output<br />

Tabel 1 Gambar 1<br />

INPUT OUTPUT<br />

A B Y<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

7. Ulangi langkah kerja 4 <strong>dan</strong> 5 untuk rangkaian gerbang logika yang<br />

lain.<br />

i. OR gate<br />

Tabel 2<br />

INPUT OUTPUT<br />

A B Y<br />

A<br />

B<br />

Gambar 2<br />

0 0<br />

0 1<br />

Modul ELKA.MR.UM.004.A 46<br />

A<br />

B<br />

Y

1<br />

1<br />

0<br />

1<br />

ii. NOT gate<br />

Tabel 3. Gambar 3<br />

INPUT OUTPUT<br />

A Y<br />

0<br />

1<br />

iii. NAND gate<br />

Tabel 4 Gambar 4<br />

INPUT OUTPUT<br />

A B Y<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

iv. NOR gate<br />

Tabel 5 Gambar 5<br />

INPUT OUTPUT<br />

A B Y<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

v. Ex-OR gate<br />

Tabel 6 Gambar 6<br />

INPUT OUTPUT<br />

A B Y<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

Modul ELKA.MR.UM.004.A 47<br />

A<br />

A<br />

B<br />

A<br />

B<br />

A<br />

B<br />

Y<br />

Y<br />

Y<br />

Y

vi. Ex-NOR gate<br />

Tabel 7<br />

A<br />

Gambar 7<br />

INPUT OUTPUT<br />

B<br />

A B Y<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

8. Buatlah kesimpulan <strong>dan</strong> laporan dari hasil praktek yang telah<br />

dilakukan!<br />

KEGIATAN BELAJAR 3: RANGKAIAN CLOCK<br />

a. Tujuan Pemelajaran<br />

1. Merangkai rangkaian clock dengan benar.<br />

2. Menjelaskan prinsip kerja <strong>dan</strong> fungsi rangkaian clock dengan benar.<br />

b. Uraian Materi<br />

Rangakaian clock berfungsi untuk pembentuk/membangkitkan<br />

pulsa/gelombang kotak secara terus-menerus <strong>dan</strong> rangkaian ini tidak<br />

mempunyai kondisi stabil/setimbang. Rangkaian clock termasuk<br />

golongan Astabil Multivibrator dengan IC 555. Output rangkaian clock<br />

Modul ELKA.MR.UM.004.A 48<br />

Y

digunakan untuk input rangkaian-rangkaian logika yang sekuensial<br />

(berhubungan dengan waktu). Yang termasuk rangkaian logika<br />

sekuensial contohnya: Flip-Flop, Shift Register, <strong>dan</strong> Counter. Adapun<br />

fungsi rangkaian clock yaitu, untuk mengatur jalannya data dalam<br />

penggeseran ke kanan atau ke kiri, maupun dalam<br />

perhitungan/pencacahan bilangan biner. Yang dimaksud rangkaian<br />

Astabil Multivribator Adalah multivribator yang tidak stabil tegangan<br />

output-nya (tegangan pengeluarannya berubah-ubah) tanpa a<strong>dan</strong>ya<br />

sinyal masukan yang diberikan. Rangakaian clock dengan IC 555 besrta<br />

pulsa-pulsa pada pin 3 <strong>dan</strong> pin 6 ditunjukkan pada gambar ini<br />

Vout<br />

2<br />

3<br />

4<br />

R<br />

TRIG<br />

O<br />

555<br />

8<br />

U7<br />

VCC<br />

1<br />

D<br />

TH<br />

CTL<br />

GND<br />

7<br />

6<br />

5<br />

0.01uF<br />

Gambar 1<br />

Cara kerja rangkaian diatas<br />

+VCC<br />

RA<br />

RB<br />

C<br />

• Pada saat C diisi tegangan ambang naik melebihi + (2/3) Vcc.<br />

• Kini Kapasitor C dikosongkan melalui Rb oleh karena itu tetapan<br />

waktu pengosongan dapat ditentukan dengan rumus T = Rb x C.<br />

• Bila egangan C sudah turun sedikit sebesar + (Vcc/3) maka keluaran<br />

menjadi tinggi.<br />

Pewaktu IC 555 mempunyai tegangan yang naik <strong>dan</strong> turun secara<br />

exponensial. Keluarannya berbentuk gelombang segi empat. Karena<br />

tetapan waktu pengisian lebih lama daripada tetapan waktu<br />

pengosonngan, maka keluarannya tidak simetri. Keadaan keluaran yang<br />

tinggi lebih lama dari keadaan keluaran yang rendah. Untuk dapat<br />

Modul ELKA.MR.UM.004.A 49

menentukan ketidak simetrian ssuatu pulsa keluaran yang dihasilkan<br />

oleh rangkaian multivibrator jenis astabil ini dipergunakan suatu siklus<br />

kerja yang dirumuskan sebagai berikut:<br />

W = 0.693 (RA + Rb ).C<br />

t = 0.693 . Rb. C<br />

T = W + t<br />

Dimana : W = lebar pulsa ; T = waktu periode<br />

Besarnya frekuensi ditentukan oleh<br />

1<br />

F = ( dimana T = detik ; F = Hertz )<br />

T<br />

c. Rangkuman<br />

Astabil Multivibrator atau pembentuk pulsa atau generator pulsa<br />

merupakan rangkaian yang membangkitkan sinyal secara terus-menerus<br />

pada keluarannya tanpa a<strong>dan</strong>ya sinyal masukan dari rangkaian.<br />

Rangkaian ini juga sering dinamakan dengan rangkaian cloc. Frekuensi<br />

pulsa yang dihasilhan tergantung oleh besarnya C, Resistor RA, Rb.<br />

Untuk menentukan periode T ditentukan oleh lebart pulsa W <strong>dan</strong> t.<br />

d. Tugas<br />

1. Definisikan rangkaian clock?<br />

2. Sebutkan fungsi rangkaian clock?<br />

3. Jika periode waktu T = 0.1 milidetik, Hitung besanya frekuensi?<br />

4. Periode T ditentukan oleh komponen apa saja? sebutkan!<br />

e. Test Formatif<br />

1. Gambar <strong>dan</strong> terangkan prinsip kerja rangkaian clock dengan<br />

rangkaian IC 555?<br />

f. Kunci Jawaban<br />

Modul ELKA.MR.UM.004.A 50

220<br />

2<br />

3<br />

4<br />

R<br />

TRIG<br />

O<br />

555<br />

8<br />

U7<br />

VCC<br />

CTL<br />

GND<br />

1<br />

D<br />

TH<br />

7<br />

6<br />

5<br />

0.1uF<br />

VCC=6V<br />

10k<br />

10k<br />

4.7uF<br />

Prinsip kerja:<br />

Pada waktu pin 2 <strong>dan</strong> pin 6 berada dibawah VLT = 1/3 Vcc,sehingga kaki<br />

3 (keluaran) menjadi tinggi. Kapasitor C mengisi, melalui Ra <strong>dan</strong> Rb.<br />

Sampai Vc mencapai harga VUT, yaitu sebesar 2/3 Vcc, maka keluaran<br />

kaki 3 menjadi rendah. Kapasitor C mengosongkan muatannya melalui<br />

Rb ke kaki 6. Sampai harga Vc menjadi tinggi. Sehingga kejadian seperti<br />

di atas akan terulang kembali. Kejadian akan berulang terus, dengan<br />

frekuensi ditentukan sebagai berikut:<br />

1<br />

f =<br />

T<br />

1,<br />

4<br />

f =<br />

( Ra + 2Rb).<br />

C<br />

g. Lembar Kerja<br />

Judul: Rangkaian Clock (Astabil Multivibrator)<br />

Alat <strong>dan</strong> bahan<br />

1. IC pewaktu 555<br />

2. CRO<br />

3. Batteray 5 volt (catu daya )<br />

4. Resistor Ra = Rb = 10 K Ω , R = 220 Ω<br />

5. Condensator 0,1 μ F , 1 μ F , 4,7 μ F , 10 μ F , 47 μ F , 100 μ F .<br />

6. LED warna merah<br />

7. Breadboard<br />

8. Kabel penghubung<br />

Langkah kerja<br />

Modul ELKA.MR.UM.004.A 51

1. Siapkan alat <strong>dan</strong> bahan yang diperlukan.<br />

2. Susunlah rangkaian seperti gambar berikut:<br />

220<br />

2<br />

3<br />

4<br />

R<br />

TRIG<br />

O<br />

555<br />

8<br />

U7<br />

VCC<br />

1<br />

D<br />

TH<br />

CTL<br />

GND<br />

7<br />

6<br />

5<br />

0.1uF<br />

VCC=6V 5V<br />

3. Hubungkan catu daya 5 volt DC, kemudian amatilah apa yang terjadi<br />

pada LED (pin 3 sebagai output).<br />

4. Amatilah dengan CRO untuk bentuk gelombang pada pin 3 <strong>dan</strong> pin 6<br />

5. Gambarlah bentuk gelombang tersebut <strong>dan</strong> catat harga W <strong>dan</strong> T<br />

Modul ELKA.MR.UM.004.A 52<br />

10k<br />

10k<br />

4.7uF<br />

dalam satuan detik, serta harga amplitudo dalam satuan Vpp.<br />

6. Ulangilah percobaan ini dengan menggantikan kondensator C yang<br />

lain, kemudian melaksanakan langkah 4 <strong>dan</strong> 5.<br />

7. Kembalikanlah peralatan <strong>dan</strong> bahan ke tempat semula.<br />

8. Buatkan laporan lengkap dengan kesimpulannya, berdasaarkan hasil<br />

praktek.

KEGIATAN BELAJAR 4: FLIP-FLOP<br />

h. Tujuan Pemelajaran<br />

1. Mampu mengaplikasikan konsep-konsep sistem <strong>digital</strong> menjadi<br />

rangkaian flip-flop<br />

2. Menjelaskan prinsip kerja macam-macam rangkaian flip-flop dengan<br />

benar<br />

3. Menjelaskan fungsi rangkaian flip-flop<br />

i. Uraian Materi<br />

Flip-flop adalah keluarga Multivibrator yang mempunyai dua keadaaan<br />

stabil atau disebut Bistobil Multivibrator. Rangkaian flip-flop mempunyai<br />

sifat sekuensial karena sistem kerjanya diatur dengan jam atau pulsa,<br />

yaitu sistem-sistem tersebut bekerja secara sinkron dengan deretan<br />

pulsa berperiode T yang disebut jam sistem (System Clock atau<br />

disingkat menjadi CK). Seperti yang ditunjukkan dalam gambar 1:<br />

Gambar1: Keluaran dari pembangkit pulsa yang digunakan sebagai<br />

deretan pulsa untuk sinkronisasi suatu sistem <strong>digital</strong><br />

sekuensial Lebor pulsa tp diandaikan kecil terhadap T<br />

Berbeda dengan uraian materi sebelumnya yang bekerja atas dasar<br />

gerbang logika <strong>dan</strong> logika kombinasi, keluarannya pada saat tertentu<br />

hanya tergantung pada harga-harga masukan pada saat yang sama.<br />

Sistem seperti ini dinamakan tidak memiliki memori. Disamping itu<br />

bahwa sistem tersebut menghafal hubungan fungsional antara variabel<br />

keluaran <strong>dan</strong> variabel masukan.<br />

Se<strong>dan</strong>gkan fungsi rangkaian flip-flop yang utama adalah sebagai<br />

memori (menyimpan informasi) 1 bit atau suatu sel penyimpan 1 bit.<br />

Modul ELKA.MR.UM.004.A 53

Selain itu flip-flop juga dapat digunakan pada Rangkaian Shift Register,<br />

rangkaian Counter <strong>dan</strong> lain sebagainya.<br />

Macam - macam Flip-Flop:<br />

1. RS Flip-Flop<br />

2. CRS Flip-Flop<br />

3. D Flip-Flop<br />

4. T Flip-Flop<br />

5. J-K Flip-Flop<br />

ad 1. RS Flip-Flop<br />

RS Flip-Flop yaitu rangkaian Flip-Flop yang mempunyai 2 jalan<br />

keluar Q <strong>dan</strong> Q (atasnya digaris). Simbol-simbol yang ada pada<br />

jalan keluar selalu berlawanan satu dengan yang lain. RS-FF<br />

adalah flip-flop dasar yang memiliki dua masukan yaitu R (Reset)<br />

<strong>dan</strong> S (Set). Bila S diberi logika 1 <strong>dan</strong> R diberi logika 0, maka<br />

output Q akan berada pada logika 0 <strong>dan</strong> Q not pada logika 1. Bila<br />

R diberi logika 1 <strong>dan</strong> S diberi logika 0 maka keadaan output akan<br />

berubah menjadi Q berada pada logik 1 <strong>dan</strong> Q not pada logika 0.<br />

Sifat paling penting dari Flip-Flop adalah bahwa sistem ini dapat<br />

menempati salah satu dari dua keadaan stabil yaitu stabil I<br />

diperoleh saat Q =1 <strong>dan</strong> Q not = 0, stabil ke II diperoleh saat<br />

Q=0 <strong>dan</strong> Q not = 1 yang diperlihatkan pada gambar berikut:<br />

Gambar 2. RS-FF yang disusun dari gerbang NAND<br />

Modul ELKA.MR.UM.004.A 54

Tabel Kebenaran:<br />

S B Q Q Keterangan<br />

0 0 1 1 Terlarang<br />

0 1 1 0 Set (memasang)<br />

1 1 1 0 Stabil I<br />

1 0 0 1 Reset (melepas)<br />

1 1 0 1 Stabil II<br />

0 0 1 1 Terlarang<br />

1 1 Qn Qn Kondisi memori (mengingat)<br />

Yang dimaksud kondisi terlarang yaitu keadaaan yang tidak<br />

diperbolehkan kondisi output Q sama dengan Q not yaitu pada<br />

saat S=0 <strong>dan</strong> R=0.<br />

Yang dimaksud dengan kondisi memori yaitu saat S=1 <strong>dan</strong> R=1,<br />

output Q <strong>dan</strong> Qnot akan menghasilkan perbedaan yaitu jika Q=0<br />

maka Qnot=1 atau sebaliknya jika Q=1 maka Q not =0.<br />

ad 2. CRS Flip-Flop<br />

Tabel kebenarannya:<br />

S R Qn +1<br />

0 0 Qn<br />

0 1 0<br />

1 0 1<br />

1 1 terlarang<br />

Keterangan:<br />

Qn = Sebelum CK<br />

Qn +1 = Sesudah CK<br />

CRS Flip-flop adalah clocked RS-FF yang dilengkapi dengan<br />

sebuah terminal pulsa clock. Pulsa clock ini berfungsi<br />

Modul ELKA.MR.UM.004.A 55

mengatur keadaan Set <strong>dan</strong> Reset. Bila pulsa clock berlogik 0,<br />

maka perubahan logik pada input R <strong>dan</strong> S tidak akan<br />

mengakibatkan perubahan pada output Q <strong>dan</strong> Qnot. Akan<br />

tetapi apabila pulsa clock berlogik 1, maka perubahan pada<br />

input R <strong>dan</strong> S dapat mengakibatkan perubahan pada output Q<br />

<strong>dan</strong> Q not.<br />

ad 3. D Flip-Flop<br />

D flip-flop adalah RS flip-flop yang ditambah dengan suatu inventer<br />

pada reset inputnya. Sifat dari D flip-flop adalah bila input D (Data) <strong>dan</strong><br />

pulsa clock berlogik 1, maka output Q akan berlogik 1 <strong>dan</strong> bilamana<br />

input D berlogik 0, maka D flip-flop akan berada pada keadaan reset<br />

atau output Q berlogik 0.<br />

Tabel Kebenaran:<br />

D Qn+1<br />

0<br />

1<br />

Gambar 4. D flip-flop<br />

0<br />

1<br />

Modul ELKA.MR.UM.004.A 56

ad 4. T Flip-Flop<br />

Tabel Kebenaran:<br />

T Q<br />

0 0<br />

1 0<br />

0 1<br />

1 1<br />

0 0<br />

1 0<br />

0 1<br />

1 1<br />

Gambar 5. T flip-flop<br />

Rangkaian T flip-flop atau Togle flip-flop dapat dibentuk dari<br />

modifikasi clocked RSFF, DFF maupun JKFF. TFF mempunyai<br />

sebuah terminal input T <strong>dan</strong> dua buah terminal output Q <strong>dan</strong><br />

Qnot. TFF banyak digunakan pada rangkaian Counter, frekuensi<br />

deviden <strong>dan</strong> sebagainya.<br />

ad 5. J-K Flip-Flop<br />

JK flip-flop sering disebut dengan JK FF induk hamba atau Master<br />

Slave JK FF karena terdiri dari dua buah flip-flop, yaitu Master FF<br />

<strong>dan</strong> Slave FF. Master Slave JK FF ini memiliki 3 buah terminal<br />

input yaitu J, K <strong>dan</strong> Clock. Se<strong>dan</strong>gkan IC yang dipakai untuk<br />

menyusun JK FF adalah tipe 7473 yang mempunyai 2 buah JK<br />

flip-flop dimana lay outnya dapat dilihat pada Vodemaccum IC<br />

Modul ELKA.MR.UM.004.A 57

(Data bookc IC). Kelebihan JK FF terhadap FF sebelumnya yaitu<br />

JK FF tidak mempunyai kondisi terlarang artinya berapapun input<br />

yang diberikan asal ada clock maka akan terjadi perubahan pada<br />

output.<br />

Tabel Kebenaran:<br />

j. Rangkuman<br />

Gambar 6. JK FF<br />

J K Qn+1 Keterangan<br />

0 0 Qn Mengingat<br />

0 1 0 Reset<br />

1 0 1 Set<br />

1 1 Qn (strep) Togle<br />

Telah diuraikan konfigurasi flip-flop RS, CRS, D (Data), T (Togle) <strong>dan</strong> JK<br />

sebagai lima jenis flip-flop yang penting. Hubungan logika yang berlaku<br />

untuk masing-masing flip-flop adalah berbeda. Suatu flip-flop IC<br />

biasanya dijalankan secara sinkron dengan suatu jam <strong>dan</strong> disamping itu<br />

IC tersebut dapat (atau tidak dapat) memiliki masukan langsung untuk<br />

operasi asinkron/tak sinkron, masukan J <strong>dan</strong> K Data <strong>dan</strong> Clear. Masukan<br />

langsung hanya dapat berharga 0 diantara pulsa jam (Clock) ketika<br />

CK=0. Bilamana CK=1 kedua masukan asinkron harus dalam keadaan<br />

tinggi <strong>dan</strong> harus tetap bertahan pada keadaanya selama jangka waktu<br />

pulsa, CK=1. Untuk flip-flop majikan budak (Master Slave), keluaran Q<br />

tetap sama selama jangka waktu pulsa <strong>dan</strong> hanya berubah setelah CK<br />

berubah dari 1 ke 0, pada tepi pulsa kearah negatif flip-flop togle atau<br />

Modul ELKA.MR.UM.004.A 58

komplementer tidak terdapat secara komersial karena JK FF dapat juga<br />

digunakan sebagai T FF dengan menghubungkan langsung masukan J<br />

<strong>dan</strong> K seperti gambar dibawah.<br />

k. TUGAS<br />

a. Berikan definisi dari suatu flip-flop!<br />

b. Tuliskan 2 fungsi dari flip-flop !<br />

c. Sebutkan jenis-jenis flip-flop yang pengaturnya menggunakan jam<br />

(clock)!<br />

d. Gambarkan sebuah flip-flop RS yang tidak menggunakan <strong>dan</strong><br />

disusun dari pintu/gerbang NAND!<br />

e. Apa arti dari Men-Set flip-flop?<br />

l. Test Formatif<br />

I Berilah tanda silang pada jawaban yang paling benar!<br />

1. Flip-flop termasuk golongan/keluarga:<br />

a. Univibrator<br />

b. Astabil Multivibrator<br />

c. Monostabil Multivibrator<br />

d. Bistabil Multivibrator<br />

2. Yang bukan merupakan jenis flip-flop yang diatur dengan clock<br />

adalah:<br />

a. JK FF<br />

b. D FF<br />

c. CRS FF<br />

d. RS FF<br />

3. Daerah terlarang untuk RS FF yang disusun dari pintu NAND<br />

yaitu:<br />

a. S=0 , R=0 c. S=0 , R=0<br />

Modul ELKA.MR.UM.004.A 59

. S=1 , R=0 d. S=1 , R=1<br />

4. Daerah stabil untuk RS FF yang dibangun dari pintu NAND yaitu:<br />

a. S=0 , R=0 c. S=1 , R=0<br />

b. S=1 , R=1 d. S=0 , R=1<br />

5. Yang disebut dengan Me-Reset sebuah FF yaitu dengan membuat<br />

keluaran:<br />

a. Q=1 , Qnot=0 c. Q=0 , Qnot=1<br />

b. Q=1 , Qnot=1 d. Q=0 , Qnot=0<br />

6. Jenis flip-flop yang tidak mempunyai kondisi terlarang adalah:<br />

a. RS FF dari NAND c. JK FF<br />

b. CRS FF d. RS FF dari NOR<br />

7. Daerah terlarang untuk CRS flip-flop adalah:<br />

a. R=1 , S=1 c. R=0 , S=1<br />

b. R=0 , S=0 d. R=1 , S=0<br />

8. Pernyataan berikut merupakan fungsi dari flip-flop, kecuali:<br />

a. Memory<br />

b. Pembangkit pulsa clock<br />

c. Rangkaian penggeser data<br />

d. Rangkaian hitung<br />

9. Jenis IC yang melaksanakan fungsi NAND adalah:<br />

a. 7402 c. 7473<br />

b. 7400 d. 7474<br />

10. Jenis IC yang melaksanakan fungsi JK FF adalah:<br />

a. 7402 c. 7473<br />

b. 7400 d. 7474<br />

II Jawablah pertanyaan berikut dengan tepat, jelas <strong>dan</strong> benar!<br />

1. Gambarkan <strong>dan</strong> buatlah tabel kebenaran dari CRS Flip-flop!<br />

2. Gambarkan <strong>dan</strong> buatlah tabel kebenaran dari JK Flip-flop!<br />

Modul ELKA.MR.UM.004.A 60

m. Kunci Jawaban<br />

1. 1. d 6. c<br />

2. d 7. a<br />

3. a 8. b<br />

4. b 9. b<br />

5. c 10. c<br />

2. Uraian<br />

1. Gambar CRS FF <strong>dan</strong> tabel kebenaran<br />

Tabel kebenaran:<br />

S R Qn +1<br />

0 0 Qn<br />

0 1 0<br />

1 0 1<br />

1 1 terlarang<br />

2. Gambar JK FF <strong>dan</strong> tabel kebenaran<br />

Tabel kebenaran:<br />

J K Qn+1 Keterangan<br />

0 0 Qn Mengingat<br />

0 1 0 Reset<br />

1 0 1 Set<br />

1 1 Qn (strep) Togle<br />

Modul ELKA.MR.UM.004.A 61

n. Lembar Kerja<br />

Judul 1 : RS FF , CRS FF <strong>dan</strong> D FF dengan gerbang-gerbang NAND<br />

ALAT DAN BAHAN<br />

1. IC SN 7400 : 2 buah<br />

2. LED : 2 buah<br />

3. R : 220 Ω : 2 buah<br />

4. Multimeter<br />

5. Catu daya 5 Volt<br />

6. Breadboard<br />

7. Kabel penghubung secukupnya<br />

GAMBAR RANGKAIAN<br />

R-S Flip-flop<br />

C-RS Flip-Flop<br />

Modul ELKA.MR.UM.004.A 62

LANGKAH KERJA<br />

MERAKIT RS FF<br />

D Flip Flop<br />

IC SN 7400<br />

1. Buatlah rangkaian RS FF seperti pada gambar rangkaian diatas.<br />

2. Masukkanlah tegangan +5V pada kaki 14 <strong>dan</strong> ground pada kaki<br />

7.<br />

3. Masukkan input logik pada input-input R <strong>dan</strong> S seperti pada tabel<br />

dibawah ini. Dan masukan hasil pengamatan ini ke dalam tabel I.<br />

TABEL I<br />

INPUT OUTPUT<br />

R S Q Qnot<br />

0 0<br />

0 1<br />

1 1<br />

1 0<br />

1 1<br />

0 0<br />

Modul ELKA.MR.UM.004.A 63

4. Ulangi percobaan ini beberapa kali sampai dapat memahami sifat<br />

<strong>dan</strong> cara kerja rangkaian RS FF.<br />

MERAKIT CLOCK<br />

1. Buatlah C-RS FF seperti pada gambar rangkaian diatas.<br />

2. Masukkanlah tegangan +5V pada kaki 14 <strong>dan</strong> ground pada kaki<br />

7.<br />

3. Masukanlah input logik pada input R, S <strong>dan</strong> Clock seperti pada<br />

tabel II, <strong>dan</strong> kemudian catat keadaan outputnya <strong>dan</strong> masukanlah<br />

hasilnya ke dalam tabel II berikut:<br />

TABEL II<br />

INPUT OUTPUT<br />

R S C Q Qnot<br />

0 0 0<br />

0 0 1<br />

1 0 0<br />

1 0 1<br />

0 1 0<br />

0 1 1<br />

1 1 0<br />

1 1 1<br />

4. Ulangilah percobaan ini beberapa kali sampai dapat memahami<br />

sifat <strong>dan</strong> cara kerja C-RS FF dengan gerbang NAND.<br />

MERAKIT D FF<br />

1. Buatlah rangkaian D FF seperti pada gambar rangkaian diatas.<br />

2. Masukkanlah tegangan +5V pada kaki 14 <strong>dan</strong> ground pada kaki<br />

7.<br />

3. Masukkan input logik pada input D <strong>dan</strong> Clock, lalu amatilah<br />

keadaan outputnya <strong>dan</strong> catatlah hasilnya ke dalam tabel III.<br />

Modul ELKA.MR.UM.004.A 64

TABEL III<br />

INPUT OUTPUT<br />

D Clock Q Qnot<br />

0 0<br />

0 1<br />

1 0<br />

1 1<br />

4. Ulangi percobaan ini beberapa kali sampai dapat memahami sifat<br />

KESIMPULAN<br />

<strong>dan</strong> cara kerja rangkaian D flip-flop dengan gerbang NAND.<br />

Apakah kesimpulan dari percobaan ini?<br />

Judul 2 : JK Flip-Flop <strong>dan</strong> T Flip-Flop<br />

ALAT DAN BAHAN<br />

1. IC SN 7473<br />

2. R : 220 Ω : 2 buah<br />

3. LED : 2 buah<br />

4. Catu Daya 5 Volt<br />

5. Bread Board<br />

6. Kabel Penghubung secukupnya<br />

GAMBAR RANGKAIAN<br />

J-K FF induk Hamba<br />

Modul ELKA.MR.UM.004.A 65

LANGKAH KERJA<br />

JK flip-flop Induk Hamba<br />

T FF Induk hamba<br />

1. Buatlah rangkaian JK FF seperti pada gambar diatas.<br />

2. Masukan tegangan +5 V pada kaki 4 <strong>dan</strong> ground pada kaki 11.<br />

3. Berikan keadaan logik pada input J, K <strong>dan</strong> Clock. Lalu amatilah<br />

keadaan outputnya <strong>dan</strong> catat hasilnya pada tabel I.<br />

4. Ulangi percobaan ini beberapa kali sampai dapat memahami sifat<br />

<strong>dan</strong> cara kerja rangkaian JK FF induk hamba.<br />

INPUT OUTPUT<br />

JA KA ClockA QA QAnot<br />

0 0 0<br />

0 0 1<br />

0 1 0<br />

0 1 1<br />

1 0 0<br />

1 0 1<br />

1 1 0<br />

1 1 1<br />

INPUT OUTPUT<br />

JB KB ClockB QB QBnot<br />

0 0 0<br />

0 0 1<br />

0 1 0<br />

0 1 1<br />

1 0 0<br />

1 0 1<br />

1 1 0<br />

Modul ELKA.MR.UM.004.A 66

1 1 1<br />

T FF Induk Hamba<br />

1. Buatlah rangkaian seperti pada gambar diatas.<br />

2. Masukan tegangan +5 V pada kaki 4 <strong>dan</strong> ground pada kaki 11.<br />

3. Berikan input logik pada input T, lalu amati <strong>dan</strong> catat keadaan<br />

outputnya pada tabel II berikut ini:<br />

TABEL<br />

KESIMPULAN<br />

INPUT OUTPUT<br />

T (Togle) Q Qnot<br />

0<br />

1<br />

0<br />

1<br />

0<br />

1<br />

0<br />

1<br />

Kesimpulan apakah yang diperoleh dari percobaan JK FF <strong>dan</strong> T FF<br />

ini?<br />

Modul ELKA.MR.UM.004.A 67

KEGIATAN BELAJAR 5: REGISTER<br />

a. Tujuan Pemelajaran<br />

1. Dapat menganalisa <strong>dan</strong> menggunakan flip-flop dalam rangkaian<br />

Register<br />

2. Menyebutkan macam-macam register dengan benar<br />

3. Menyebutkan fungsi <strong>dan</strong> kegiatan Register<br />

4. Menggambarkan macam-macam Register<br />

5. Menjelaskan prinsip kerja macam-macam register<br />

b. Uraian Materi<br />

Register adalah sekelompok flip-flop yang dapat dipakai untuk<br />

menyimpan <strong>dan</strong> untuk mengolah informasi dalam bentuk linier.<br />

Ada 2 jenis utama Register yaitu:<br />

1. Storage Register (register penyimpan)<br />

2. Shift Register (register geser)<br />

Register penyimpan (Storage Register) digunakan apabila kita hendak<br />

menyimpan informasi untuk sementara, sebelum informasi itu dibawa<br />

ke tempat lain. Banyaknya kata/bit yang dapat disimpan, tergantung<br />

dari banyaknya flip-flop dalam register.<br />

Satu flip-flop dapat menyimpan satu bit. Bila kita hendak menyimpan<br />

informasi 4 bit maka kita butuhkan 4 flip-flop.<br />

Contoh: Register yang mengingat bilangan duaan (biner): 1101 terbaca<br />

pada keluaran Q.<br />

Modul ELKA.MR.UM.004.A 68

Shift Register adalah suatu register dimana informasi dapat bergeser<br />

(digeserkan). Dalam register geser flip-flop saling dikoneksi, sehingga<br />

isinya dapat digeserkan dari satu flip-flop ke flip-flop yang lain, kekiri<br />

atau kekanan atas perintah denyut lonceng (Clock).<br />

Dalam alat ukur digit, register dipakai untuk mengingat data yang<br />

se<strong>dan</strong>g ditampilkan.<br />

Ada 4 Shift Register yaitu:<br />

1. SISO (Serial Input Serial Output)<br />

Gambar Register SISO yang menggunakan JK FF<br />

Word in (SI)<br />

Clock<br />

Prinsip kerja:<br />

1<br />

2<br />

3<br />

J<br />

CLK<br />

K<br />

FF1<br />

Q<br />

Q<br />

4<br />

5<br />

Q1<br />

Modul ELKA.MR.UM.004.A 69<br />

1<br />

2<br />

3<br />

J<br />

CLK<br />

K<br />

FF2<br />

Informasi/data dimasukan melalui word in <strong>dan</strong> akan dikeluarkan jika<br />

ada denyut lonceng berlalu dari 1 ke 0. Karena jalan keluarnya flip-<br />

flop satu dihubungkan kepada jalan masuk flip-flop berikutnya, maka<br />

informasi didalam register akan digrser ke kanan selama tebing dari<br />

denyut lonceng (Clock).<br />

Tabel Kebenaran (Misal masuknya 1101)<br />

Clock ke Word in Q1 Q2 Q3 Q4<br />

0 0 0 0 0 0<br />

1 1 1 0 0 0<br />

2 0 0 1 0 0<br />

3 1 1 0 1 0<br />

4 1 1 1 0 1<br />

Q<br />

Q<br />

4<br />

5<br />

Q2<br />

1<br />

2<br />

3<br />

J<br />

CLK<br />

K<br />

FF3<br />

Q<br />

Q<br />

4<br />

5<br />

Q3<br />

1<br />

2<br />

3<br />

J<br />

CLK<br />

K<br />

FF4<br />

Q<br />

Q<br />

4<br />

5<br />

Q4

Register geser SISO ada dua macam yaitu:<br />

1. Shift Right Register (SRR)/Register geser kanan<br />

2. Shift Left Register (SLR)/Register geser kiri<br />

3. Shift Control Register dapat berfungsi sebagai SSR maupun SLR<br />

Rangkaian Shift control adalah sebagi berikut:<br />

Geser Kanan<br />

Geser Kiri<br />

Rangkaian ini untuk mengaktifkan geser kanan/kiri yang ditentukan<br />

oleh SC. Jika SC=1, maka akan mengaktifkan SLR. Jika SC=0, maka<br />

akan mengaktifkan SRR. Gambar rangkaian selengkapnya adalah<br />

sebagai berikut:<br />

Serial out<br />

Clock<br />

Serial in<br />

SRR<br />

SC<br />

Keterangan:<br />

1<br />

D Q<br />

3<br />

2<br />

CLK<br />

DFF1<br />

1<br />

D Q<br />

3<br />

2<br />

CLK<br />

DFF2<br />

Modul ELKA.MR.UM.004.A 70<br />

DFF3<br />

Out<br />

1<br />

D Q<br />

3<br />

2<br />

CLK<br />

1<br />

D Q<br />

3<br />

2<br />

CLK<br />

DFF4<br />

Serial out<br />

Serial in<br />

SLR<br />

Jika SC=0,maka input geser kanan akan aktif. Keluaran NAND<br />

diumpamakan ke input DFF1 <strong>dan</strong> setelah denyut lonceng<br />

berlaku (saat tebing depan), maka informasi diteruskan ke<br />

output Q1. Dan output Q1 terhubung langsung keoutput DFF2

erikutnya sehingga dengan proses ini terjadi pergeseran ke<br />

kanan.<br />

TABEL KEBENARAN (jika input 1101)<br />

Clock ke Input Q1 Q2 Q3 Q4<br />

0 0 0 0 0 0<br />

1 1 1 0 0 0<br />

2 1 1 1 0 0<br />

3 0 0 1 1 0<br />

4 1 1 0 1 1<br />

Informasi digit digeser kekanan setiap ada perubahan pulsa<br />

clock tebing atas. Geser kanan berfungsi sebagai operasi<br />

aritmatika yaitu pembagi dua untuk tiap-tiap flip-flop.<br />

Jika SC = 1 , maka akan mengaktifkan input geser kiri. Output<br />

NAND masuk ke input D-FF4 <strong>dan</strong> setelah diberi pulsa clock<br />

informasi dikeluarkan melalui Q4 <strong>dan</strong> keluaran Q4<br />