You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

mengatur keadaan Set <strong>dan</strong> Reset. Bila pulsa clock berlogik 0,<br />

maka perubahan logik pada input R <strong>dan</strong> S tidak akan<br />

mengakibatkan perubahan pada output Q <strong>dan</strong> Qnot. Akan<br />

tetapi apabila pulsa clock berlogik 1, maka perubahan pada<br />

input R <strong>dan</strong> S dapat mengakibatkan perubahan pada output Q<br />

<strong>dan</strong> Q not.<br />

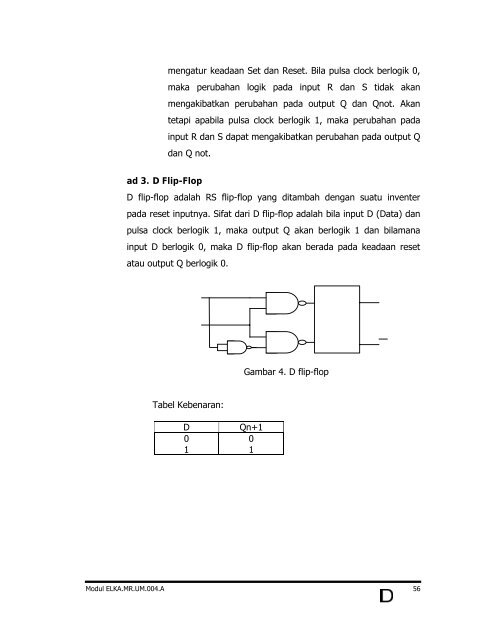

ad 3. D Flip-Flop<br />

D flip-flop adalah RS flip-flop yang ditambah dengan suatu inventer<br />

pada reset inputnya. Sifat dari D flip-flop adalah bila input D (Data) <strong>dan</strong><br />

pulsa clock berlogik 1, maka output Q akan berlogik 1 <strong>dan</strong> bilamana<br />

input D berlogik 0, maka D flip-flop akan berada pada keadaan reset<br />

atau output Q berlogik 0.<br />

Tabel Kebenaran:<br />

D Qn+1<br />

0<br />

1<br />

Gambar 4. D flip-flop<br />

0<br />

1<br />

Modul ELKA.MR.UM.004.A 56