Dispensa Calcolatori..

Dispensa Calcolatori..

Dispensa Calcolatori..

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>Calcolatori</strong> Elettronici II<br />

23/03/2004<br />

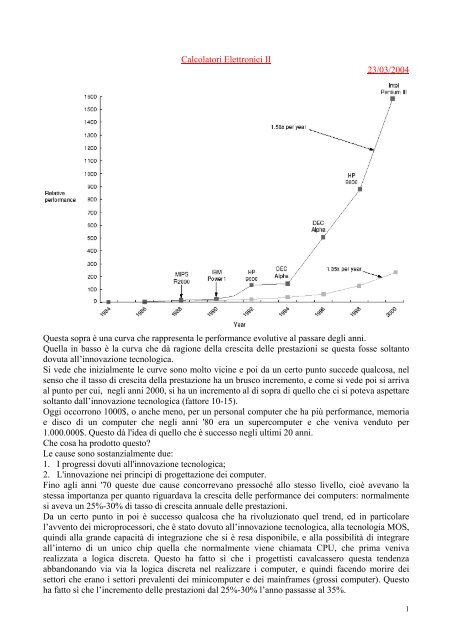

Questa sopra è una curva che rappresenta le performance evolutive al passare degli anni.<br />

Quella in basso è la curva che dà ragione della crescita delle prestazioni se questa fosse soltanto<br />

dovuta all’innovazione tecnologica.<br />

Si vede che inizialmente le curve sono molto vicine e poi da un certo punto succede qualcosa, nel<br />

senso che il tasso di crescita della prestazione ha un brusco incremento, e come si vede poi si arriva<br />

al punto per cui, negli anni 2000, si ha un incremento al di sopra di quello che ci si poteva aspettare<br />

soltanto dall’innovazione tecnologica (fattore 10-15).<br />

Oggi occorrono 1000$, o anche meno, per un personal computer che ha più performance, memoria<br />

e disco di un computer che negli anni '80 era un supercomputer e che veniva venduto per<br />

1.000.000$. Questo dà l'idea di quello che è successo negli ultimi 20 anni.<br />

Che cosa ha prodotto questo?<br />

Le cause sono sostanzialmente due:<br />

1. I progressi dovuti all'innovazione tecnologica;<br />

2. L'innovazione nei principi di progettazione dei computer.<br />

Fino agli anni '70 queste due cause concorrevano pressoché allo stesso livello, cioè avevano la<br />

stessa importanza per quanto riguardava la crescita delle performance dei computers: normalmente<br />

si aveva un 25%-30% di tasso di crescita annuale delle prestazioni.<br />

Da un certo punto in poi è successo qualcosa che ha rivoluzionato quel trend, ed in particolare<br />

l’avvento dei microprocessori, che è stato dovuto all’innovazione tecnologica, alla tecnologia MOS,<br />

quindi alla grande capacità di integrazione che si è resa disponibile, e alla possibilità di integrare<br />

all’interno di un unico chip quella che normalmente viene chiamata CPU, che prima veniva<br />

realizzata a logica discreta. Questo ha fatto sì che i progettisti cavalcassero questa tendenza<br />

abbandonando via via la logica discreta nel realizzare i computer, e quindi facendo morire dei<br />

settori che erano i settori prevalenti dei minicomputer e dei mainframes (grossi computer). Questo<br />

ha fatto sì che l’incremento delle prestazioni dal 25%-30% l’anno passasse al 35%.<br />

1

In realtà però questo salto essenzialmente era dovuto, più che all'innovazione nelle tecniche di<br />

progettare un computer, quasi esclusivamente alla tecnologia. Ad un certo punto c'è stata una<br />

svolta: fino a quel punto si lavorava tipicamente in assembler, e questo significa che non era facile<br />

programmare, e poi quando veniva creato un nuovo microprocessore si cercava di renderlo<br />

compatibile con quello precedente, almeno per quanto riguardava l'esecuzione del codice; un<br />

esempio classico è quello della famiglia Intel (che è nata con l'8080, che era un microprocessore a 8<br />

bit, poi è nato l'8085, l'8086, l'80186, …, l'80486, Pentium), dove un codice sviluppato negli anni<br />

'80 ancora girerebbe su un Pentium. Questo era legato non al fatto che il progettista nel progettare il<br />

prossimo microprocessore era “innamorato” dell'architettura precedente, ma ad un fatto pratico,<br />

cioè al fatto di non sprecare tutte le risorse investite nel progettare il software che girava su quel<br />

microprocessore. Questo era un vincolo fortissimo per il progettista. A metà degli anni '80 però via<br />

via si è cominciato ad abbandonare il linguaggio assembler, perché i programmatori cominciavano<br />

ad usare sempre più i compilatori. Abbandonare il linguaggio assembler significava incominciare ad<br />

eliminare quel vincolo sulla compatibilità del codice: se ho un codice scritto in C e voglio passare<br />

da un processore all'altro ricompilo e non devo rifare il software. Però questo è uno degli aspetti;<br />

l'altro aspetto fondamentale è legato ai sistemi operativi: fino a quel tempo i sistemi operativi erano<br />

essenzialmente i sistemi operativi proprietari, e questo significava che quando l'IBM, per esempio,<br />

vendeva ad una banca un software che girava su quel sistema operativo, questa era bloccata a vita<br />

su quella piattaforma perché il software fa riferimento al sistema operativo.<br />

Poi è stato creato Unix: è stato concepito all'interno di un’università, quindi era un software libero,<br />

non risentiva di logiche di mercato e si poneva quindi come un sistema operativo che non era legato<br />

ad una particolare piattaforma hardware. Unix è stato già dall'inizio progettato, quasi tutto scritto in<br />

C e non più in assembler, per essere indipendente dalla piattaforma. Questo ha fatto sì che il<br />

progettista improvvisamente si trovasse di fronte ad una libertà inaspettata. A questo punto,<br />

Patterson ed Hennessy non dovendo più sottostare a quei vincoli potevano progettare un processore<br />

che aveva delle prestazioni molto più elevate delle architetture che in quel momento erano in<br />

circolazione. Questa logica ha fatto sì che si incominciasse ad affermare la nuova filosofia di<br />

processori, che è quella che si chiama RISC (reduced instruction set computer).<br />

A parità di tecnologia perché una filosofia RISC dovrebbe avere prestazioni migliori?<br />

Patterson ed Hennessy hanno fatto una considerazione: prima si programmava in assembler, e oltre<br />

al problema della compatibilità del codice c'erano altri problemi, cioè un programmatore assembler<br />

da un nuovo processore si aspetta un set di istruzioni molto ricco così ha una certa libertà nello<br />

scegliere il proprio stile di programmazione. Una volta che non si programma più in assembler non<br />

è più programmatore che utilizza il set di istruzioni del processore ma il compilatore, ovvero il<br />

progettista del compilatore; allora ci si è chiesti il perché continuare a progettare un processore con<br />

set di istruzioni ricchissimo (ricchissimo significa che da un punto di vista implementativo più<br />

esteso e complesso è il set di istruzioni più complesso è l'hardware che poi realizza quel set di<br />

istruzioni, e quindi occupa più area sul silicio) se poi nessuno più lo utilizza, o meglio non si sa<br />

quanto è utilizzato. Qual è il modo più semplice e diretto di capire se conviene o no progettare un<br />

set di istruzioni ricco visto che adesso ci sono i compilatori? Si cominciano a compilare tanti<br />

programmi diversi tra loro e vado a vedere ogni per programma compilato quali sono le istruzioni<br />

del processore che utilizza, e magari faccio una statistica. Facendo questo posso scoprire che, per<br />

esempio, un’istruzione pazzesca che qualcuno aveva concepito in quel microprocessore dal<br />

compilatore non veniva mai usata o quasi mai; ma allora se io la tolgo il compilatore entra in crisi<br />

oppure si può sempre trovare una strategia per cui quella istruzione io la faccio la stessa però<br />

usando altre istruzioni? La risposta naturalmente è sì. Siccome progettare un processore significa<br />

innanzitutto definire il suo set di istruzioni, e siccome il progettista sa che più complesso è il set di<br />

istruzioni più complesso è il processore, allora incomincia a vedere un determinato compilatore su<br />

quel processore che ha un set complesso di istruzioni quante ne utilizza, e quindi si fanno delle<br />

statistiche, delle misure sull'utilizzo del set di istruzioni. Facendo queste misure è emerso che<br />

moltissime istruzioni erano praticamente quasi mai utilizzate. Allora a questo punto la cosa più<br />

2

ovvia era ridurre il set di istruzioni all'essenziale; ma riducendo il set di istruzioni qual è il<br />

vantaggio che si ottiene? Se il set di istruzioni è meno complesso significa che l'hardware è meno<br />

complesso e quindi posso andare più veloce. Se io diminuisco il numero di transistor all'interno del<br />

chip per eseguire le istruzioni, i rimanenti transistor li posso utilizzare per metterci dentro la<br />

memoria oppure per realizzare il pipeline (un modo di eseguire più istruzioni contemporaneamente<br />

all'interno dello stesso processore). Normalmente il processore è molto più veloce della memoria,<br />

allora se all'interno del processore si sono liberati tanti transistor potrei utilizzare quell'aria di silicio<br />

libera per mettere un po’ di memoria dentro, per esempio dei registri; questo mi fa andare più<br />

veloce perché si risparmiano un sacco di accessi in memoria.<br />

Un aspetto è la memoria cache. Tutte le volte che si va memoria il processore deve rallentare<br />

moltissimo, allora la possibilità di inventarsi la gerarchia di memoria, cioè la memoria cache, è un<br />

qualcosa che fa pagare molto meno il prezzo al processore sulla lentezza della memoria.<br />

Facendo queste innovazioni si incomincia ad assistere ad un rate di crescita delle prestazioni di oltre<br />

il 50% per anno, e questo è quello che dà la spiegazione dell'andamento di quelle curve.<br />

Conseguenze:<br />

• Un microprocessore di oggi supera le prestazioni di un supercomputer di 10 anni fa<br />

• Dominanza di computer a microprocessore (PC+WS) sull'intero range dei computers<br />

(minicomputer e mainframe sostituiti da multiprocessore).<br />

Tutto questo è dovuto a questa innovazione nell'arte di progettare, innovazione che si basa sul<br />

principio fondamentale che è quello di un approccio quantitativo alla progettazione. Approccio<br />

quantitativo significa che prima di progettare qualcosa vado a fare delle misure vedo quello che già<br />

ho come viene utilizzato, e se ci sono cose che vengono utilizzate raramente queste sono le<br />

candidate ad essere buttate via, e questo significa inventarsi qualcosa di nuovo.<br />

Questa è una possibile rappresentazione della catena alimentare: i pesci più grossi mangiano i pesci<br />

più piccoli:<br />

Questa catena alimentare nel caso dell'informatica è stata ribaltata:<br />

Alcune conseguenze dell'approccio quantitativo sono:<br />

• Le prestazioni delle workstation migliorano del 50% per anno<br />

• Se si tiene conto del fattore costo un miglioramento costo-prestazioni del 70% per anno.<br />

Quando parliamo di computer che cosa intendiamo esattamente?<br />

Oggi ci sono tre segmenti di mercato che è abbastanza facile identificare:<br />

• Desktop computing (PC + WS)<br />

• Servers: file server, web server, ecc…<br />

• Embedded computers: parte più in crescita del mercato.<br />

3

Questi tre segmenti di mercato però hanno caratteristiche diverse da diversi punti di vista:<br />

Nell'ultima riga sono riportate le caratteristiche tipiche di ognuno dei tre settori: nel caso del<br />

desktop due parametri importanti sono il prezzo e le prestazioni (anche sulla grafica); per quanto<br />

riguarda il server si vuole un throughput elevato, cioè che riesca per esempio a processare un certo<br />

numero di milioni di richieste secondo, la disponibilità, che significa la capacità del sistema a<br />

continuare a mantenersi funzionante anche in presenza di guasti, e poi la scalabilità, ovvero la<br />

capacità del sistema ad essere espanso (un server normalmente prevede la possibilità di aumentare<br />

la capacità di memorizzazione, la possibilità di aggiungere processori, ecc…); per quanto riguarda i<br />

sistemi embedded questi sono caratterizzati sicuramente dal prezzo, il consumo di potenza,<br />

prestazioni per quella specifica applicazione.<br />

Dopo aver parlato di questa suddivisione e aver visto come i tre settori richiedono parametri di<br />

performance diversi, il compito del progettista è quello di determinare quali sono gli attributi della<br />

nuova macchina, e progettare per massimizzare la prestazioni rispettando i vincoli di costo e<br />

potenza, naturalmente collocandosi nel settore orientato (desktop, server o embedded).<br />

Un aspetto molto interessante è quello legato alla tendenza della tecnologia: perché un progettista di<br />

computer deve preoccuparsi moltissimo della tendenza tecnologica? Se io progettista ho oggi una<br />

certa tecnologia e il progetto del prossimo processore lo faccio con quello che ho a disposizione,<br />

perché mi devo preoccupare della tecnologia che avrò fra due anni?<br />

Ci sono dei dati che sono abbastanza consolidati che riguardano l'evoluzione della tecnologia:<br />

(capacity = capacità d’integrazione)<br />

C'è un parametro che assume un ruolo cruciale: time to market = 2 anni design + produzione. Il<br />

time to market è il tempo che si impiega ad immettere un nuovo prodotto sul mercato. Se io ho un<br />

time to market, per esempio per una workstation, di due anni e faccio il progetto con la tecnologia<br />

di oggi faccio un errore clamoroso perché se fra due anni il trend tecnologico è quello visto sopra<br />

allora la capacità, per esempio, sarà sicuramente maggiore di quella di oggi. Quindi bisogna<br />

guardare a cosa ci sarà disponibile quando il prodotto andrà in produzione.<br />

Altri aspetti legati alla tecnologia sono:<br />

• Feature size: minima size di un transistor o wire nelle direzioni x e y<br />

10µ (1971) → 0,08µ (2003)<br />

Il numero di transistor incrementa quadraticamente con la diminuzione della feature size,<br />

mentre la performance invece aumenta linearmente con la feature size.<br />

• All'aumentare della capacità di integrazione e della frequenza di funzionamento di questi<br />

dispositivi il ritardo di propagazione (wire delay) dei segnali incomincia ad essere rilevante:<br />

4

molti cicli di clock sono spesi per il ritardo sulle linee, e nel caso del Pentium IV due stage di<br />

pipeline su 20 sono consumati per la propagazione dei segnali attraverso il chip.<br />

• Potenza (power): l'incremento del numero di transistor per chip e la frequenza di switching<br />

comporta un incremento del consumo di potenza (qualche decina di W per un microprocessore<br />

anni '80, 100 W per il Pentium IV a 2GHz).<br />

Nel prossimo futuro la potenza sarà il limite principale.<br />

5

25/03/2004<br />

Abbiamo visto che una delle chiavi fondamentali che spiega l'elevato incremento delle performance<br />

nei computers è un nuovo approccio alla progettazione: un approccio di tipo quantitativo, quindi un<br />

approccio che sostanzialmente assume come paradigma quello di eseguire delle misure e sulla base<br />

di queste misure selezionare quelli che sono gli aspetti più rilevanti, quindi quelli che sono più<br />

suscettibili di essere migliorati garantendo un elevato livello di performance, e trascurando altri<br />

aspetti che, per quanto possono offrire scelte che soddisfano l'utente, magari poi sono molto poco<br />

utilizzati.<br />

Per fare queste misure questo approccio quantitativo utilizza vari strumenti che si basano su un<br />

insieme di programmi che si chiamano Benchmarks, sui Traces (queste informazioni vengono<br />

derivate a fronte dell'esecuzione di un programma, e per esempio questi traces ci dicono<br />

un'istruzione rispetto al totale quante volte viene eseguita), sugli instruction Mixes (mi dicono per<br />

esempio 30% di ALU e così via).<br />

Abbiamo visto, per esempio, nel caso dei sistemi embedded che uno dei requisiti fondamentali,<br />

oltre alla performance per quella determinata applicazione, per esempio era il consumo di potenza,<br />

ma si capisce bene è fondamentale anche l'area consumata sul silicio. Quindi sono stati messi a<br />

punto strumenti per la stima della potenza, dell'aria, del delay (tempo speso per eseguire un<br />

programma), ecc.<br />

Naturalmente poi ci sono strumenti che provano valutare i vari parametri di interesse attraverso<br />

teorie “tradizionali”, quale la teoria delle code, regole di tipo pratico, e leggi fondamentali.<br />

Oggi incominciamo a vedere cosa significa valutare alcuni parametri prestazionali dei sistemi<br />

partendo da alcune definizioni di base. Per noi misurare le prestazioni di un computer, per esempio<br />

in termini di velocità, significa valutare il tempo di esecuzione, cioè all'utente finale quello che<br />

interessa è quanto tempo viene speso da questo oggetto per eseguire una determinata applicazione,<br />

quindi si parla di ExTime (execution time): dire che un computer X è n volte più veloce di un<br />

computer Y significa dire che<br />

(per un web server non ci interessa l’ExTime, ma il throughput). A seconda che si parla di ExTime,<br />

oppure di throughput, oppure di qualsiasi altro parametro, devo stare attento a cosa mettere<br />

numeratore per dire che una cosa è più performante di quella precedente; questa ambiguità si<br />

elimina, quanto meno a livello di linguaggio, parlando di rapporto di prestazioni: se io dico che la<br />

macchina X è più performante della macchina Y di n volte, significa che<br />

Naturalmente in questo caso si ha che , se la mia performance è<br />

espressa in termini di tempo di esecuzione; se invece come performance intento il throughput ecco<br />

che la performance coincide con il throughput.<br />

Se X è n% volte più veloce di Y significa che<br />

dove<br />

> 1<br />

> 1<br />

,<br />

6

Esempio:<br />

Se Y impiega 15 secondi per eseguire un task e X impiega 10 secondi, quanto % X è più veloce?<br />

n=50%.<br />

Legge di Amdahl<br />

Questo è un principio che dovrebbe essere sempre seguito da un progettista, e in verità occorrerebbe<br />

seguirlo sempre a prescindere che il progetto riguardi un computer piuttosto che un'automobile, ecc.<br />

Make the common case fast! (rendi il caso più frequente veloce).<br />

“Più frequente” come va inteso? Va inteso che quando io utilizzo il sistema c'è una sua parte che è<br />

responsabile di molto del tempo di lavoro del sistema, allora intuitivamente un miglioramento<br />

apportato a questa parte ci ripaga sufficientemente.<br />

In miglioramento di prestazioni che può essere ottenuto migliorando una qualche attività, quindi<br />

rendendola più veloce, è limitato dalla frazione di tempo in cui tale attività ha luogo.<br />

SPEEDUP: misura di quanto più veloce un task gira sulla macchina enhanced. Quindi se io misuro<br />

uno Speedup = 1.5 significa che ho migliorato le performance del 50%.<br />

Vediamo come si ricava una qualche relazione che ci consenta quantitativamente di misurare qual è<br />

lo Speedup che si ottiene quando si apporta un miglioramento ad un sistema.<br />

Supponiamo di avere un programma che impiega il seguente tempo (la ExTime) per essere<br />

eseguito; analizzando il sistema vedo che c'è una sua parte che si<br />

può migliorare e in termini di tempo di esecuzione è<br />

responsabile di quella frazione di tempo (parte colorata) rispetto al totale. Questa parte a cui applico<br />

il miglioramento posso renderla più veloce, e questo significa che nel nuovo sistema quella parte si<br />

contrarrà, e quindi il tempo di esecuzione totale si accorcerà:<br />

Il rapporto tra il primo tempo di esecuzione e il secondo mi dà lo Speedupoverall (cioè Speedup<br />

complessivo).<br />

Le due grandezze che ci interessano sono: Speedupenhanced (Speedup Enhanced, cioè lo Speedup che<br />

posso ottenere solo della parte a cui applico il miglioramento); il rapporto tra il tempo da migliorare<br />

e l’ExTime totale si chiama FractionEnhanced (cioè la frazione di tempo a cui posso applicare il<br />

miglioramento, si misura sul sistema originario).<br />

Avendo definito queste due grandezze possiamo vedere come si misura lo Speedupoverall.<br />

Quest'ultimo non è altro che:<br />

(woE = without enhancement, wE = with<br />

enhancement).<br />

Il nuovo tempo di esecuzione è dato da:<br />

Così lo Speedupoverall è:<br />

Questa formula ci consente di fare un sacco di valutazioni per scoprire se un determinato<br />

miglioramento ripaga oppure no in termini di guadagno complessivo che si può ottenere.<br />

Nelle annunciato della legge di Amdahl abbiamo detto che il performance improvement è limitato<br />

dalla frazione di tempo in cui l'attività ha luogo; questa frazione di tempo è proprio la<br />

FractionEnhanced; ovvero il massimo Speedup ottenibile è limitato dalla FractionEnhanced. In che senso?<br />

7

Immaginiamo, caso irrealizzabile, di trovare un’idea che fa sì che una certa parte del sistema possa<br />

andare infinitamente più veloce di quanto va adesso; questo significa che lo Speedupenhanced sarebbe<br />

infinito e quindi il rapporto FractionEnhanced/Speedupenhanced tenderebbe a 0; più elevata è la<br />

FractionEnhanced maggiore è lo Speedupoverall.<br />

Da questa analisi semplicissima si può concludere che quello che in effetti ha un impatto enorme<br />

dal punto di vista di guadagno di prestazioni complessivo è la FractionEnhanced, ovvero la frazione di<br />

tempo suscettibile di essere migliorata: maggiore è questa frazione di tempo maggiore è il guadagno<br />

che si può ottenere, e questo ragionamento lo si fa indipendentemente da quanto veloce si vuole<br />

rendere.<br />

Esempio<br />

Prendiamo un computer che ha un certo processore in cui la parte relativa all’esecuzione delle<br />

istruzioni in floating point può essere migliorata facendola andare al doppio di velocità rispetto a<br />

quella attuale, quindi abbiamo uno Speedupenhanced pari a 2; qual è il guadagno che possiamo<br />

ottenere? Per rispondere a questa domanda dobbiamo stimare la FractionEnhanced. L’unità floating<br />

point viene utilizzata dai programmi, quindi non devo parlare in astratto, ma prendo un programma,<br />

suppongo che è il programma che mi interessa, e vedo quanto tempo viene speso (da questo<br />

programma) durante l’esecuzione sull’unità floating point rispetto al totale. In questo caso<br />

supponiamo che soltanto il 10% delle istruzioni eseguite sono di tipo floating point, ed è come dire<br />

che soltanto il 10% del tempo rispetto al totale del tempo di esecuzione, di un determinato<br />

programma, viene speso per la parte floating point. Questo 10% rappresenta la FractionEnhanced.<br />

Applicando le formule abbiamo:<br />

Quindi viene fuori che lo Speedup è pari al 5,3%.<br />

Esempio<br />

Dato un computer cerchiamo di rendere più veloce la CPU di 5 volte, ma questo ci costa 5 volte il<br />

costo originale della CPU. Quanto ci guadagno?<br />

Per vedere se questo investimento è economicamente vantaggioso devo vedere quanto ci guadagno<br />

in termini di performance e quanto mi costa questo guadagno di performance.<br />

I dati che abbiamo sono:<br />

la CPU nel sistema originario è responsabile del 50% del tempo totale di esecuzione (di un<br />

determinato programma); questo significa che l’altro 50% è dedicato all’I/O. Il costo della CPU è<br />

di 1/3 del costo totale del sistema.<br />

La prima cosa che facciamo è valutare lo Speedup:<br />

Quindi ottengo un miglioramento di performance complessivo pari al 67%.<br />

Quanto mi costa questo investimento? I 2/3 del sistema continueranno a costare quanto prima,<br />

mentre l’altro 1/3 costerà 5 volte di più:<br />

Quindi mi costerà 2,33 volte il costo originario.<br />

Così ho che il costo cresce molto di più delle performance.<br />

8

Esempio<br />

Supponiamo di avere un computer su cui viene eseguito una determinata applicazione. Questa<br />

applicazione ha delle operazioni in floating point alcune delle quali sono radici quadrate (FPSQR).<br />

In totale l’unità floating point è responsabile del 50% del tempo di esecuzione, e la sola FPSQR è<br />

responsabile del 10% del tempo di esecuzione totale. A questo punto c’è una gara tra due tipi di<br />

progettazione diversi:<br />

1) l’hardwareista dice che riesce a migliorare l’hardware del FPSQR in modo tale da farlo andare<br />

10 volte più veloce;<br />

2) il softwareista dice che può ottenere il doppio di velocità dell’intera unità floating point.<br />

Nel primo caso ho una FractionEnhanced che è pari a 0,2 e uno Speedup di 10, e allora ne segue che:<br />

Nel secondo caso ho una FractionEnhanced che è pari a 0,5 e uno Speedup di 2, e allora ne segue che:<br />

Quindi migliorano di più le prestazioni se aumento la velocità di tutta l’unità floating point anche se<br />

solo del doppio, rispetto al miglioramento della sola FPSQR anche se di 10 volte.<br />

Abbiamo detto che uno dei dilemmi che fa diventare matti i progettisti di computer è quello della<br />

lentezza della memoria. È un problema perché il computer nasce come una macchina per eseguire<br />

programmi e la CPU non fa altro che andare a leggere l'istruzione della memoria ed eseguirla.<br />

Quindi sicuramente per ogni istruzione bisogna fare quanto meno un accesso in memoria; questo<br />

significa che tutti i miglioramenti di prestazioni che si riescono ad apportare al processore possono<br />

essere vanificate dalla lentezza della memoria. Cosa si può fare per cercare di risolvere questo<br />

problema, o quanto meno di farlo pesare poco?<br />

Non potendo fare niente la tecnologia, qualcuno si è inventato una soluzione estremamente<br />

intelligente. Questa soluzione fa riferimento ad un principio che è il cosiddetto principio di<br />

località, e ad un altro principio che è molto legato all'elettronica. Per quanto riguarda l'elettronica<br />

c'è un principio che dice che: “smaller is faster” (più piccolo è più veloce). Sappiamo che quando<br />

parliamo di memorie RAM ci sono due tipologie: RAM statiche e RAM dinamiche. Le RAM<br />

statiche sono caratterizzate da una velocità più elevata delle RAM dinamiche, però le prime hanno il<br />

problema che consumano di più, perché sono più veloci, e la loro capacità di integrazione è molto<br />

più bassa delle seconde.<br />

Il principio di località è un principio che fa riferimento ad una considerazione base: quando eseguo<br />

un programma vado in memoria legge un istruzione, la eseguo e vado all'istruzione successiva, ecc.;<br />

queste istruzioni quando un programma viene caricato in memoria si succedono una dopo l'altra<br />

nella memoria; quindi quando io eseguo l'istruzione i-esima è probabile che la prossima da eseguire<br />

sta nella locazione di memoria immediatamente successiva. Questo è quello che ha fatto pensare a<br />

qualcuno che allora c'è una località nell'esecuzione del programma, e questo è quello che viene<br />

chiamato principio di località spaziale, ovvero quando io vado a referenziare un item<br />

probabilmente referenzierò gli item che stanno là intorno.<br />

C'è un altro aspetto di questo principio di località che, piuttosto che guardare alla località spaziale,<br />

guarda alla località temporale, ovvero se io vada referenziare un item (istruzione) in questo tempo, è<br />

probabile che nel prossimo futuro la referenzierò di nuovo (si pensi ai loop).<br />

Questa considerazione che tipo di idea potrebbe fare venire al progettista per risolvere questo<br />

problema del gap di prestazioni tra processore e memoria?<br />

9

Se io vado ad interporre una memoria statica, quindi una piccola memoria, tra processore e RAM<br />

dinamica, e in questa piccola memoria di volta in volta ci metto, sfruttando il principio di località, la<br />

parte di codice che viene referenziata, essendo veloce diminuisco in termini di velocità il gap tra<br />

processore e memoria. Quest’idea è furba soltanto se capita poco spesso che il processore andando<br />

in questa piccola memoria (memoria cache) non trova quello che cerca. Per verificare se questa cosa<br />

succede poco spesso oppure no si fanno delle misure su dei programmi di uso molto frequente. Ci<br />

sono delle misure su programmi molto utilizzati e si va scoprire che l’80%-90% dei riferimenti<br />

generati dal processore durante l'esecuzione di un programma cadono all'interno del 10%-20%<br />

dell'intero codice. Se questo è vero quel 20% di codice lo piglio e lo metto nella memoria statica.<br />

Da un punto di vista architetturale il nostro sistema si organizza nel seguente modo:<br />

abbiamo il processore all'interno del quale c'è un certo insieme di registri (che si può vedere come<br />

una piccola memoria incorporata all'interno del processore), poi quando il processore ma all'esterno<br />

per leggere dalla memoria qualcosa, incontra come prima cosa la memoria cache, che sta prima<br />

della main memory, e naturalmente dopo c’è la memoria di massa. Vista in questi termini è come se<br />

avessimo creato una gerarchia di memoria. Più alto è il livello, più questo è prossimo al processore<br />

più veloce è, e più costoso è.<br />

Esempio<br />

Cache cinque volte più veloce della main memory, e il 90% del tempo di CPU è speso in una<br />

frazione di codice che può interamente essere posto in cache.<br />

Lo Speedup che posso ottenere è:<br />

Questo significa che il sistema complessivamente sarà più veloce di 3,6 volte, cioè delle 360%.<br />

(secondo me del 260%)<br />

La formula che sintetizza il principio di Amdahl e che fa riferimento allo Speedupenhanced e alla<br />

FractionEnhanced ci serve a valutare il rapporto tra il vecchio ExTime e il nuovo ExTime. Laddove<br />

questi ExTime io potessi valutarli attraverso altre grandezze che magari in alcuni casi sono più<br />

facilmente misurabili è ovvio che ricorro ad un altro modo per valutarli.<br />

Cycles per Instruction<br />

A noi interessa vedere qual è il CPU time, cioè il tempo speso dalla CPU per eseguire un<br />

programma. Naturalmente in questo CPU time non è presente la parte eventualmente legata<br />

all’input/output.<br />

Il CPU time lo possiamo esprimere attraverso il seguente prodotto:<br />

10

Il tempo del processore durante il suo lavoro viene scandito da un clock con un periodo pari a Tck.<br />

Se io voglio misurare quanto tempo ho speso per eseguire un programma, ovviamente se conosco<br />

quant'è il periodo di clock, misuro quanti cicli di clock dall'inizio alla fine del programma sono<br />

trascorsi.<br />

CK cycles for a program a sua volta si può esprimere come Ic × CPI, dove Ic sta per Instruction<br />

Count, e CPI è il clock per instruction.<br />

Supponiamo di potere sapere quante istruzioni sono state eseguite, Ic, e conosco il numero di cicli di<br />

clock eseguiti per ogni istruzione, allora il numero di cicli di clock richiesti per un’istruzione<br />

moltiplicati per il numero di istruzioni mi dà il numero totale di cicli di clock del programma, che<br />

moltiplicato per il tempo di clock mi dà il CPUtime:<br />

Il CPI in realtà non è altro che un valore medio, ed è ottenuto come:<br />

Qua si parla di CPI medio. In realtà molto spesso io posso calcolare il CPI attraverso una media<br />

pesata che fa riferimento a categorie diverse di istruzioni: quando viene eseguito un programma ci<br />

saranno istruzioni che implicano l’esecuzione di operazioni logico-aritmetiche (ALU), poi ci<br />

saranno istruzioni di Branch (salto condizionato), poi ci saranno istruzioni di scambio di<br />

informazioni tra la memoria e il processore (Load/Store), ecc…; ammettendo che ogni categoria sia<br />

omogenea dal punto di vista del numero di cicli di clock richiesta per essere eseguita posso<br />

calcolare il CPI attraverso una media pesata:<br />

dove n rappresenta il numero di categorie distinte di istruzioni, ed Fi è la frequenza con cui la<br />

categoria i-esima è presente all’interno del running; la frequenza non è altro che il numero di volte<br />

in cui quella categoria di istruzioni è stata eseguita rispetto al numero di istruzioni totali eseguite:<br />

Ovviamente il CPUtime in questo caso è pari a:<br />

Il problema è stimare Fi, cioè durante un runnig quante volte è stata eseguita una determinata classe<br />

di istruzioni; questo si chiama instruction mix.<br />

È da notare che il CPIi dovrebbe essere misurato e non dedotto da quello che normalmente viene<br />

chiamato CPU technical reference manual, perché questo assume che tutto vada alla velocità del<br />

processore e non considera che alcuni cicli di clock possono essere spesi per degli accessi in<br />

memoria che è più lenta.<br />

Se è vero che il CPUtime è una misura delle prestazioni del nostro sistema ed è esprimibile dal<br />

prodotto di Ic, CPI e Tck, noi possiamo pensare che se vogliamo apportare un miglioramento,<br />

diminuire l’Ic del 30% è la stessa cosa, in termini di guadagno di performance, di fare più veloce il<br />

clock del 30% oppure ridurre del 30% il CPI medio. Allora si potrebbe pensare di investire sulla<br />

cosa che viene più facile migliorare. C’è un problema: questi tre fattori non sono tra di loro<br />

indipendenti, ma cercare di migliorare uno dei tre porta al peggioramento di qualcuno degli altri due<br />

o di entrambi. Quindi come sempre succede nella pratica bisogna trovare un compromesso tra<br />

esigenze molto spesso tra di loro in conflitto.<br />

11

Di seguito mostriamo una tabella che fa vedere da cosa dipendono l’Ic, il CPI e il Clock Rate:<br />

L’Ic dipende dal compilatore perché ogni compilatore lo stesso programma lo può tradurre in<br />

diversi modi; dipende dall’Instruction Set perché per esempio un’istruzione di Branch in alcuni<br />

processori è un’unica istruzione, e ci sono processori in cui il loro set di istruzioni non prevede di<br />

fare sia la verifica della condizione che il salto in un’unica istruzione, ma sono splittate su due<br />

istruzioni diverse.<br />

Il CPI indirettamente dipende dal compilatore perché a seconda di come compilo, e quindi dalla<br />

sequenza di istruzioni che produco, questo può portare a richiedere più cicli di clock per eseguire<br />

un’istruzione; dipende dall’Instruction Set perché se nel mio set di istruzioni includo un’istruzione<br />

che fa un insieme di operazioni è ovvio che ha bisogno di più cicli di clock per essere eseguita;<br />

dipende dall’Organizzazione che è l’organizzazione architetturale che io scelgo per implementare<br />

tutte le attività che deve eseguire il processore.<br />

Il Clock Rate dipende dall’Organizzazione perché più semplice è l’hardware più veloce si può<br />

rendere; ed è ovvio che la Tecnologia incide sulla frequenza di clock.<br />

Si vede che il miglioramento della tecnologia porta solo benefici.<br />

Come si vede se io penso di abbassare il CPI agendo sull’organizzazione bisogna capire cosa<br />

succede al clock rate; per esempio se io trovo una soluzione che mi porta le istruzioni dell’ALU da<br />

1.5 cicli di clock ad 1 ciclo di clock, e però per implementare questa soluzione scopro che<br />

l’hardware si è complicato e quindi la frequenza di clock con cui opero devo abbassarla,<br />

automaticamente ho migliorato il CPI ed ho peggiorato il Clock Rate.<br />

12

30/04/2004<br />

Esempio<br />

Facciamo riferimento ad una macchina base A in cui all’interno dell’instruction set tutte le volte che<br />

dobbiamo implementare un if, cioè un salto condizionato, in realtà per come è fatto l’instruction set<br />

questo richiede l’esecuzione di due istruzioni: COMPARE + BRANCH.<br />

Immaginando di avere un programma che giri su questa macchina, attraverso delle misure sono<br />

state dedotte le seguenti frequenze di esecuzione delle varie classi di istruzioni:<br />

alla fine otteniamo un CPI<br />

medio di 1,2. Significa che<br />

per eseguire quel<br />

programma mediamente<br />

spendiamo 1,2 cicli di<br />

clock per ogni istruzione.<br />

A questo punto un progettista pensa di apportare una modifica: proviamo a modificare l’instruction<br />

set di questo processore in modo tale che l’istruzione COMPARE venga incorporata all’interno<br />

dell’istruzione di BRANCH, cioè in poche parole la fase di valutazione della condizione appartiene<br />

all’istruzione di BRANCH. Per fare questo però l’organizzazione interna del processore,<br />

l’organizzazione hardware, è tale che la frequenza di clock operativa deve modificarsi; in<br />

particolare a seguito di questa modifica bisogna allungare, rispetto alla versione base, il periodo di<br />

clock di 1,25, cioè del 25%. La domanda è: conviene questa modifica?<br />

Supponendo di ignorare il problema legato al costo, cioè quanto costa fare questa modifica, ma ci<br />

concentriamo soltanto sulla performance, noi dobbiamo andare a vedere se il tempo speso per<br />

eseguire lo stesso programma sulla macchina A o sulla macchina B (quella modificata) varia, e<br />

come varia.<br />

Cercando di ricavarsi di nuovo quel tipo di tabella, però per la nuova macchina, adesso dobbiamo<br />

vedere qual è la nuova frequenza di BRANCH, e la frequenza delle rimanenti istruzioni:<br />

Sappiamo che il CPUtime della macchina base è: CPUtimeA = IcA × 1,2 × TckA.<br />

Noi sappiamo che sulla macchina B l’IcB varia rispetto a quello della macchina A perché in<br />

quest’ultima c’erano due istruzioni per ogni BRANCH; questo significa che adesso il numero di<br />

istruzioni si contrae del 20%: IcB = IcA – 20%IcA = 0,8IcA.<br />

La frequenza di BRANCH è data dal numero di occorrenze del BRANCH rispetto all’IcB<br />

complessivo:<br />

Così la tabella che si ottiene è:<br />

quindi il nuovo CPI medio è 1,25.<br />

13

A questo punto il CPUtimeB è:<br />

CPUtimeB = IcB × CPIB × 1,25 × TckA = 0,8IcA × 1,25 × 1,25TckA = 1,25 × IcA × TckA.<br />

Questo significa che il programma viene eseguito più velocemente nella macchina A.<br />

Quando si parla di misure delle performance c'è un indice, che è stato utilizzato moltissimo un po'<br />

di anni fa, tuttora viene ancora utilizzato, ma è caduto in disuso, che è il cosiddetto MIPS: milioni di<br />

istruzioni per secondo. MIPS = instruction count / Time × 10 6 = Clock Rate / CPI × 10 6 .<br />

Se io confronto due CPU è una ha un numero di MIPS maggiore dell'altra allora la prima è più<br />

veloce della seconda. Questa cosa non è detto che sia una cosa vera: è facilmente dimostrabile che<br />

una CPU con un numero di MIPS può portare ad un CPUtime maggiore piuttosto che minore. Se<br />

due CPU hanno un set diverso di istruzioni, lo stesso programma compilato su una macchina<br />

potrebbe presentare un MIPS, quando viene eseguito, maggiore perché per esempio sono istruzioni<br />

semplici quindi maggiori come numero di istruzioni piuttosto che in un'altra macchina dove ci sono<br />

istruzioni più complesse.<br />

I MFLOP/s sono milioni di floating point operation per second.<br />

MFLOP/s = FP Operation / Time × 10 6 . Anche in questo caso vale lo stesso ragionamento fatto<br />

prima.<br />

Esempio<br />

Supponiamo di avere una macchia base di cui sono state ottenute, a fronte dell'esecuzione di un<br />

programma, le seguenti statistiche:<br />

Questa macchina base che tipo di set di istruzioni ha?<br />

Ha un set di istruzioni che si chiamano register/register, oppure si può dire che è una macchina di<br />

tipo Load/Store. Una macchina di tipo Load/Store è una macchina in cui qualsiasi operazione che<br />

coinvolge l'unità logica-aritmetica (ALU) può essere eseguita soltanto se gli operandi stanno<br />

entrambi all'interno del processore, cioè sono nei registri del processore. Questo significa che, per<br />

esempio, quando scriviamo un programma in C e c’è la somma fra due variabili, queste variabili se<br />

quando è stato compilato il programma stanno in memoria, prima di potere eseguire la somma<br />

bisogna prevedere che il valore di queste variabili venga caricato con un’operazione di load<br />

all’interno di registri del processore, e successivamente può essere eseguita la somma; il risultato<br />

della somma presuppone che poi ci sia un’operazione di store, cioè venga scritto in memoria.<br />

Questa è un’architettura load/store. In un’architettura di questo tipo non è possibile eseguire, per<br />

esempio, la somma tra un operando che sta all’interno di un registro del processore e un operando<br />

che sta all’interno della memoria.<br />

Adesso rispetto ad una macchina di tipo load/store supponiamo di voler modificare l’architettura di<br />

questa macchina modificando l’instruction set e aggiungendo una nuova classe di istruzioni di tipo<br />

register/memory ovvero che mi consentono di fare operazioni ALU anche con operandi che stanno<br />

uno in un registro e uno in memoria. Questo tipo di istruzioni richiedono due cicli di clock, a<br />

differenza di una qualunque istruzione ALU che invece richiedeva un ciclo di clock.<br />

14

Il problema è: a fronte dello stesso programma, compilato sulle due macchine, cosa ci guadagno<br />

modificando il set di istruzioni introducendo questo tipo di istruzione? In particolare la domanda è:<br />

quale frazione di load nella macchina base deve essere eliminata perché questa modifica incominci<br />

a dare un guadagno?<br />

Questo significa che, se adesso ho istruzioni di tipo register/memory, tutta una parte di operazioni<br />

che facevo nella macchina base, operazioni che coinvolgevano l’ALU, che richiedevano delle load<br />

verranno eliminate nella nuova macchina perché non è necessario fare delle load esplicite.<br />

In pratica probabilmente riduco l’Ic, e riducendo l’Ic, siccome CPUtime = Ic × CPI × Tck, se non<br />

peggiorano le altre due componenti può darsi che avrò un CPUtime più basso, quindi che la nuova<br />

macchina con questo nuovo set di istruzioni sia più performante della vecchia macchina.<br />

È ovvio che in qualche modo la performance di una macchina dipenderà da quante load<br />

scompaiono; allora in questo caso il nostro obiettivo è valutare qual è la percentuale di load che<br />

deve essere eliminata perché questo tipo di instruction set architecture possa incominciare a fornire<br />

un guadagno rispetto alla macchina base. I dati relativi alla macchina base sono riportati sopra.<br />

Se io metto anche l’istruzione RegMem e chiamiamo X il numero di istruzioni RegMem eseguite<br />

abbiamo che X è il numero di load che si riducono rispetto alla macchina originaria, ma queste<br />

istruzioni di tipo RegMem le utilizzo per fare operazioni di tipo ALU, quindi anche le istruzioni<br />

ALU si riducono di X:<br />

facendo questa<br />

modifica purtroppo<br />

il branch avrà<br />

2 bisogno di tre cicli<br />

di clock.<br />

Calcolando il nuovo CPI otterrei 1.7-X; in realtà X è la frazione di istruzioni espressa però rispetto<br />

al vecchio instruction count. Noi vogliamo calcolare il CPI della nuova macchina, quindi questo<br />

CPI deve essere normalizzato rispetto al nuovo instruction count, ovvero il vecchio instruction<br />

count moltiplicato per 1-X, questo perché ognuna delle nuove frequenze è divisa per 1-X:<br />

F’ALU=N’ALU/I’C=(NALU–NRegMem )/IC(1–X)=NALU/IC(1–X)–NRegMem/IC(1–X)=FALU/(1–X)–X/(1–X).<br />

Vado a trovare il valore di X per cui i due CPUtime sono uguali:<br />

⇒ 1.00 × 1.5 = (1 – X) × (1.7 – X)/(1 – X) (ClockOld = ClockNew)<br />

⇒ 1.5 =1.7 – X ⇒ X = 0.2<br />

X deve essere almeno uguale a 0.2, cioè tutte le load che erano presenti dovrebbero essere<br />

eliminate, affinché la modifica non produca una perdita di performance.<br />

Noi abbiamo considerato il CPUtime immaginando che tutto vada alla velocità della CPU, e quindi<br />

che la CPU non debba aspettare memoria, ecc.<br />

In realtà le cose non stanno così: quando la CPU accede in memoria normalmente deve aspettare.<br />

Abbiamo visto che per mitigare questo problema è stata inventata la memoria cache. Allora tutte le<br />

volte che andando in memoria la CPU trova quello che sta cercando nella cache di fatto non deve<br />

aspettare (immaginando che la cache vada alla stessa velocità del processore); naturalmente questo<br />

non può succedere sempre perché la cache è piccola e quindi difficilmente riuscirà a contenere tutto<br />

quello che serve; questo significa che delle volte ci sarà un miss (mancato successo); in tal caso si<br />

/<br />

15

deve aspettare che il dato che non sta in cache debba essere reperito nel livello di memoria<br />

successivo, main memory, spostato nella cache e quindi il processore può leggere quel dato se si<br />

trattava di un’operazione di lettura. Questo significa che il CPUtime, se lo devo calcolare<br />

correttamente quando c’è una gerarchia di memoria, lo devo esprimere nel seguente modo:<br />

Quindi il tempo di CPU per eseguire un determinato programma sarà pari al numero di cicli della<br />

CPU se tutto andasse bene dilatato di un numero di cicli di stallo, nel senso che il processore deve<br />

bloccare la propria attività aspettando che qualcosa arrivi dalla memoria. Questo come si vede fa sì<br />

che il numero di cicli di clock totale per eseguire quel programma in presenza di una memoria reale<br />

aumenti rispetto al numero di cicli di clock strettamente richiesti dal processore.<br />

Proviamo a esprimere il MemoryStallCycles in qualche modo: questi cicli di clock di stallo si<br />

verificano tutte le volte che andando in memoria si verifica un miss. Se moltiplico il numero di miss<br />

per il miss penalty, ovvero per la penalità che pago per spostare il dato dalla main memory alla<br />

cache espresso in numero di cicli di clock, ottengo il numero totale di cicli di clock di stallo. Se io<br />

voglio mettere in evidenza l’instruction count, il numero di miss non è altro che una frazione di Ic,<br />

ovvero il numero di miss per instruction. Posso definire una nuova grandezza: il cosiddetto miss<br />

rate. Il miss rate non è altro che la frazione di miss che sperimento rispetto al numero totale di<br />

accessi in memoria: se vado 100 volte in memoria (cache) e 15 volte su queste 100 volte c’è un<br />

miss allora il miss rate è il 15%. Allora possiamo scrivere:<br />

dove mem.ref.per.instr. è il numero di riferimenti medio per istruzione, cioè per ogni istruzione<br />

quanti riferimenti in memoria si fanno.<br />

Esempio<br />

Supponiamo di avere una macchina A e supponiamo di avere un programma in cui ci sono il 40% di<br />

istruzioni load/store, un CPI medio pari a 2, in cui però ci siano tutti cache hits (tutti gli accessi in<br />

memoria hanno successo). Questa macchina la voglio confrontare con una macchina B che ha il 2%<br />

di miss rate, cioè il 2% delle volte che vado in cache non trovo quello che voglio; tutte le volte che<br />

succede questo il miss penalty è di 25 cicli di clock.<br />

Nel caso della macchina A abbiamo:<br />

Per quanto riguarda la macchina B abbiamo:<br />

Il mem.ref.per.instr. sarà 1 perché tutte le istruzioni eseguite richiedono un accesso in memoria, e<br />

poi ci sono il 40% delle istruzioni che sono di tipo load/store che richiedono due accessi: uno per<br />

leggere l’istruzione e un altro per eseguire o la load o la store, quindi il numero di riferimenti medi è<br />

1+0,4.<br />

Così il CPUtime è:<br />

Se facciamo il rapporto otteniamo:<br />

Così abbiamo un degrado di performance del 35%.<br />

,<br />

16

Abbiamo parlato di approcci quantitativi alla progettazione basati su misure per vedere quanto una<br />

certa alternativa piuttosto che un’altra è utilizzata, e abbiamo visto come valutare.<br />

Siccome parliamo di computer, cos’è che ci consente di valutare le prestazioni?<br />

Fare girare dei programmi e vedere quanto tempo impiega il computer per eseguirlo.<br />

Se ci mettiamo nella prospettiva in cui normalmente si mettono i produttori di computer si capisce<br />

che è auspicabile che il proprio prodotto è migliore di quello che produce qualcun altro. Solo che<br />

dire “migliore” non è facile.<br />

Incominciamo da un punto di vista logico a definire cosa ci consentirebbe di dire se un computer è<br />

migliore oppure no. Il produttore per dire che un computer è meglio di un altro dovrebbe dimostrare<br />

che per eseguire certi programmi il suo computer impiega meno tempo di un altro; però non si sa a<br />

quali programmi fare riferimento, perché non si sa ogni utente quali programmi usa.<br />

Il primo problema quindi è: quali programmi usare per valutare le prestazioni? E per quali tipologie<br />

di utenti?<br />

Qual è la condizione ideale impossibile da realizzare?<br />

La condizione è quella di utilizzare un workload reale, quindi fatto da programmi reali, che non è<br />

altro che l’insieme di applicazioni e di comandi di sistema operativo che vengono dati durante<br />

l’utilizzo normale da parte di quell’utente. Questo perché gli utenti sono tanti e ognuno ha esigenze<br />

abbastanza diverse.<br />

La soluzione che è stata individuata già da un po’ di anni è quella di utilizzare le cosiddette<br />

benchmark suites, cioè delle collezioni di programmi che in qualche modo siano rappresentativi<br />

dei diversi scenari di utilizzo dei computer.<br />

Che tipo di programmi costituiscono una benchmark suite? Ci sono varie tipologie di programmi.<br />

• Toy benchmarks, sono dei software semplicissimi, 10-100 linee di programma, fatti per<br />

stimolare certi parti del sistema: sieve, puzzle, quicksort.<br />

• Synthetic benchmark, che non sono dei programmi reali, cioè che non risolvono nessun<br />

problema reale: whetstone, dhrystone.<br />

• Kernels, che sono dei pezzi di programmi reali, tipicamente per esempio pezzi di programmi di<br />

un sistema operativo o kernel di qualche applicazione particolare: livermore loops.<br />

• Programmi reali: gcc, spice, ecc.<br />

Dopo aver litigato per tanti anni alla fine i costruttori sempre cercano di trovare un accordo, e in<br />

genere lo scenario in cui si cerca di sintetizzare queste liti e questo accordo è quello degli organismi<br />

di standardizzazione internazionali. A livello di standardizzazione è stato proposto il cosiddetto<br />

SPEC (Standard Performance Evaluation Corporation), che è riconosciuto da tutti i costruttori e che<br />

specifica quali sono i programmi che bisogna utilizzare per valutare le prestazioni di una macchina.<br />

Considerando il tipo di differenziazione del mercato nel settore dei computer (desktop, server ed<br />

embedded) SPEC ha cercato di differenziare le suites per valutare le prestazioni dei vari settori:<br />

CPU intensive significa che stimolano prevalentemente la CPU, quindi valutano le prestazioni<br />

prevalentemente del processore. I Graphic intensive che cercano di valutare le prestazioni dal punto<br />

di vista della grafica. Gli SPEC FS (spec filesystem) sono basati sulla valutazione del numero di<br />

transazioni per secondo che è in grado di eseguire un server.<br />

17

Tipicamente un benchmark esce ogni 3 anni.<br />

SPEC CPU2000<br />

Naturalmente c’è un ampio settore di mercato, che è il settore di mercato più promettente, che è<br />

quello dei PC, per cui sono nati anche i benchmark per PC:<br />

• Business Winstone: è uno script che lancia Netscape e diversi prodotti di Office per cercare di<br />

simulare un workload reale di un tipico pc user;<br />

• CC Winstone: simula un ambiente di applicazioni per la creazione di contenuti multimediali<br />

(Photoshop, Premiere, Navigator, ecc.);<br />

• Winbench: insieme di kernel per il test di CPU, sistema video, dischi.<br />

Per quanto riguarda i sistemi embedded è nato il consorzio EEMBC che ha creato la suite chiamata<br />

EDN che include: automotive industrial, consumer, networking, office automation,<br />

elecommunication.<br />

Si fanno molti giochi con i benchmark:<br />

• ottenere dei risultati migliori su una macchina rispetto ad un’altra facendo girare lo stesso<br />

benchmark suite sui due sistemi senza dire come sono equipaggiati;<br />

• ottenere performance migliori ottimizzando dei compilatori per determinati programmi;<br />

18

• workload utilizzati in modo arbitrario: quando per esempio ho una suite di benchmark con i<br />

programmi A, B, C, D, e il programma A è quello più veloce allora quando faccio girare questa<br />

suite di benchmark, se non ho delle costrizioni particolari, potrei fare girare molte volte il<br />

programma A e poche volte gli altri programmi; quindi prevale la performance del programma<br />

A.<br />

19

01/04/2004<br />

Abbiamo detto che proprio perché è abbastanza complicato individuare un workload che sia<br />

rappresentativo per ogni utente sono nati dei benchmark suites. Un benchmark suite abbiamo detto<br />

che è costituito da un insieme di programmi molto diversi tra di loro, quindi si capisce che non è<br />

facile stabilire qual è il giusto mixing di questi programmi per valutare le prestazioni.<br />

Allora c’è il problema di cercare di stabilire quando si fa girare un benchmark che tipo di rapporto<br />

di prestazioni devo andare ad ottenere.<br />

Una delle cose che molto raramente avviene nel campo dei computer è quello di rispettare il<br />

cosiddetto principio di riproducibilità: includere tutto ciò che consente ad altri di replicare gli<br />

esperimenti fatti.<br />

Nel caso degli SPEC benchmark un report richiede:<br />

- una descrizione quasi completa della macchina (configurazione hardware e software);<br />

- flag di compilazione: quando si usa un programma come gcc per compilare, per esempio, è<br />

necessario settare dei flag in modo tale che tutti devono utilizzare quei flag per compilare;<br />

- pubblicazione dei risultati sia delle performance di base (baseline) sia quelle ottimizzate.<br />

Nella performance baseline viene imposto di utilizzare un particolare tipo di compilatore e un set<br />

di flag da utilizzare nella compilazione per tutti i programmi nello stesso linguaggio.<br />

Per quanto riguarda la performance di picco (peak performance) c’è una maggiore libertà in modo<br />

da potere fare un tuning delle prestazioni attraverso, per esempio, compilatori proprietari o flag<br />

specifici, cioè che non sono imposti.<br />

Esempio di baseline performance<br />

Per quanto riguarda l’affidabilità dei benchmark come predittori della performance reale riportiamo<br />

un esempio:<br />

c’è un programma che si chiama matrix300 (SPEC 89), un software che fa il prodotto tra matrici,<br />

che spende il 99% del tempo di esecuzione su una linea di codice. ottimizzando il loop più interno<br />

attraverso un compilatore per una IBM PowerStation 550 si ottiene un miglioramento di un fattore 9<br />

20

nella performance. In questo modo però non sto testando la macchina ma sto semplicemente<br />

testando la performance del compilatore.<br />

Andiamo ora a capire come si possono misurare le prestazioni a fronte dell’esecuzione di alcuni<br />

programmi.<br />

Quando faccio girare un programma posso dire che la performance è il tempo di esecuzione del<br />

programma; quando mi pongo il problema di trovare un indice globale di prestazione per la mia<br />

macchina è ovvio che non mi conviene dire che la mia macchina per fare girare, per esempio, il gcc<br />

piuttosto che un’altra applicazione impiega tot tempo; poi se quella applicazione non è<br />

rappresentativa per l’utente questo di per sé non è un’informazione che è appetibile per il mercato.<br />

Quindi bisognerebbe tirare fuori un indice di performance globale ricavato dal running di una suite<br />

di benchmark, cioè di programmi abbastanza rappresentativi. Ma qual è quest’indice globale?<br />

Vediamo quali si potrebbero utilizzare, e sulla base di questi eventuali indici globali cercare di<br />

capire se è possibile rispondere ad una domanda: quest’indice globale di performance mi consente<br />

di dire che una macchina è più veloce di un’altra?<br />

Esempio<br />

Abbiamo tre computer e supponiamo di avere una suite di benchmark fatta da due programmi: P1 e<br />

P2. Facendo girare questi due programmi sui tre computer impiego i secondi indicati nella seguente<br />

tabella:<br />

A questo punto bisognerebbe cercare di capire qual è l’indice globale di performance utile ai fini di<br />

dire quale delle tre macchine è più veloce.<br />

Ovviamente per il programma P1 la macchina più veloce è A, e a sua volta B è più veloce di C; per<br />

il programma P2 la macchina più veloce è C, e B è più veloce di A. Quindi non c’è una tendenza<br />

che mi porta a dire che una macchina è più veloce delle altre.<br />

Una misura più consistente è quella, per esempio, di considerare il total execution time. Se io vado a<br />

considerare questo indice trovo i tempi indicati nella tabella sopra. Questo mi porterebbe a dire che<br />

il computer C è 2,75 volte più veloce del computer B e 25 volte del computer A; e il computer B è<br />

9,1 volte più veloce del computer A.<br />

Quindi in questo caso il tempo di esecuzione totale è una misura consistente e ci consente di<br />

affermare quello detto sopra; però questa cosa è vera solo se io faccio girare su queste tre macchine<br />

i programmi P1 e P2 lo stesso numero di volte.<br />

Il problema è che non è detto che io faccia girare lo stesso numero di volte P1 e P2.<br />

Se il numero di running di ogni singolo programma costituente la benchmark allora il total<br />

execution time oppure la media dei tempi di esecuzione sono abbastanza rappresentativi delle<br />

performance.<br />

Nel caso in cui il numero di running di P1 è diverso dal numero di running di P2 si può ricorrere a<br />

due soluzioni:<br />

1) media aritmetica pesata<br />

2) media geometrica.<br />

La media aritmetica pesata è uguale a: , dove Ti è il tempo di esecuzione del programma<br />

i-esimo all’interno del benchmark.<br />

21

Se io ho ni che è il numero di running di Pi nel workload e ∑i ni = n, il peso o la frequenza relativa<br />

del programma i-esimo non è altro che wi = ni / n.<br />

Vediamo alcuni esempi relativamente alle macchine A, B e C:<br />

La pesatura w(1) fa si che pesa nello stesso modo i due programmi: così otteniamo quello che<br />

avevamo ottenuto prima, cioè che il computer C è più veloce di B, e B è più veloce di A, e se si<br />

fanno i rapporti si ottengono gli stessi valori di prima.<br />

Nella pesatura w(2) fisso i pesi in modo tale che siano inversamente proporzionali ai tempi di<br />

esecuzione dei programmi P1 e P2 sul computer B, cioè faccio girare più volte il programma che<br />

richiede meno tempo. In questo modo ottengo che il computer B è più veloce di A e di C, e C è più<br />

veloce di A.<br />

Con la pesatura w(3) fisso i pesi in modo inversamente proporzionale al tempo di esecuzione di P1<br />

e P2 sulla macchina A. In questo modo ottengo che il computer A è più veloce di B e C, e B è più<br />

veloce di C.<br />

Sempre parlando di indici di prestazione globale quando il numero di running dei vari programmi è<br />

diverso piuttosto che la media aritmetica pesata un altro tipo di media che si potrebbe utilizzare è<br />

quella geometrica. In particolare si considera normalmente la media geometrica dei tempi di<br />

esecuzione normalizzati: ho una suite di benchmark e voglio misurare le prestazioni sulla macchina<br />

A, allora devo fare girare il programma sulla macchina A e ottengo un tempo di esecuzione che<br />

devo normalizzare rispetto al tempo di esecuzione dello stesso programma su una macchina<br />

campione (per esempio come macchina campione viene utilizzata per la SPEC una SPARCstation).<br />

In questo caso la media geometrica dei tempi normalizzati è:<br />

Si potrebbe erroneamente pensare che si possa predire la performance di un programma sulla mia<br />

macchina moltiplicando π per la performance del programma sulla macchina campione, essendo<br />

noti sia il primo che la seconda.<br />

Un’altra cosa da notare è che quando si utilizzano i tempi di esecuzione normalizzati e si utilizza la<br />

media aritmetica di questi ultimi si può arrivare a dei paradossi. Per esempio: supponiamo di avere<br />

al solito i computer A, B e C, e i due programmi P1 e P2; normalizzando i tempi di esecuzione<br />

22

considerando le varie macchine come macchina campione si ottengono i valori riportati in tabella.<br />

Se io considero la media aritmetica dei tempi normalizzati o rispetto ad A, B o C, questa fornisce<br />

delle misure assolutamente inconsistenti, nel senso che nel primo caso viene fuori che A è il<br />

computer più veloce, nel secondo caso è B il più veloce, è nel terzo caso e C il più veloce; quindi il<br />

computer più veloce è quello rispetto a cui normalizzo. Quindi non bisogna mai considerare la<br />

media aritmetica dei tempi di esecuzione normalizzati, ma considerare la media geometrica. Infatti<br />

la media geometrica è consistente: indipendentemente dalla macchina campione otteniamo sempre<br />

misure consistenti, in questo caso C è sempre il computer più veloce, e anche i rapporti sono sempre<br />

uguali.<br />

Quindi la media geometrica dei tempi di esecuzione normalizzati è consistente indipendentemente<br />

dalla macchina di riferimento, e non dipende dal numero di running dei programmi individuali.<br />

Uno dei problemi con la media geometrica è che non consente di predire il tempo di esecuzione. Un<br />

altro problema è che quando si considerano tre o più macchine non esiste nessun workload che sia<br />

compatibile con la performance predetta dalla media geometrica. Questo significa che in qualche<br />

modo si vanifica la ragione per cui questa media è stata introdotta.<br />

Un altro problema con la media geometrica è: se per esempio io voglio fare un’ottimizzazione,<br />

ovvero voglio migliorare sulla mia macchina le prestazioni e ho due possibilità, per esempio passare<br />

da 2s a 1s per un programma piuttosto che da 1000s a 500s per un altro programma, se io considero<br />

la media geometrica il miglioramento che io vado a valutare è identico, cioè dire dato lo stesso peso<br />

ai due abbattimenti dei tempi di esecuzione. Quindi se io mi metto nei panni di quello che vuole<br />

truccare le carte e volessi ottenere quello stesso miglioramento di performance globale valutato<br />

attraverso la media geometrica, supponendo che voglio dimezzare il tempo di esecuzione, fra tutti i<br />

programmi vado a scegliere quello su cui è più facile farlo.<br />

Cosa bisogna fare per cercare di dare delle informazioni consistenti e corrette? Bisogna misurare un<br />

workload reale e pesare i programmi con nelle loro frequenze di esecuzione reali.<br />

Quando si dà come misura delle prestazioni un indice globale, questo tende a nascondere delle<br />

informazioni importanti, e in alcuni casi potrebbe non essere il migliore indicatore della<br />

performance per un'applicazione d'utente. Per cui assieme all'indice globale sarebbe bene fornire<br />

anche i risultati (tempo di esecuzione, frequenza con cui è stato fatto girare un programma del<br />

benchmark, ecc…) dei singoli benchmark costituenti il workload.<br />

Sistema di elaborazione<br />

Un sistema di elaborazione per noi non è altro che costituito da tre entità:<br />

statica<br />

In particolare un sistema di elaborazione lo possiamo definire come una macchina in grado di<br />

eseguire programmi espressi in un determinato linguaggio di programmazione.<br />

23

La macchina è un'entità attiva, dinamica (che evolve nel tempo), mentre il programma è una entità<br />

statica. Durante l'esecuzione di un programma questo rimane quello che è, mentre la macchina,<br />

rappresentata da tastiera, monitor e dall'insieme di variabili (che dobbiamo considerare appartenenti<br />

alla macchina) viene modificata (ad esempio il valore delle variabili viene modificato).<br />

Nel nostro modello noi assumiamo normalmente che un'istruzione costituisce una azione atomica<br />

per il nostro sistema, cioè significa che se noi facciamo riferimento allo stato della nostra macchina<br />

(insieme di variabili, e in generale tutto ciò che ha all'interno della macchina memorizza<br />

informazioni) l’istruzione ci fa passare da uno stato all'altro; quindi significa che eseguire un<br />

programma equivale a fare compiere alla nostra macchina una traiettoria di stati all'interno dello<br />

spazio dei possibili stati che la macchina può assumere.<br />

Quello a cui siamo stati abituati a vedere come modello di un sistema di elaborazione è quello che<br />

viene chiamato modello funzionale: il modello che descrive la macchina come un puro esecutore<br />

del proprio linguaggio. Da questo punto di vista tutte le macchine Pascal, oppure C, ecc…, sono<br />

funzionalmente identiche.<br />

Il modello realizzativo di un sistema di elaborazione fa riferimento a come quest’ultimo è fatto,<br />

cioè che tipo di componenti fisici ci sono, come sono collegati tra di loro, ecc.<br />

Questo significa che due macchine che hanno lo stesso modello funzionale non è affatto detto che<br />

abbiano lo stesso modello realizzativo:<br />

Parlando del modello funzionale possiamo dire che la traiettoria di stato che viene percorsa dalla<br />

nostra macchina è di tipo deterministica, cioè è predicibile sapere quali sono tutti gli stati che<br />

attraverserà la nostra macchina se noi conosciamo tre elementi: programma in esecuzione, i dati che<br />

forniamo al nostro programma e lo stato iniziale. Questa affermazione assume un’importanza<br />

notevole perché non è detto che sia così.<br />

Da un punto di vista schematico quello che abbiamo detto sul modello funzionale è rappresentabile<br />

nel seguente modo:<br />

Esempio<br />

dove M = macchina, L = linguaggio, P = programma.<br />

In generale in realtà un sistema di elaborazione è costituito da una gerarchia di macchine, non da<br />

una singola macchina. Questa gerarchia di macchine è organizzata attraverso il seguente principio:<br />

se io mi metto ad un certo livello di questa gerarchia di macchine posso salire di livello, e realizzo<br />

una macchina che sta ad un livello superiore a partire dalla macchina del livello immediatamente<br />

inferiore. Questa affermazione che sembra banale è quella che è stata uno dei motivi della<br />

rivoluzione nel campo dell’informatica, o quantomeno che ha consentito di estendere l’uso dei<br />

calcolatori ad una quantità di utenti maggiore.<br />

24

Realizzo una macchina sopra un’altra macchina a partire o da un compilatore (traduttore) o da un<br />

interprete. (Il compilatore traduce il nostro codice in un altro linguaggio, l’interprete legge il codice<br />

lo interpreta e lo esegue). Il compilatore è più efficiente perché questo traduce il codice una sola<br />

volta, mentre l’interprete ogni volta che si deve far girare il programma interpreta il codice.<br />

In che senso realizzo una macchina sopra un’altra macchina?<br />

Supponiamo di avere una macchina M1 caratterizzata da un proprio<br />

linguaggio L1; su questa macchina posso realizzare una macchina M2,<br />

che gerarchicamente è superiore ad essa, con un linguaggio L2<br />

semplicemente costruendo un programma P12(L1) espresso nel<br />

linguaggio L1, e questo programma non è altro che o un compilatore o<br />

un interprete. Ovviamente il programma che può girare sulla macchina<br />

M2 sarà scritto nel linguaggio L2: P(L2).<br />

Il senso di realizzare una gerarchia di macchine è quello di fare sì che<br />

la macchina sia più facilmente utilizzabile.<br />

Naturalmente se salire di livello significa rendere più facile l’utilizzo<br />

all’uomo, questo allo stesso tempo può penalizzare le prestazioni.<br />

Adesso scendiamo di livello e arriviamo nell’ambito della gerarchia di macchine a quella che viene<br />

chiamata macchina processo. La macchina processo è quella macchina che esegue i programmi<br />

che tipicamente producono i compilatori. Il linguaggio della macchina processo è un linguaggio di<br />

tipo binario. Una caratteristica della macchina processo è che si incomincia a perdere quella che<br />

viene chiamata identità funzionale tra le varie macchine: noi abbiamo detto che tutte le macchine C,<br />

per esempio, sono funzionalmente identiche, mentre la stessa cosa non vale più per le macchine<br />

processo, cioè un programma espresso nel linguaggio di una macchina processo non può girare su<br />

un’altra macchina processo; questo avviene perché la macchina processo è quel livello all’interno<br />

della gerarchia al di sotto del quale non è più possibile nascondere i dettagli realizzativi della<br />

macchina, cioè le differenze reali tra le varie macchine. Questo significa che ogni macchina<br />

processo ha un proprio linguaggio binario, che dipende dal sistema di elaborazione. Sebbene questo<br />

sia vero tutte le macchine processo sono caratterizzate da un insieme di elementi che le rendono<br />

simili. Questi elementi sono:<br />

• sono dotate di una memoria di processo, che sostanzialmente è uguale un po’ per tutte;<br />

• richiedono che il programma, che poi verrà eseguito dalla stessa macchina processo, debba<br />

risiedere nella memoria di processo;<br />

• sono caratterizzate dal fatto che utilizzano per eseguire i programmi un registro che si chiama<br />

Program Counter;<br />

• sono dotate di un meccanismo di esecuzione delle istruzioni del programma che è analogo;<br />

• stato del processo: contenuto di memoria + contenuto dei registri.<br />

La memoria di processo su per giù è la seguente:<br />

25

La memoria non è altro che un sistema che è in grado di memorizzare informazioni espresse in<br />

formato binario. Se il suo scopo è quello di memorizzare informazioni significa che è un sistema<br />

che per essere usato mi deve offrire dei servizi; questi servizi mi devono consentire di memorizzare<br />

informazioni, ma se memorizzo informazioni lo faccio perché poi voglio andare a reperirle. Questo<br />

sistema è organizzato come un insieme di locazioni (ognuna è una riga), e ciascuna locazione (o<br />

cella di memoria, o parola di memoria) è in grado di memorizzare un certo insieme di bit. Una<br />

caratteristica del sistema memoria è che tutte le locazioni di memoria costituenti il sistema hanno la<br />

stessa dimensione in bit, nel nostro caso k bit (k=1, 8 ,16, 32, 64).<br />

Per utilizzare i servizi che vengono offerti dal sistema memoria è necessario specificare alcune<br />

cose. Quando voglio andare a memorizzare un informazione, poiché questo sistema ha N diverse<br />

locazioni, devo specificare al sistema dove voglio che l’informazione venga memorizzata; questo lo<br />

specifico attraverso un indirizzo, utilizzando la porta degli indirizzi che il sistema memoria mette a<br />

disposizione. Inoltre se si vuole depositare una specifica informazione, questa la si dà al sistema<br />

memoria attraverso la porta dei dati.<br />

La capacità di memoria esprime la quantità di informazioni in bit che è memorizzabile in essa<br />

(1Mbyte = 2 20 byte, ovvero 2 20 word di un byte).<br />

Quando avviene la scrittura di una particolare locazione, questa fa sì che il contenuto precedente<br />

scompaia, cioè si altera il contenuto informativo di quella locazione. La lettura, viceversa, mi<br />

consente di accedere ad una locazione ottenere l’informazione che c'è all'interno di quella locazione<br />

mantenendo nella stessa locazione la stessa informazione; quindi significa che la lettura non altera<br />

l’informazione contenuta all'interno di una locazione di memoria.<br />

In scrittura:<br />

• sulla porta degli indirizzi devo fornire l'indirizzo, ovvero la posizione su cui memorizzare la<br />

parola;<br />

• sulla porta dei dati devo fornire l'informazione da scrivere.<br />

A questo punto la memoria prende quello che c'è sulla porta dei dati è lo va a memorizzare<br />

all'interno della locazione selezionata dall'indirizzo presente sulla porta degli indirizzi:<br />

In lettura:<br />

• sulla porta degli indirizzi devo specificare l'indirizzo della locazione da leggere;<br />

• sulla porta dei dati si ottiene la parola memorizzata in quell'indirizzo.<br />

L’indirizzo deve specificare in modo univoco ogni singola locazione di memoria. Ad esempio se<br />

ho una memoria da 1 Kbyte (2 10 byte) occorrono 10 bit (log2 2 10 = 10) per specificare un indirizzo.<br />

26

Come fa il sistema memoria sulla base di quei 10 bit a dire a quale locazione si fa riferimento? Non<br />

fa altro che usare un decodificatore, che è un circuito combinatorio che riceve un ingresso, in questo<br />

caso di 10 bit, e fornisce un’uscita, in questo caso 1024. Facciamo un esempio con un decodificare<br />

binario a 3 bit:<br />

bit più significativo<br />

0<br />

0<br />

1<br />

DEC<br />

bit meno significativo<br />

0<br />

1<br />

2<br />

3<br />

4<br />

5<br />

6<br />

7<br />

Della macchina processo la parte che esegue i programmi è l’unità centrale di processamento<br />

(CPU). Essa non è altro che l’esecutore di cui si serve la macchina processo per eseguire i<br />

programmi che stanno nella memoria di processo; nello svolgere questo ruolo di esecutore coordina<br />

anche tutti i vari blocchi che costituiscono la nostra macchina.<br />

Questa CPU è caratterizzata da un proprio set di istruzioni, ovvero dall’insieme di istruzioni che<br />

essa è in grado di eseguire. Ognuna di queste istruzioni è codificata in binario, e ovviamente questa<br />

codifica binaria deve essere riconoscibile da quella particolare CPU. Questo ci fa capire perché<br />

macchine processo diverse hanno linguaggi binari diversi. Ovviamente un programma può essere<br />

eseguito dalla CPU se è costituito da istruzioni appartenenti al set di istruzioni della CPU, e inoltre<br />

se tutte le istruzioni che costituiscono il programma sono codificate in quel linguaggio binario e<br />

memorizzate sequenzialmente nella memoria centrale. Quindi un programma eseguibile dalla<br />

macchina processo lo possiamo immaginare fatto così:<br />

Il modo stesso di andare a memorizzare il programma in memoria<br />

implicitamente per l’esecutore contiene l’informazione di quale è<br />

l’ordine di esecuzione delle istruzioni.<br />

Formato delle istruzioni<br />

Abbiamo detto che è codificata in binario; questo significa che ogni istruzione del set di istruzioni<br />

di una determinata CPU è costituita da una stringa di 1 e 0 con una certa lunghezza. Tutte le<br />

macchine processo, per quanto ognuna ha un linguaggio binario diverso e tecniche di codifica<br />

diverse, si assomigliano su degli elementi comuni, ovvero tutte utilizzano una tecnica di codifica<br />

che consente di individuare sempre due campi all’interno dell’istruzione codificata: un campo che si<br />

chiama codice operativo e un campo che si chiama operandi<br />

codice operativo operandi<br />

27

La prima parte dell’istruzione (codice operativo) specifica all’esecutore di che tipo di istruzione si<br />

tratta, cioè caratterizza l’istruzione; gli operandi specificano gli oggetti su cui quell’operazione deve<br />