3 相 5 レベル ANPC インバータの理論体積と実験 ... - 長岡技術科学大学

3 相 5 レベル ANPC インバータの理論体積と実験 ... - 長岡技術科学大学

3 相 5 レベル ANPC インバータの理論体積と実験 ... - 長岡技術科学大学

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

3 <strong>相</strong> 5 <strong>レベル</strong> <strong>ANPC</strong> インバータの 理 論 体 積 と 実 験<br />

機 の 体 積 に 対 する 一 考 察<br />

樫 原 有 吾 * , 伊 東 淳 一 ( 長 岡 技 術 科 学 大 学 )<br />

A Consideration about Volume of Calculation and Experimental Value of a Three-phase Five-level <strong>ANPC</strong> Inverter<br />

Yugo Kashihara, Jun-ichi Itoh (Nagaoka University of Technology)<br />

1.はじめに<br />

近 年 , 電 力 変 換 器 の 損 失 や 体 積 を 数 学 的 に 求 め, 最 適 化<br />

する 技 術 が 盛 んに 研 究 されている。 筆 者 らは,これまでに 5<br />

<strong>レベル</strong>アクティブ 中 性 点 クランプ 形 ( 以 下 <strong>ANPC</strong>)インバー<br />

タに 注 目 して, 数 式 を 用 いたパラメータ 設 計 法 について 検<br />

討 を 行 ってきた (1)-(2) 。しかしながら, 実 際 の 変 換 器 の 体 積 は,<br />

半 導 体 素 子 のスイッチングによって 発 生 する 熱 や 部 品 間 の<br />

配 線 などで, 変 換 器 中 の 部 品 体 積 の 総 和 よりも 大 きくなる (3) 。<br />

本 論 文 では, 数 式 を 用 いて 変 換 器 の 実 体 積 を 定 量 的 に 評<br />

価 することを 目 的 として, 電 力 変 換 器 の「 実 装 率 」を 定 義<br />

し,その 検 討 を 行 なう。 一 例 として,3 <strong>相</strong> 10kW <strong>ANPC</strong> イン<br />

バータの 設 計 と 実 機 検 証 を 行 い, 実 装 率 について 考 察 する。<br />

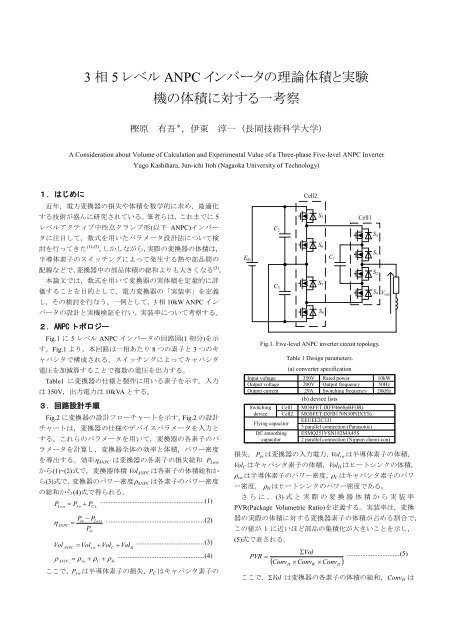

2.<strong>ANPC</strong> トポロジー<br />

Fig.1 に 5 <strong>レベル</strong> <strong>ANPC</strong> インバータの 回 路 図 (1 <strong>相</strong> 分 )を 示<br />

す。Fig.1 より, 本 回 路 は 一 <strong>相</strong> あたり 8 つの 素 子 と 3 つのキ<br />

ャパシタで 構 成 される。スイッチングによってキャパシタ<br />

電 圧 を 加 減 算 することで 複 数 の 電 圧 を 出 力 する。<br />

Table1 に 変 換 器 の 仕 様 と 製 作 に 用 いる 素 子 を 示 す。 入 力<br />

は 350V, 出 力 電 力 は 10kVA とする。<br />

3. 回 路 設 計 手 順<br />

Fig.2 に 変 換 器 の 設 計 フローチャートを 示 す。Fig.2 の 設 計<br />

チャートは, 変 換 器 の 仕 様 やデバイスパラメータを 入 力 と<br />

する。これらのパラメータを 用 いて, 変 換 器 の 各 素 子 のパ<br />

ラメータを 計 算 し, 変 換 器 全 体 の 効 率 と 体 積 ,パワー 密 度<br />

を 導 出 する。 効 率 <strong>ANPC</strong> は 変 換 器 の 各 素 子 の 損 失 総 和 P Loss<br />

から(1)~(2) 式 で, 変 換 器 体 積 Vol <strong>ANPC</strong> は 各 素 子 の 体 積 総 和 か<br />

ら(3) 式 で, 変 換 器 のパワー 密 度 <strong>ANPC</strong> は 各 素 子 のパワー 密 度<br />

の 総 和 から(4) 式 で 得 られる。<br />

P P P<br />

.............................................................(1)<br />

Loss<br />

Sw<br />

C L<br />

P P<br />

in Loss<br />

<br />

<strong>ANPC</strong><br />

..........................................................(2)<br />

Pin<br />

Vol<br />

<br />

<strong>ANPC</strong><br />

<strong>ANPC</strong><br />

Vol<br />

sw<br />

sw<br />

Vol<br />

C<br />

C<br />

H<br />

Vol<br />

H<br />

........................................ (3)<br />

<br />

...................................................(4)<br />

ここで,P sw は 半 導 体 素 子 の 損 失 ,P C はキャパシタ 素 子 の<br />

E dc<br />

損 失 , P in は 変 換 器 の 入 力 電 力 ,Vol sw は 半 導 体 素 子 の 体 積 ,<br />

Vol C はキャパシタ 素 子 の 体 積 ,Vol H はヒートシンクの 体 積 ,<br />

sw は 半 導 体 素 子 のパワー 密 度 , C はキャパシタ 素 子 のパワ<br />

ー 密 度 , H はヒートシンクのパワー 密 度 である。<br />

さ ら に , (3) 式 と 実 際 の 変 換 器 体 積 か ら 実 装 率<br />

PVR(Package Volumetric Ratio)を 定 義 する。 実 装 率 は, 変 換<br />

器 の 実 際 の 体 積 に 対 する 変 換 器 素 子 の 体 積 が 占 める 割 合 で,<br />

この 値 が 1 に 近 いほど 部 品 の 集 積 化 が 大 きいことを 示 し,<br />

(5) 式 で 表 される。<br />

Vol<br />

PVR ...............................(5)<br />

Conv Conv<br />

Conv<br />

<br />

C 2<br />

C 3<br />

H<br />

Cell2<br />

W<br />

S 5<br />

S 6<br />

C 1<br />

S 7<br />

S 8<br />

ここで,Vol は 変 換 器 の 各 素 子 の 体 積 の 総 和 ,Conv H は<br />

D<br />

<br />

Cell1<br />

Fig.1. Five-level <strong>ANPC</strong> inverter circuit topology.<br />

Input voltage<br />

Output voltage<br />

Output current<br />

Switching<br />

device<br />

Cell1<br />

Cell2<br />

Flying capacitor<br />

DC smoothing<br />

capacitor<br />

Table 1 Design parameters.<br />

(a) converter specification<br />

350V Rated power<br />

200V Output frequency<br />

29A Switching frequency<br />

(b) device lists<br />

S 3<br />

S 1<br />

S 2<br />

S 4 V out<br />

10kW<br />

50Hz<br />

20kHz<br />

MOSFET:IRFP4668pBF(IR)<br />

MOSFET:IXFB170N30P(IXYS)<br />

EEUEE2C331<br />

5 parallel connection (Panasonic)<br />

ESMQ251VSN182MA45S<br />

2 parallel connection (Nippon chemi-con)

変 換 器 の 高 さ,Conv W は 変 換 器 の 幅 ,Conv D は 変 換 器 の 奥 行<br />

きである。 実 体 積 を 理 論 体 積 と 実 装 率 を 用 いて 表 すことで,<br />

回 路 トポロジーが 小 型 化 に 寄 与 する 部 分 と 実 装 技 術 により<br />

小 型 化 する 部 分 を 分 離 して 考 えることが 出 来 る。<br />

4. 試 作 機 による 評 価<br />

Table 1 の 変 換 器 の 試 作 と Fig.2 の 変 換 器 設 計 チャートを<br />

用 いて 10kW の 3 <strong>相</strong> <strong>ANPC</strong> インバータを 試 作 し, 体 積 につ<br />

いて 検 討 した。なお, 今 回 は, 変 換 器 設 計 は 主 回 路 部 分 の<br />

みとし,リアクトルは 考 慮 しない。 主 回 路 部 分 は 4 層 のプ<br />

リント 基 板 を 用 いて 試 作 し, 効 率 が 高 いため 放 熱 フィンは<br />

縦 型 のものを 用 いている。<br />

実 験 結 果<br />

Fig.3 に,3 <strong>相</strong> 10kW <strong>ANPC</strong> インバータの 動 作 波 形 を 示 す。<br />

Fig.3 より 出 力 電 流 は 良 好 な 正 弦 波 が 出 力 されている。また,<br />

出 力 線 間 電 圧 は 直 流 中 点 を 基 準 とする 出 力 <strong>相</strong> 電 圧 は 指 令 値<br />

に 追 従 し,9 <strong>レベル</strong>の 出 力 <strong>相</strong> 電 圧 波 形 が 得 られた。さらに,<br />

フライングキャパシタ 電 圧 は 入 力 の 1/4 である 87.5V になっ<br />

ており,5 <strong>レベル</strong> <strong>ANPC</strong> インバータの 基 本 動 作 を 確 認 した。<br />

実 装 した 最 大 効 率 は 出 力 9.2kW のとき 98.6%であり, 理 論<br />

解 析 (98.7% at 9.2kW 出 力 )とよく 一 致 している。<br />

体 積 比 較<br />

Fig.4 に Table1 の 条 件 を 用 いて 設 計 した 変 換 器 を,Fig.5<br />

に 変 換 器 の 理 論 体 積 と 実 体 積 を 比 較 した 結 果 示 す。Fig.5 よ<br />

り,5 <strong>レベル</strong> <strong>ANPC</strong> インバータの 理 論 体 積 が 0.9dm 3 , 実 体<br />

積 が 1.55dm 3 となった。ここで, 実 際 の 変 換 器 体 積 は, 変 換<br />

器 の 幅 と 奥 行 きを 主 回 路 基 板 の 幅 と 奥 行 きとして, 変 換 器<br />

の 高 さを 実 装 した 部 品 のなかで 最 も 高 い 素 子 の 高 さとして<br />

導 出 を 行 なった。 理 論 体 積 を 用 い た パ ワ ー 密 度 は<br />

10.2kW/dm 3 であり, 実 際 は 5.9kW/dm 3 となった。(5) 式 を 用<br />

いて 実 装 率 を 求 めると 0.58 となった。 実 体 積 の 解 析 結 果 よ<br />

り, 部 品 の 配 置 , 配 線 によって 生 じた 空 間 体 積 は 実 機 の 40%<br />

を 占 めている。この 空 間 体 積 は, 変 換 器 のヒートシンクの<br />

熱 設 計 や 冷 却 方 式 に 大 きく 依 存 し,パッケージング 技 術 と<br />

して 最 適 化 する 余 地 がある。<br />

5. 結 論<br />

本 論 文 では, 実 装 率 を 導 入 することによって 回 路 トポロ<br />

ジーにより 小 型 化 に 寄 与 する 部 分 と 実 装 技 術 により 小 型 化<br />

に 寄 与 する 部 分 を 分 離 する 試 みを 行 なった。 実 装 率 を 向 上<br />

させるには 熱 処 理 とパターンの 引 き 回 しなどが 重 要 となる。<br />

今 後 は, 変 換 器 のヒートシンクの 熱 設 計 と 実 装 率 につい<br />

て 検 討 を 行 なう。<br />

文 献<br />

(1) 樫 原 有 吾 ・ 伊 東 淳 一 : 電 学 論 D, Vol 131, No12 ,2011<br />

(2) 樫 原 有 吾 ・ 伊 東 淳 一 :SPC-11-157, 2011<br />

(3) J. W. Kolar, etc.: IPEMC 2009-China, 2009<br />

Deptt 0.5dm<br />

Hight 0.5dm<br />

Input<br />

Specification<br />

Device parameters<br />

Semiconductor<br />

Losses Prediction<br />

Capacitor<br />

Design Parameter (ripple current, capacity, loss, volume)<br />

& selection<br />

Inductor<br />

Design parameter (inductor, ripple current, loss, volume)<br />

& selection<br />

Heatsink<br />

Design parameter (thermal resistance, volume)<br />

& selection<br />

Output<br />

Efficiency & Volume<br />

& Power density<br />

Fig.2. Inverter design procedure<br />

Output line voltage [200V/div]<br />

Flying capacitor voltage [50V/div]<br />

Output current [50A/div]<br />

Fig.3. Experimental waveform.<br />

Width 2dm<br />

(a) Top side<br />

Width 2dm<br />

(b) Front side<br />

Fig.4. A three-phase five-level <strong>ANPC</strong> inverter.<br />

5msec/div<br />

Heatsink<br />

DC smoothing capacitor<br />

Flying capacitor<br />

Calculation<br />

Switching device<br />

Connecter<br />

value<br />

Current transducer<br />

Measurrement<br />

Terminal block<br />

Space<br />

value<br />

0 0.5 1 1.5 2<br />

Volume[dm 3 ]<br />

Fig.5. Volume of <strong>ANPC</strong> inverter.