在FPGA 平台上实现实时波束形成器 - Xilinx

在FPGA 平台上实现实时波束形成器 - Xilinx

在FPGA 平台上实现实时波束形成器 - Xilinx

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

算两个输出项 ℑ(υ) 和 ℜ(υ) 之一。<br />

计算这两个输出项需要两个时钟周期。<br />

每个时钟周期内都为 DSP 提供一个独<br />

一无二 的操作码 。 让 我们看看数据<br />

ℜ(υ) 的计算过程。第一个时钟周期<br />

里,计算得出 cos(Φ) x ℜ(xin ) 的乘积<br />

并存储在 DSP48 乘积(或称 p)寄存器<br />

中。<br />

第二个时钟周期里,算出 sin(Φ)<br />

x ℑ(xin ) 结果,然后从 p 寄存器所存<br />

储 的数值 中 减去该结果, 得出最终的<br />

输出项。通过类似 的计算过程可得出<br />

ℑ(υ)。内部单元上使用 DSP48 嵌入<br />

式模块而不使用基于 CORDIC 的方<br />

法,可减少计算中的相位延迟,同时还<br />

使实现所需的 FPGA 逻辑架构的数量<br />

降为最低。表 1 所示为 QRD 实现<br />

中 主 要 功 能单元范围的 明细,同时<br />

还显示了该设计的总范围。<br />

内部单元所需的 cos(Φ)、sin(Φ)、<br />

cos(Θ) 和 sin(Θ) 项是用一个简单的<br />

LUT 计算出来的,这个 LUT 将边界单<br />

元中矢量单元计算得出的 Φ 和 Θ 角<br />

映射到相应的正弦和余弦中。线性插补<br />

法被应用于 LUT 的输出样本,以增加<br />

从角到 振幅的 映射的 精确度,同时将<br />

LUT 本身限制在单个 Block RAM 上。<br />

QRD 处理器的输入阵列的行和列<br />

的维数可在运行时进行动态调节,方法<br />

是将新维数写到 FPGA 控制平台中的控<br />

制寄存器上。<br />

表 2 提供了输入数据组几个配置<br />

的时序信息。<br />

设计流程<br />

我们的 QRD 实现使用了基 于<br />

<strong>Xilinx</strong> System Generator for DSP 模式<br />

的设计流程。除了为开发 FPGA 信号处<br />

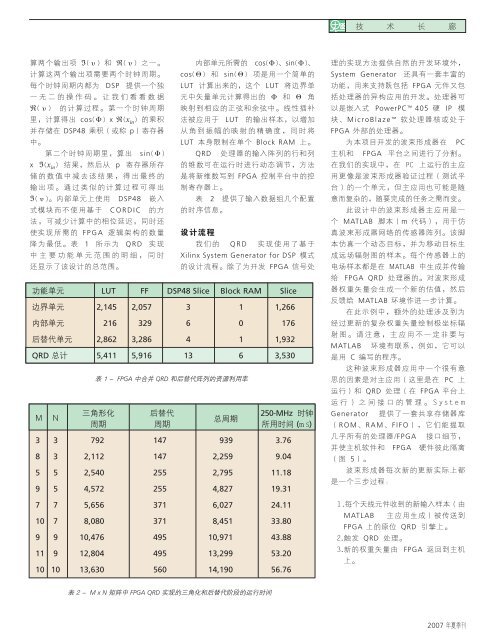

功能单元 LUT FF DSP48 Slice Block RAM Slice<br />

边界单元 2,145 2,057 3 1 1,266<br />

内部单元 216 329 6 0 176<br />

后替代单元 2,862 3,286 4 1 1,932<br />

QRD 总计 5,411 5,916 13 6 3,530<br />

M N<br />

表 1 - FPGA 中合并 QRD 和后替代阵列的资源利用率<br />

三角形化 后替代<br />

250-MHz 时钟<br />

总周期<br />

周期 周期 所用时间 (m s)<br />

3 3 792 147 939 3.76<br />

8 3 2,112 147 2,259 9.04<br />

5 5 2,540 255 2,795 11.18<br />

9 5 4,572 255 4,827 19.31<br />

7 7 5,656 371 6,027 24.11<br />

10 7 8,080 371 8,451 33.80<br />

9 9 10,476 495 10,971 43.88<br />

11 9 12,804 495 13,299 53.20<br />

10 10 13,630 560 14,190 56.76<br />

表 2 - M x N 矩阵中 FPGA QRD 实现的三角化和后替代阶段的运行时间<br />

技 术 长 廊<br />

理的实现方法提供自然的开发环境外,<br />

System Generator 还具有一套丰富的<br />

功能,用来支持既包括 FPGA 元件又包<br />

括处理器的异构应用的开发。处理器可<br />

以是嵌入式 PowerPC 405 硬 IP 模<br />

块、MicroBlaze 软处理器核或处于<br />

FPGA 外部的处理器。<br />

为本项目开发的波束形成器在 PC<br />

主机和 FPGA 平台之间进行了分割。<br />

在我们的实现中,在 PC 上运行的主应<br />

用更像是波束形成器验证过程(测试平<br />

台)的一个单元,但主应用也可能是随<br />

意而复杂的,随要完成的任务之需而变。<br />

此设计中的波束形成器主应用是一<br />

个 MATLAB 脚本(m 代码),用于仿<br />

真波束形成器网络的传感器阵列。该脚<br />

本仿真一个动态目标,并为移动目标生<br />

成远场辐射图的样本。每个传感器上的<br />

电场样本都是在 MATLAB 中生成并传输<br />

给 FPGA QRD 处理器的。对波束形成<br />

器权重矢量会生成一个新的估值,然后<br />

反馈给 MATLAB 环境作进一步计算。<br />

在此示例中,额外的处理涉及到为<br />

经过更新的复杂权重矢量绘制极坐标辐<br />

射 图。请注意, 主 应用不一定非 要 与<br />

MATLAB 环境有联系,例如,它可以<br />

是用 C 编写的程序。<br />

这种波束形成器应用中一个很有意<br />

思的因素是对主应用(这里是在 PC 上<br />

运行)和 QRD 处理(在 FPGA 平台上<br />

运 行)之间接口的管理。System<br />

Generator 提供了一套共享存储器库<br />

(ROM、RAM、FIFO),它们能提取<br />

几乎所有的处理器/FPGA 接口细节,<br />

并使主机软件和 FPGA 硬件彼此隔离<br />

(图 5)。<br />

波束形成器每次新的更新实际上都<br />

是一个三步过程:<br />

1.每个天线元件收到的新输入样本(由<br />

MATLAB 主应用生成)被传送到<br />

FPGA 上的原位 QRD 引擎上。<br />

2.触发 QRD 处理。<br />

3.新的权重矢量由 FPGA 返回到主机<br />

上。<br />

2007 年夏季刊