SDR SDRAM 的上电åˆÂ始化原ç†与控制电路的设计实现 - SOC@Fudan

SDR SDRAM 的上电åˆÂ始化原ç†与控制电路的设计实现 - SOC@Fudan

SDR SDRAM 的上电åˆÂ始化原ç†与控制电路的设计实现 - SOC@Fudan

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

<strong>SDR</strong>C_liteBeta2.1SPEC inilialization<br />

FudanUniversity 08300720451 梁 晨<br />

<strong>SDR</strong> <strong>SDR</strong>AM 的 上 电 初 始 化 原 理 与 控 制 电 路 的 设 计 实 现<br />

1. <strong>SDR</strong> <strong>SDR</strong>AM 的 上 电 初 始 化 原 理<br />

<strong>SDR</strong> <strong>SDR</strong>AM 必 须 要 用 规 定 的 方 式 进 行 上 电 与 初 始 化 , 以 保 证 器 件 正 常 工 作 。 同 时 , 对 模 式 寄 存 器 的 设<br />

置 也 发 生 在 初 始 化 期 间 。<br />

1.1 Jedec 21-C 标 准 与 Intel PC100 标 准 的 规 定<br />

早 期 的 <strong>SDR</strong>AM、 当 代 的 韩 系 、 日 系 、 台 系 <strong>SDR</strong>AM 都 符 合 这 里 的 描 述 。 为 保 证 兼 容 性 , 本 次 设 计 采 用 这<br />

个 传 统 初 始 化 标 准 , 但 tMRD 周 期 取 为 2 以 匹 配 当 代 的 器 件 。<br />

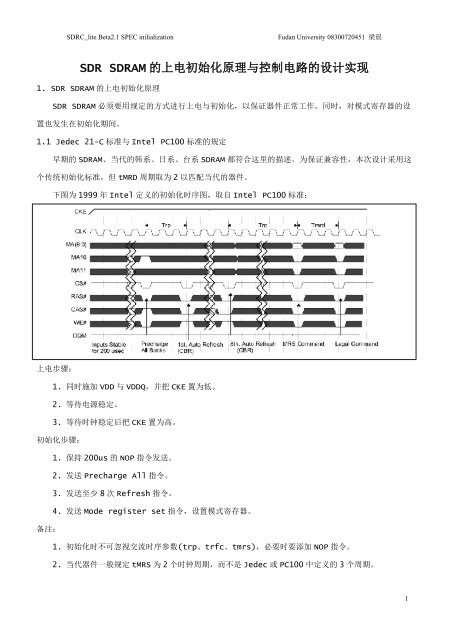

下 图 为 1999 年 Intel 定 义 的 初 始 化 时 序 图 , 取 自 Intel PC100 标 准 :<br />

上 电 步 骤 :<br />

1. 同 时 施 加 VDD 与 VDDQ, 并 把 CKE 置 为 低 。<br />

2. 等 待 电 源 稳 定 。<br />

3. 等 待 时 钟 稳 定 后 把 CKE 置 为 高 。<br />

初 始 化 步 骤 :<br />

1. 保 持 200us 的 NOP 指 令 发 送 。<br />

2. 发 送 Precharge All 指 令 。<br />

3. 发 送 至 少 8 次 Refresh 指 令 。<br />

4. 发 送 Mode register set 指 令 , 设 置 模 式 寄 存 器 。<br />

备 注 :<br />

1. 初 始 化 时 不 可 忽 视 交 流 时 序 参 数 (trp、trfc、tmrs), 必 要 时 要 添 加 NOP 指 令 。<br />

2. 当 代 器 件 一 般 规 定 tMRS 为 2 个 时 钟 周 期 , 而 不 是 Jedec 或 PC100 中 定 义 的 3 个 周 期 。<br />

1

<strong>SDR</strong>C_liteBeta2.1SPEC inilialization<br />

FudanUniversity 08300720451 梁 晨<br />

3. 对 于 Samsung、Zentel 的 器 件 , 可 以 只 Refresh 两 次 。<br />

4. Elpida、Zentel 等 公 司 建 议 在 初 始 化 时 把 DQM 置 为 1, 以 防 止 可 能 的 数 据 冲 突 。 这 一 点 在 Intel<br />

定 义 的 时 序 图 中 也 有 体 现 。PC100 规 定 在 第 一 条 有 效 指 令 发 送 后 ,DQ 自 动 变 为 高 阻 , 但 这 之 前 的 状 态 未 规<br />

定 。<br />

5. 理 论 上 只 要 所 有 Bank 都 空 闲 , 就 可 以 设 置 Mode register。 但 一 般 情 况 下 , 初 始 化 后 Mode<br />

register 不 再 需 要 改 变 。Mode register 中 设 置 了 CAS Latency、Burst Length 等 重 要 参 数 , 这 些<br />

通 过 数 据 通 过 地 址 线 传 送 , 详 细 过 程 将 在 后 面 的 章 节 中 描 述 。<br />

1.2 Micron、ISSI 等 当 代 美 系 <strong>SDR</strong> <strong>SDR</strong>AM 的 改 进<br />

Micron、ISSI 等 公 司 的 <strong>SDR</strong>AM 产 品 中 , 时 钟 稳 定 后 的 初 始 等 待 时 间 缩 短 为 100us, 同 时 refresh<br />

的 次 数 减 少 为 至 少 2 次 。 对 于 Micron 器 件 , 时 钟 稳 定 后 ,CKE 可 以 在 100us 的 等 待 期 间 上 升 , 然 后 保 持<br />

NOP 发 送 ; 而 对 于 ISSI 器 件 , 时 钟 稳 定 后 ,CKE、DQM 必 须 上 升 为 1, 然 后 才 开 始 100us 的 NOP 发 送 。<br />

Micron 为 <strong>SDR</strong>AM 做 的 verilog 模 型 流 传 甚 广 ,Xilinx、Altera、Lattice 等 FPGA 厂 商 提 供 的<br />

参 考 设 计 一 般 都 遵 循 Micron 手 册 中 的 初 始 化 步 骤 。<br />

下 图 为 Micron <strong>SDR</strong>AM 的 初 始 化 时 序 图 , 取 自 Micron 的 器 件 手 册 :<br />

2

<strong>SDR</strong>C_liteBeta2.1SPEC inilialization<br />

FudanUniversity 08300720451 梁 晨<br />

2. 上 电 初 始 化 控 制 电 路 (MCB_INI_CTRL) 的 设 计 概 要<br />

本 次 设 计 使 用 的 初 始 化 控 制 电 路 , 包 括 初 始 化 状 态 机 (MCB_INI_FSM) 、 初 始 化 等 待 计 数 器<br />

(i_ini_w_cnt)、 初 始 化 refresh 次 数 计 数 器 (i_ref_n_cnt)、 初 始 化 命 令 延 时 计 数 器 (i_cmd_cnt)<br />

四 个 模 块 。 它 们 的 连 接 关 系 如 下 图 :<br />

初 始 化 等 待 计 数 器 (i_ini_w_cnt)、 初 始 化 refresh 次 数 计 数 器 (i_ref_n_cnt)、 初 始 化 命 令 延 时<br />

计 数 器 (i_cmd_cnt), 与 初 始 化 状 态 机 协 同 工 作 , 共 同 完 成 初 始 化 的 控 制 。 初 始 化 等 待 计 数 器 控 制 100us<br />

或 200us 的 初 始 化 等 待 ; 初 始 化 refresh 次 数 计 数 器 控 制 refresh 的 次 数 ; 初 始 化 命 令 延 时 计 数 器 保 证<br />

trp、trfc、tmrd 等 指 令 延 时 参 数 被 满 足 。 用 户 可 以 通 过 verilog 参 数 改 变 这 三 个 计 数 器 的 设 置 。<br />

初 始 化 状 态 机 (MCB_INI_FSM) 采 用 Moore 模 型 , 输 出 只 与 当 前 状 态 有 关 , 以 保 证 输 出 控 制 信 号 与 时 钟<br />

同 步 。 状 态 机 代 码 风 格 将 采 用 Altera 推 荐 的 2 段 式 写 法 , 时 序 的 状 态 更 新 为 一 段 , 组 合 的 Next State<br />

Logic 与 Output Logic 为 一 段 。 初 始 化 状 态 机 的 状 态 跳 转 顺 序 基 本 按 照 Jedec 的 <strong>SDR</strong>AM 初 始 化 规 定 。<br />

此 处 假 设 在 系 统 复 位 后 , 电 源 与 时 钟 信 号 已 经 稳 定 , 状 态 机 主 要 控 制 初 始 化 部 分 而 非 上 电 部 分 。 各 个 状 态 与<br />

对 应 的 输 出 如 下 表 :<br />

状 态 名 输 出 的 指 令 信 号 输 出 的 其 他 控 制 信 号<br />

i_st_nop ( 延 时 状 态 )<br />

i_st_prea i_prea i_cmd_cnt_sclr<br />

i_st_trp ( 延 时 状 态 )<br />

i_st_ref i_ref i_cmd_cnt_sclr<br />

i_st_trfc ( 延 时 状 态 )<br />

i_st_lmr i_lmr i_cmd_cmr_sclr<br />

i_st_tmrd ( 延 时 状 态 )<br />

i_st_ready ( 初 始 化 完 成 状 态 ) i_ready<br />

3

<strong>SDR</strong>C_liteBeta2.1SPEC inilialization<br />

FudanUniversity 08300720451 梁 晨<br />

trp、trfc、tmrd 分 别 是 Precharge、Refresh、Mode Register Set 后 的 延 时 。 在 此 期 间 不 能<br />

发 送 NOP 以 外 的 指 令 。 按 照 器 件 手 册 的 规 定 ,trp、trfc、tmrd 的 单 位 从 ns 折 算 为 时 钟 周 期 时 , 应 该 向<br />

上 取 整 。 假 设 Trp 折 合 为 x 个 时 钟 周 期 , 那 么 从 i_st_prea 进 入 i_st_trp 后 , 就 应 停 留 x-1 个 时 钟 周<br />

期 ( 因 为 i_st_prea 自 身 也 占 用 了 一 个 周 期 )。 如 果 x 恰 好 为 1, 则 i_st_trp 状 态 不 存 在 , 电 路 参 数 决<br />

定 了 ,x 的 大 小 就 决 定 了 , 是 否 可 能 进 入 i_st_trp 只 与 电 路 参 数 有 关 , 这 个 判 断 不 会 映 射 为 实 体 逻 辑 电 路 ,<br />

在 下 文 中 的 状 态 转 换 图 中 用 蓝 色 条 件 标 出 。trfc、tmrd 对 状 态 跳 转 的 影 响 同 理 于 trp。<br />

在 系 统 复 位 时 , 进 入 IDEL 状 态 ( 即 i_st_nop); 完 成 100us 或 200us 的 初 始 化 等 待 后 , 进 行<br />

Precharge All; 满 足 trp 延 时 后 , 进 行 refresh; 满 足 trfc 延 时 后 , 如 果 达 到 需 要 的 refresh 次 数 ,<br />

就 进 行 mode register set, 否 则 , 继 续 refresh;mode register set 后 , 经 过 tmrd 延 时 , 最 终<br />

进 入 ready 状 态 , 初 始 化 完 成 。<br />

所 有 的 延 时 等 待 状 态 中 , 都 不 发 指 令 信 号 ;i_st_prea 中 发 起 i_prea;i_st_ref 中 发 起 i_ref;<br />

i_st_lmd 中 发 起 i_lmr;i_prea、i_ref、i_lmr 信 号 将 通 过 信 号 通 路 (MCB_SIG_FF) 编 码 为 <strong>SDR</strong>AM<br />

命 令 。 初 始 化 完 成 后 , 发 出 i_ready, 这 之 后 用 户 的 请 求 才 会 被 响 应 。 初 始 化 状 态 机 的 状 态 转 换 图 如 下 :<br />

注 : 上 图 中 , 蓝 色 的 条 件 与 器 件 的 时 序 和 系 统 工 作 频 率 参 数 有 关 , 不 会 映 射 为 电 路 逻 辑 。<br />

4

<strong>SDR</strong>C_liteBeta2.1SPEC inilialization<br />

FudanUniversity 08300720451 梁 晨<br />

A1 版 本 历 史 :<br />

版 本 时 间 说 明<br />

<strong>SDR</strong>C_lite spec alpha2 2012/03/30 参 照 <strong>SDR</strong>AM 的 业 界 标 准 与 alpha2 版 初 始 化 单 元 的<br />

设 计 实 现 编 写 。<br />

<strong>SDR</strong>C_lite spec beta2.1 2012/04/14 包 含 beta2.1 版 设 计 的 一 些 更 新 ;verilog 仿 真 、<br />

FPGA 综 合 部 分 将 另 外 在 设 计 实 现 文 档 中 描 述 。<br />

A2 参 考 文 献 :<br />

[1] Intel, PC <strong>SDR</strong>AM Specification, Revision 1.7, November 1999. (Intel PC100)<br />

[2] Jedec, Jedec standard No.21-C. (Jedec <strong>SDR</strong>AM standard)<br />

[3] TI, TMS626812 datasheet, 1997. ( 早 期 的 <strong>SDR</strong>AM, 只 有 两 个 bank)<br />

[4] Micron, 64Mb x4, x8, x16 <strong>SDR</strong> <strong>SDR</strong>AM Features, Rev. Q, February 2012.<br />

[5] ISSI, 1 Meg Bits x 16 Bits x 4 Banks (64-MBIT) SYNCHRONOUS DYNAMIC RAM, Rev.<br />

I, Dec. 2011.<br />

[6] Elpida, User's manual HOW TO USE <strong>SDR</strong>AM, rev 8.1, March 2009.<br />

[7] Hynix, <strong>SDR</strong>AM DEVICE OPERATION, rev1.1, sep. 2003.<br />

[8] Samsung, CMOS <strong>SDR</strong>AM Device Operations, rev 0.2, 1999.<br />

[9] Windbond, W9864G6JT 1M * 4 BANKS * 16 BITS <strong>SDR</strong>AM, Revision A01, dec. 2011.<br />

[10] Nanya, NT5SV32M8CS NT5SV16M16CS 256Mb Synchronous DRAM, REV 1.4, dec.2011<br />

[11] Xilinx, xapp134, Synthesizable High Performance <strong>SDR</strong>AM Controller, 2000.<br />

[12] Altera, white paper <strong>SDR</strong> <strong>SDR</strong>AM Controller, version 1.1, February 2001.<br />

[13] Lattice, RD1010, <strong>SDR</strong> <strong>SDR</strong>AM Controller, rev 04.6, April 2011.<br />

[14] Zentel, A3V64S40FTP 64Mb Synchronous DRAM Specification, rev 1.0, Aug. 2011.<br />

[15] Altera, Quartus II Handbook, Ch10, Recommended HDL Coding Styles, rev 10.1,<br />

Dec. 2011.<br />

[16] Xilinx, UG627 XST user guide, Chapter 03:XST HDL Coding Techniques, rev 12.4,<br />

Dec. 2010.<br />

[17] Pong P. Chu, FPGA Prototyping Using Verilog Examples, Wiley-Interscience, June<br />

2008.<br />

5