2a Lista de exercÃcios

2a Lista de exercÃcios

2a Lista de exercÃcios

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

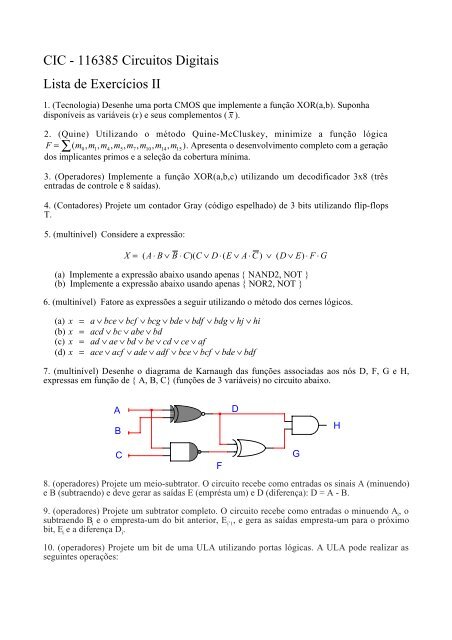

S1 S2 ULA0 0 F=A+B0 1 F= and B1 0 F=A xor B1 1 F = A - B11. (operadores) Implemente a função maioria com 4 variáveis, ou seja, F é 1 se ao menos 3variáveis são 1, utilizando para isso apenas multiplexadores 2x1.12. (operadores) Implemente um full-ad<strong>de</strong>r utilizando um <strong>de</strong>codificador 3x8 e um mínimo <strong>de</strong>portas lógicas auxiliares.13. (operadores) Dada a função F( abcd , , , ) =∑m( 0, 3, 5, 7, 11, 12, 13, 15 ),(a) implementar com um multiplexador <strong>de</strong> 16x1(b) implementar com um multiplexador <strong>de</strong> 8x1, usando d como entrada do mux(c) implementar com um mux <strong>de</strong> 4x1, utilizando C e D portas auxiliares como entrada.14. (flip-flops) Consi<strong>de</strong>re o flip-flop D sensível a borda <strong>de</strong> <strong>de</strong>scida. Acrescente sinais <strong>de</strong> set e reset,<strong>de</strong> forma que quando set = 1, Q = 1 e Q’ = 0, in<strong>de</strong>pen<strong>de</strong>nte <strong>de</strong> Clk e D. Quando reset = 1, Q = 0 eQ’ = 1, in<strong>de</strong>pen<strong>de</strong>nte <strong>de</strong> Clk e D.ClkQpos\QposD15. (flip-flops) Mostre como implementar um flip-flop JK a partir <strong>de</strong> um FF Toggle (um FF T temuma entrada T e saídas Q e Q’).16. (flip-flops) Implemente um FF T a partir <strong>de</strong> um FF D.17. (flip-flops) Para o diagrama <strong>de</strong> tempos abaixo, <strong>de</strong>senhe as respectivas formas <strong>de</strong> onda da saídaconsi<strong>de</strong>rando que o circuito:(a) é um FF D sensível à borda <strong>de</strong> <strong>de</strong>scida(b) é um FF mestre-escravo(c) é um FF D sensível à borda <strong>de</strong> subida(d) é um latch sensível ao nível um.

ClkD18. (multinível&operadores) Consi<strong>de</strong>re a expressão a seguir:x = acd ∨bcd ∨abc ∨abd ∨ef ∨ef(a) fatore a expressão utilizando o método dos cernes lógicos.(b) suponha que nosso laboratório disponha apenas <strong>de</strong> meio-somadores (half-ad<strong>de</strong>rs) einversores. Implemente o circuito fatorado procurando minimizar o número <strong>de</strong> dispositivosutilizados.19. (operadores) A ACTEL é um fabricante <strong>de</strong> circuitos programáveis (FPGA) que utilizacomo célula básica para projeto um circuito baseado em multiplexadores 2:1, apresentadoabaixo.(a) escreva a expressão Booleana da saída OUT em funçãodas entradas (A0, A1, SA, etc.).(b) implemente um meio-somador multiplexado com estacélula. Este circuito produz na saída ou a soma <strong>de</strong>dois bits x,y ou o vai-um, <strong>de</strong>pendo <strong>de</strong> um sinal <strong>de</strong>controle op. Se op = 1, temos saída = x + y; se op =0, saída = x · y. Suponha disponíveis as entradasdiretas (x) ou negadas (x’).A0A1SAB0B1SB01 SZ01 SZ01 SS0ZS1OUT20. (flip-flops) Explique o funcionamento do FF aolado com suas palavras. Indique o que ocorre quandoo relógio está nos níveis 0 e 1, em qual transição odado é armazenado e porque ele não muda o valorarmazenado <strong>de</strong>pois da transição.21. (contadores) Projete um contador <strong>de</strong> dois bits quecircule pelos estados:11 -> 10 -> 01 -> 11 -> ...empregando flip-flops JK.ClkXYQQ'D