Introdução Sub-circuitos para portas lógicas

Introdução Sub-circuitos para portas lógicas

Introdução Sub-circuitos para portas lógicas

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

Código do Laboratório: AP06<br />

Data: 16/04/2009 Turma D<br />

Nomes: Bruno Jurkovski – Cartão número 172865<br />

Marcos Vinicius Cavinato – Cartão número 171774<br />

<strong>Introdução</strong><br />

O principal objetivo da aula prática 06 foi a simulação de <strong>portas</strong> <strong>lógicas</strong> CMOS com<br />

SPICE e fazer a análise temporal e elétrica dessas <strong>portas</strong>. Inicialmente, fizemos a leitura do<br />

tutorial II, <strong>para</strong> entender como descrever uma porta lógica como uma “sub-rotina” que pode<br />

ser utilizada dentro de uma outra porta lógica. Descrevemos três <strong>portas</strong> <strong>lógicas</strong>: inversor,<br />

nand de 2 entradas e nor de 3 entradas e fizemos as medições temporais e elétrica em cada<br />

uma. Fomos capazes também de descrever um meio-somador e uma função de carry, a<br />

partir das três <strong>portas</strong> <strong>lógicas</strong> primeiramente implementadas.<br />

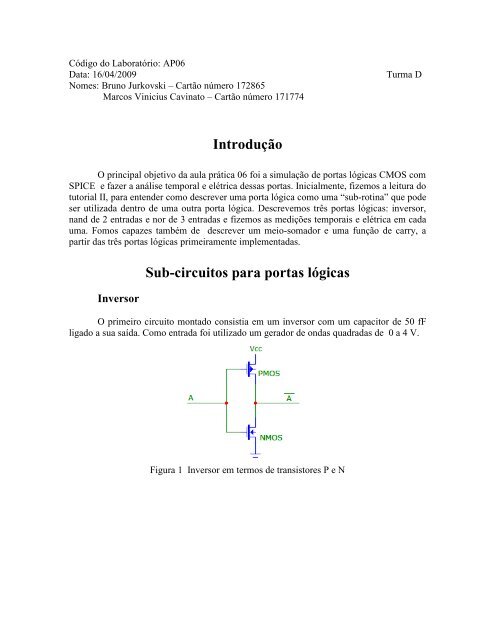

Inversor<br />

<strong>Sub</strong>-<strong>circuitos</strong> <strong>para</strong> <strong>portas</strong> <strong>lógicas</strong><br />

O primeiro circuito montado consistia em um inversor com um capacitor de 50 fF<br />

ligado a sua saída. Como entrada foi utilizado um gerador de ondas quadradas de 0 a 4 V.<br />

Figura 1 Inversor em termos de transistores P e N

Gráfico 1 Combinações de entrada (v(2)) e respectiva saída (v(3)) <strong>para</strong> o inversor<br />

Descrição Spice - Inversor<br />

.include cmos7tm.mod<br />

vcc 1 0 4<br />

vin1 2 0 pulse(0 4 0n 0.5n 0.5n 14n 30n)<br />

**** Inversor ****<br />

.subckt inv in out vcc<br />

Mp1 vcc in out vcc modp<br />

Mn1 out in 0 0 modn<br />

.ends inv<br />

**** Circuito *****<br />

x1 2 3 1 inv<br />

c1 3 0 50f<br />

.tran 1n 45n<br />

.print tran v(2) v(3)<br />

.end

Gráfico 2 Medidas temporais do sinal de saída do inversor (na subida)<br />

t dlh =1,25ns e t R=3,75 ns<br />

Gráfico 3 Medidas temporais do sinal de saída do inversor (na descida)<br />

t dhl=0,5 ns e t F=1,0ns

Tabela com os resultados encontrados<br />

Tempo Vi Vf<br />

tdlh 1,25 ns 0 V 2 V<br />

tdhl 0,5 ns 4 V 2 V<br />

tr 3,75 ns 0 V 3,6 V<br />

tf 1 ns 4 V 0,4 V<br />

Tdlh e Tr são maiores que tdhl e tf pois os transistores P são mais lerdos do que os<br />

transistores N. Assim, há um maior tempo de atraso na transição de 0 (lógico) <strong>para</strong> 1<br />

(lógico) do que na transição de 1 (lógico) <strong>para</strong> o 0 (lógico).<br />

NAND com duas entradas<br />

O segundo circuito montado consistia em um NAND de duas entradas com um<br />

capacitor de 50 fF ligado a sua saída. Como entrada foram utilizados dois geradores de<br />

ondas quadradas de 0 a 4 V.<br />

Figura 2 NAND de duas entradas em termos de transistores P e N

Gráfico 4 Combinações de entrada (v(2) e v(3)) e saída (v(4)) <strong>para</strong> o NAND2<br />

Decrição Spice - NAND2<br />

.include cmos7tm.mod<br />

vcc 1 0 4<br />

vin1 2 0 pulse(0 4 0n 0.5n 0.5n 20n 40n)<br />

vin2 3 0 pulse(0 3.9 0n 0.5n 0.5n 40n 80n)<br />

**** NAND2 ****<br />

.subckt nand2 in1 in2 out vcc<br />

Mp1 vcc in1 out vcc modp<br />

Mp2 vcc in2 out vcc modp<br />

Mn1 999 in1 0 0 modn<br />

Mn2 out in2 999 0 modn<br />

.ends nand2<br />

**** Circuito *****<br />

x1 2 3 4 1 nand2

c1 4 0 50f<br />

.tran 1n 160n<br />

.print tran v(2) v(3) v(4)<br />

.end<br />

Gráfico 5 Medidas temporais do sinal de saída do NAND2 (na subida)<br />

t dlh=3,5ns e t R=5,0ns

Gráfico 5 Medidas temporais do sinal de saída do NAND2 (na descida)<br />

t dhl=1,60 ns e t F=2,5ns<br />

Tabela com os resultados encontrados<br />

Tempo Vi Vf<br />

tdlh 3,5 ns 0 V 2 V<br />

tdhl 1,6 ns 4 V 2 V<br />

tr 5,0 ns 0 V 3,6 V<br />

tf 2,5 ns 4 V 0,4 V<br />

Tdlh e Tr são maiores que tdhl e tf pois os transistores P são mais lerdos do que os<br />

transistores N. Assim, há um maior tempo de atraso na transição de 0 (lógico) <strong>para</strong> 1<br />

(lógico) do que na transição de 1 (lógico) <strong>para</strong> o 0 (lógico). Ainda assim, a diferença entre<br />

os tempos não é tão grande pois os dois transistores P estão em <strong>para</strong>lelo, enquanto os<br />

transistores N estão em série. Transistores em <strong>para</strong>lelo acabam apresentando um menor<br />

tempo de atraso.

NOR com três entradas<br />

O terceiro circuito montado consistia em um NOR de três entradas com um<br />

capacitor de 50 fF ligado a sua saída. Como entrada foram utilizados três geradores de<br />

ondas quadradas de 0 a 4 V.<br />

Figura 3 NOR de três entradas em termos de transistores P e N

Gráfico 6 Combinações de entrada (v(2), v(3) e v(4)) e saída (v(5)) <strong>para</strong> o NOR3<br />

Descrição Spice - NOR3<br />

.include cmos7tm.mod<br />

vcc 1 0 4<br />

vin1 2 0 pulse(0 4.0 0n 0.5n 0.5n 20n 40n)<br />

vin2 3 0 pulse(0 3.9 0n 0.5n 0.5n 40n 80n)<br />

vin3 4 0 pulse(0 3.8 0n 0.5n 0.5n 80n 160n)<br />

**** NOR3 ****<br />

.subckt nor3 in1 in2 in3 out vcc<br />

Mp1 vcc in1 998 vcc modp<br />

Mp2 998 in2 997 vcc modp<br />

Mp3 997 in3 out vcc modp<br />

Mn1 out in1 0 0 modn<br />

Mn2 out in2 0 0 modn<br />

Mn3 out in3 0 0 modn<br />

.ends nor3<br />

**** Circuito *****

x1 2 3 4 5 1 nor3<br />

c1 5 0 50f<br />

.tran 1n 300n<br />

.print tran v(2) v(3) v(4) v(5)<br />

.end<br />

Gráfico 7 Medidas temporais do sinal de saída do NOR3 (na subida)<br />

t dlh =8,0 ns e t R =12,0 ns

Gráfico 8 Medidas temporais do sinal de saída do NOR3 (na descida)<br />

t dhl=0,6 ns e t F=0,8 ns<br />

Tabela com os resultados encontrados<br />

Tempo Vi Vf<br />

tdlh 8,0 ns 0 V 2 V<br />

tdhl 0,6 ns 4 V 2 V<br />

tr 12,0 ns 0,4 V 3,6 V<br />

tf 0,8 ns 3,6 V 0,4 V<br />

Tdlh e Tr são maiores que tdhl e tf pois os transistores P são mais lerdos do que os<br />

transistores N. Assim, há um maior tempo de atraso na transição de 0 (lógico) <strong>para</strong> 1<br />

(lógico) do que na transição de 1 (lógico) <strong>para</strong> o 0 (lógico). Nesta tabela os tempos de<br />

subida e descida apresentam uma grande diferença pois os transistores P estão em série,<br />

enquanto os N estão em <strong>para</strong>lelo. Assim os atrasos se acumulam, e por isso a diferença tão<br />

grande entre os tempos.<br />

Implementação de um meio-somador e do carry-out<br />

Descrição Spice de S = X!.Y + X.Y! Descrição Spice de C = X.Y

.include cmos7tm.mod<br />

vcc 1 0 4<br />

vin1 2 0 pulse(0 4.0 0n 0.5n 0.5n 20n 40n)<br />

vin2 3 0 pulse(0 3.9 0n 0.5n 0.5n 40n 80n)<br />

****** INVERSOR ***********<br />

.subckt inv in out vcc<br />

Mp1 vcc in out vcc modp<br />

Mn1 out in 0 0 modn<br />

.ends inv<br />

******** NAND2 ************<br />

.subckt nand2 in1 in2 out vcc<br />

Mp1 vcc in1 out vcc modp<br />

Mp2 vcc in2 out vcc modp<br />

Mn1 999 in1 0 0 modn<br />

Mn2 out in2 999 0 modn<br />

.ends nand2<br />

******** NOR3 ************<br />

.subckt nor3 in1 in2 in3 out vcc<br />

Mp1 vcc in1 998 vcc modp<br />

Mp2 998 in2 997 vcc modp<br />

Mp3 997 in3 out vcc modp<br />

Mn1 out in1 0 0 modn<br />

Mn2 out in2 0 0 modn<br />

Mn3 out in3 0 0 modn<br />

.ends nor3<br />

**** Circuito *****<br />

x1 2 4 1 inv<br />

x2 4 3 5 1 nand2<br />

x3 5 6 1 inv<br />

x4 3 7 1 inv<br />

x5 2 7 8 1 nand2<br />

x6 8 9 1 inv<br />

x7 6 9 9 10 1 nor3<br />

x8 10 11 1 inv<br />

.tran 1n 160n<br />

.print tran v(2) v(3) v(11)<br />

.end<br />

.include cmos7tm.mod<br />

vcc 1 0 4<br />

vin1 2 0 pulse(0 4.0 0n 0.5n 0.5n 20n 40n)<br />

vin2 3 0 pulse(0 3.9 0n 0.5n 0.5n 40n 80n)<br />

****** INVERSOR ***********<br />

.subckt inv in out vcc<br />

Mp1 vcc in out vcc modp<br />

Mn1 out in 0 0 modn<br />

.ends inv<br />

******** NAND2 ************<br />

.subckt nand2 in1 in2 out vcc<br />

Mp1 vcc in1 out vcc modp<br />

Mp2 vcc in2 out vcc modp<br />

Mn1 999 in1 0 0 modn<br />

Mn2 out in2 999 0 modn<br />

.ends nand2<br />

******** NOR3 ************<br />

.subckt nor3 in1 in2 in3 out vcc<br />

Mp1 vcc in1 998 vcc modp<br />

Mp2 998 in2 997 vcc modp<br />

Mp3 997 in3 out vcc modp<br />

Mn1 out in1 0 0 modn<br />

Mn2 out in2 0 0 modn<br />

Mn3 out in3 0 0 modn<br />

.ends nor3<br />

**** Circuito *****<br />

x1 2 3 4 1 nand2<br />

x2 4 5 1 inv<br />

.tran 1n 160n<br />

.print tran v(2) v(3) v(5)<br />

.end

Gráfico 9 Combinações de entrada (v(2) e v(3)) e saída (v(11)) <strong>para</strong> a função S

Gráfico 10 Medidas temporais do sinal de saída de S (na subida)<br />

t dlh =1,1ns e t R =2,5 ns<br />

Gráfico 11 Medidas temporais do sinal de saída de S (na descida)<br />

t dhl =3,0 ns e t F =2,5ns<br />

Tabela com os resultados encontrados<br />

Tempo Vi Vf<br />

tdlh 1,1 ns 0 V 2 V<br />

tdhl 3,0 ns 4 V 2 V<br />

tr 2,5 ns 0,4 V 3,6 V<br />

tf 2,5 ns 3,6 V 0,4 V<br />

Estes tempos poderiam ser otimizados caso fosse utilizada um número menor de<br />

<strong>portas</strong> <strong>lógicas</strong> (transformando o máximo possível de <strong>portas</strong> diferentes em uma porta<br />

complexa, por exemplo).

Gráfico 12 Combinações de entrada (v(2) e v(3)) e saída (v(5)) <strong>para</strong> a função C<br />

Gráfico 13 Medidas temporais do sinal de saída de C (na subida)<br />

t dlh =3,5ns e t R =2,5 ns

Gráfico 14 Medidas temporais do sinal de saída de C (na descida)<br />

t dhl=6,0 ns e t F=2,5ns<br />

Tabela com os resultados encontrados<br />

Tempo Vi Vf<br />

tdlh 3,5 ns 0 V 2 V<br />

tdhl 6,0 ns 4 V 2 V<br />

tr 2,5 ns 0,4 V 3,6 V<br />

tf 2,5 ns 3,6 V 0,4 V<br />

Estes tempos não poderiam ser otimizados, pois não existe a possibilidade de se<br />

utilizar uma porta complexa <strong>para</strong> essa função. A única modificação que poderia ser feita<br />

seria utilizar um NOR e dois inversores em vez de um NAND e um inversor, mas isso só<br />

aumentaria o tempo de subida do circuito (já que teria mais transistores P em série).<br />

Inversor com onda PWL<br />

O último circuito montado consistia em um inversor utilizando um gerador de ondas<br />

PWL de 0 a 10 V como entrada.

Gráfico 15 Inversor com fonte de tensão do tipo PWL. Saída em v(3)<br />

Descrição Spice – Inversor com onda PWL de entrada<br />

.include cmos7tm.mod<br />

vcc 1 0 10<br />

vin1 2 0 pwl(50m 0.0 150m 10.0 250m 0.0)<br />

**** Inversor ****<br />

.subckt inv in out vcc<br />

Mp1 vcc in out vcc modp<br />

Mn1 out in 0 0 modn<br />

.ends inv<br />

**** Circuito *****<br />

x1 2 3 1 inv<br />

.tran 1n 300m<br />

.print tran v(2) v(3)<br />

.end

A onda triangular utilizada pode ser vista como uma onda quadrada com um tempo<br />

de descida e subida considerável e tempo de propagação praticamente nulo. Assim, o<br />

inversor se comportou conforme o esperado, com o sinal de saída variando de 0 (lógico)<br />

<strong>para</strong> 1 (lógico) quando o sinal de entrada ia de 1 (lógico) <strong>para</strong> 0 (lógico) e vice-versa. O<br />

sinal é invertido pois quando a entrada está em 1 (lógico) o transistor P fica 'aberto' (não<br />

deixa passar corrente) e o transistor N fica 'fechado', ligando a saída à massa. Quando a<br />

entrada está em 0 (lógico) o transistor P fica 'fechado', ligando o Vcc à saída e o transistor<br />

N fica 'aberto'.<br />

Conclusões, Interesses, Dificuldades e Sugestões<br />

A maior dificuldade encontrada relaciona-se com a falta de tempo disponível <strong>para</strong> a<br />

resolução dos problemas. São muitas perguntas e questionamentos sobre tópicos que são<br />

exemplificados e necessitam ser entendidos no tempo entre o início e o fim da aula (muitos<br />

dos questionamentos são feitos sobre conteúdo abordados superficialmente na parte<br />

teórica). Além disso, há perguntas relacionadas a assuntos, como o meio-somador, que são<br />

vistos no mesmo dia na aula teórica. Nesses casos, o aluno não tem nem ao menos tempo<br />

<strong>para</strong> revisar a matéria e ter total compreensão do assunto.<br />

A atividade foi importante pela compreensão da montagem de uma porta através de<br />

transistores P e N e, a união das <strong>portas</strong> <strong>para</strong> montagem de <strong>circuitos</strong> mais complexos, como<br />

um meio-somador, que é amplamente utilizado em diversos <strong>circuitos</strong>.