Curs 3 - Bazele logice ale calculatoarelor - derivat

Curs 3 - Bazele logice ale calculatoarelor - derivat

Curs 3 - Bazele logice ale calculatoarelor - derivat

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

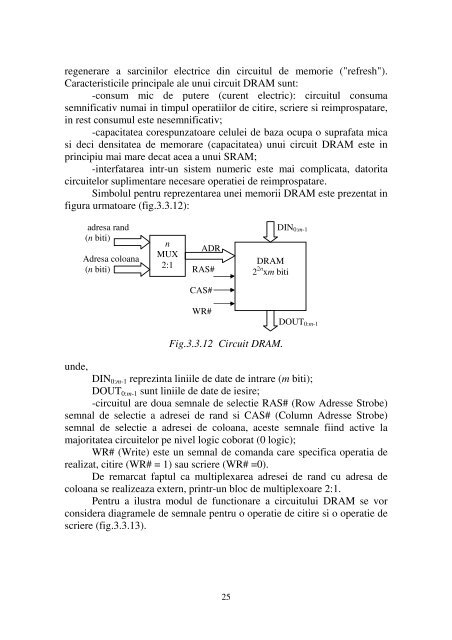

egenerare a sarcinilor electrice din circuitul de memorie ("refresh").<br />

Caracteristicile princip<strong>ale</strong> <strong>ale</strong> unui circuit DRAM sunt:<br />

-consum mic de putere (curent electric): circuitul consuma<br />

semnificativ numai in timpul operatiilor de citire, scriere si reimprospatare,<br />

in rest consumul este nesemnificativ;<br />

-capacitatea corespunzatoare celulei de baza ocupa o suprafata mica<br />

si deci densitatea de memorare (capacitatea) unui circuit DRAM este in<br />

principiu mai mare decat acea a unui SRAM;<br />

-interfatarea intr-un sistem numeric este mai complicata, datorita<br />

circuitelor suplimentare necesare operatiei de reimprospatare.<br />

Simbolul pentru reprezentarea unei memorii DRAM este prezentat in<br />

figura urmatoare (fig.3.3.12):<br />

unde,<br />

adresa rand DIN0:m-1<br />

(n biti)<br />

ADR<br />

Adresa coloana<br />

DRAM<br />

(n biti) RAS# 2 2n n<br />

MUX<br />

2:1<br />

xm biti<br />

CAS#<br />

WR#<br />

Fig.3.3.12 Circuit DRAM.<br />

25<br />

DOUT0:m-1<br />

DIN0:m-1 reprezinta liniile de date de intrare (m biti);<br />

DOUT0:m-1 sunt liniile de date de iesire;<br />

-circuitul are doua semn<strong>ale</strong> de selectie RAS# (Row Adresse Strobe)<br />

semnal de selectie a adresei de rand si CAS# (Column Adresse Strobe)<br />

semnal de selectie a adresei de coloana, aceste semn<strong>ale</strong> fiind active la<br />

majoritatea circuitelor pe nivel logic coborat (0 logic);<br />

WR# (Write) este un semnal de comanda care specifica operatia de<br />

realizat, citire (WR# = 1) sau scriere (WR# =0).<br />

De remarcat faptul ca multiplexarea adresei de rand cu adresa de<br />

coloana se realizeaza extern, printr-un bloc de multiplexoare 2:1.<br />

Pentru a ilustra modul de functionare a circuitului DRAM se vor<br />

considera diagramele de semn<strong>ale</strong> pentru o operatie de citire si o operatie de<br />

scriere (fig.3.3.13).

![Florian Moraru - Structuri de date [pdf] - Andrei](https://img.yumpu.com/16899682/1/184x260/florian-moraru-structuri-de-date-pdf-andrei.jpg?quality=85)

![Capitolul 2 - Elemente de mecanică cuantică [pdf] - Andrei](https://img.yumpu.com/16899601/1/190x245/capitolul-2-elemente-de-mecanica-cuantica-pdf-andrei.jpg?quality=85)

![Curs 2 - Gestiunea sistemului de fișiere [pdf] - Andrei](https://img.yumpu.com/16899511/1/190x143/curs-2-gestiunea-sistemului-de-fisiere-pdf-andrei.jpg?quality=85)

![Curs 5 - Performanțele circuitelor VLSI [pdf] - Andrei](https://img.yumpu.com/16899506/1/190x245/curs-5-performantele-circuitelor-vlsi-pdf-andrei.jpg?quality=85)