RF - 今日电子

RF - 今日电子

RF - 今日电子

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>RF</strong>/ 微波器件特刊<br />

36<br />

低噪声、集成的 VCO/PLL <strong>RF</strong> 合成器<br />

满足了无线基础设施的需求<br />

无线通信应用中的合成器<br />

在无线通信系统设计中,为混频器<br />

与调制解调器生成本地振荡器(LO)时钟<br />

的合成器是决定系统性能高低的关键组<br />

件。其会直接降低系统性能裕量,进而<br />

影响接收机的灵敏度、发送器的误差矢<br />

量幅度(EVM)以及信号频谱属性。采用<br />

外差(双转换)分集成接收机与直接转<br />

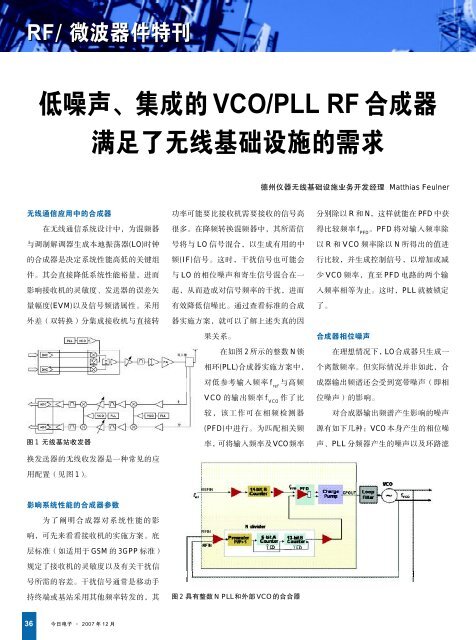

图 1 无线基站收发器<br />

换发送器的无线收发器是一种常见的应<br />

用配置(见图 1)。<br />

影响系统性能的合成器参数<br />

为了阐明合成器对系统性能的影<br />

响,可先来看看接收机的实施方案。底<br />

层标准(如适用于 GSM 的 3GPP 标准)<br />

规定了接收机的灵敏度以及有关干扰信<br />

号所需的容差。干扰信号通常是移动手<br />

持终端或基站采用其他频率转发的,其<br />

<strong>今日电子</strong> · 2007 年 12 月<br />

功率可能要比接收机需要接收的信号高<br />

很多。在降频转换混频器中,其所需信<br />

号将与 LO 信号混合,以生成有用的中<br />

频(IF)信号。这时,干扰信号也可能会<br />

与 LO 的相位噪声和寄生信号混合在一<br />

起,从而造成对信号频率的干扰,进而<br />

有效降低信噪比。通过查看标准的合成<br />

器实施方案,就可以了解上述失真的因<br />

果关系。<br />

德州仪器无线基础设施业务开发经理 Matthias Feulner<br />

在如图 2 所示的整数 N 锁<br />

相环(PLL)合成器实施方案中,<br />

对低参考输入频率 f ref 与高频<br />

VCO 的输出频率 f VCO 作了比<br />

较,该工作可在相频检测器<br />

(PFD)中进行。为匹配相关频<br />

率,可 将输入频率及VCO频率<br />

图 2 具有整数 N PLL和外部 VCO的合合器<br />

分别除以 R 和 N,这样就能在 PFD 中获<br />

得比较频率 f PFD 。PFD 将对输入频率除<br />

以 R 和 VCO 频率除以 N 所得出的值进<br />

行比较,并生成控制信号,以增加或减<br />

少 VCO 频率,直至 PFD 电路的两个输<br />

入频率相等为止。这时,PLL 就被锁定<br />

了。<br />

合成器相位噪声<br />

在理想情况下,LO合成器只生成一<br />

个离散频率。但实际情况并非如此,合<br />

成器输出频谱还会受到宽带噪声(即相<br />

位噪声)的影响。<br />

对合成器输出频谱产生影响的噪声<br />

源有如下几种:VCO 本身产生的相位噪<br />

声、PLL 分频器产生的噪声以及环路滤