使用Spartan-3A FPGA 實現低成本DDR2接口使用Spartan-3A ... - Xilinx

使用Spartan-3A FPGA 實現低成本DDR2接口使用Spartan-3A ... - Xilinx

使用Spartan-3A FPGA 實現低成本DDR2接口使用Spartan-3A ... - Xilinx

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

技 術 專 欄<br />

<strong>使用Spartan</strong>-<strong>3A</strong> <strong>FPGA</strong><br />

實現低成本DDR2接口<br />

<strong>Xilinx</strong> 提供存儲器接口完全解決方案,幫助您的產品更快上市<br />

Input_clock <strong>FPGA</strong>_Clock<br />

DCM<br />

User_data_valid<br />

User_output_data<br />

User_data_mask<br />

User_input_data<br />

User_address<br />

User_command<br />

User_burst_done<br />

User_cmd_ack<br />

User Interface<br />

LUT Delay<br />

Calibration<br />

Monitor<br />

Clocks all modules in fabric<br />

Write Datapath<br />

Controller<br />

FIFO<br />

Read<br />

Capture<br />

FIFO<br />

LUT<br />

Delay<br />

LUT<br />

Delay<br />

and Control<br />

DM<br />

Spartan-3 Generation<br />

<strong>FPGA</strong><br />

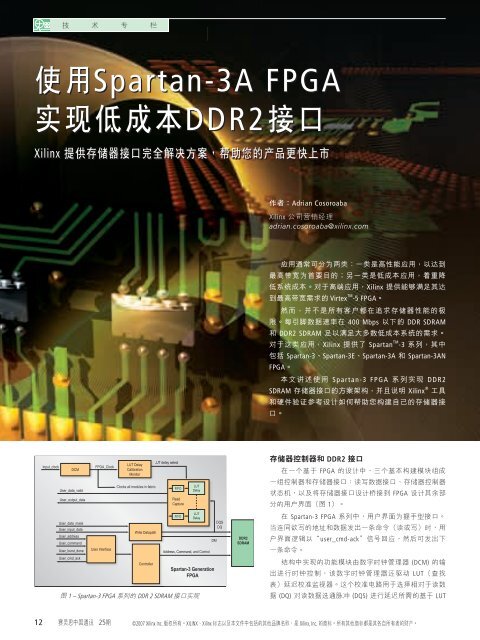

圖 1 – Spartan-3 <strong>FPGA</strong> 系列的 DDR 2 SDRAM 接口實現<br />

12 賽靈思中國通訊 25期<br />

DQS<br />

DQ<br />

DDR2<br />

SDRAM<br />

作者:Adrian Cosoroaba<br />

<strong>Xilinx</strong> 公司營銷經理<br />

adrian.cosoroaba@xilinx.com<br />

應用通常可分為兩類:一類是高性能應用,以達到<br />

最高帶寬為首要目的;另一類是低成本應用,重降<br />

低系統成本。對於高端應用,<strong>Xilinx</strong> 提供能夠滿足其達<br />

到最高帶寬需求的 Virtex TM -5 <strong>FPGA</strong>。<br />

然而,並不是所有客戶都在追求存儲器性能的極<br />

限。每引腳數據速率在 400 Mbps 以下的 DDR SDRAM<br />

和 DDR2 SDRAM 足以滿足大多數低成本系統的需求。<br />

對於這類應用,<strong>Xilinx</strong> 提供了 Spartan TM -3 系列,其中<br />

包括 Spartan-3、Spartan-3E、Spartan-<strong>3A</strong> 和 Spartan-<strong>3A</strong>N<br />

<strong>FPGA</strong>。<br />

本文講述使用 Spartan-3 <strong>FPGA</strong> 系列實現 DDR2<br />

SDRAM 存儲器接口的方案架構,並且說明 <strong>Xilinx</strong> ® 工具<br />

和硬件驗證參考設計如何幫助您構建自己的存儲器接<br />

口。<br />

存儲器控制器和 DDR2 接口<br />

在一個基於 <strong>FPGA</strong> 的設計中,三個基本構建模塊組成<br />

一組控制器和存儲器接口:讀寫數據接口、存儲器控制器<br />

狀態機,以及將存儲器接口設計橋接到 <strong>FPGA</strong> 設計其余部<br />

分的用戶界面(圖 1)。<br />

在 Spartan-3 <strong>FPGA</strong> 系列中,用戶界面為握手型接口。<br />

當連同欲寫的地址和數據發出一條命令(讀或寫)時,用<br />

戶界面邏輯以“user_cmd-ack”信號回應,然後可發出下<br />

一條命令。<br />

結構中實現的功能模塊由數字時鐘管理器 (DCM) 的輸<br />

出進行時鐘控制,該數字時鐘管理器還驅動 LUT(查找<br />

錶)延遲校准監視器。這個校准電路用於選擇相對於讀數<br />

據 (DQ) 對讀數據選通脈衝 (DQS) 進行延遲所需的基於 LUT<br />

©2007 <strong>Xilinx</strong> Inc. 版權所有。XILINX、<strong>Xilinx</strong> 標誌以及本文件中包括的其他品牌名稱,是 <strong>Xilinx</strong>, Inc. 的商標。所有其他商標都是其各自所有者的財產。

元件的數量,以便為在 <strong>FPGA</strong> 內部採集數<br />

據而正確對齊讀數據選通脈衝 (DQS)。<br />

在讀取事務過程中,DDR2 SDRAM 器件<br />

將 DQS 和相關數據發送到與 DQ 對齊邊沿<br />

的 <strong>FPGA</strong>。採集 DQ 是一項艱巨任務,因為<br />

非自由型 DQS 的每個沿上都有數據在變<br />

化。<br />

DQ 採集通過可配置邏輯塊 (CLB) 中的<br />

LUT 實現。DQ 採集的實現使用了一種基<br />

於 LUT 的 tap 延遲機制。DQS 時鐘信號經<br />

過延遲,以提供足夠的時序余量。DQ 採<br />

集是在基於 LUT 的雙端口 RAM 中實現的<br />

DQ<br />

FIFO 0<br />

FIFO_0_WE<br />

FIFO 1 User Data<br />

FIFO_1_WE<br />

IOB Delayed DQS CLB<br />

(圖 2)。LUT RAM 配置成一對 FIFO,每個<br />

數據位都輸入到上昇沿 (FIFO_0) 和下降沿<br />

(FIFO_1) 的 FIFO 中。這些厚度為 16 個入口<br />

的 FIFO 是異步的,具有獨立的讀寫端口。<br />

從 DQS 時鐘域到存儲器控制器時鐘域<br />

的 DQ 傳輸就是通過這些異步 FIFO 完成<br />

的。在存儲器控制器的時鐘域中,可以從<br />

FIFO_0 和 FIFO_1 同時讀出數據。FIFO 的讀<br />

指針是在 <strong>FPGA</strong> 的內部時鐘域中生成的。<br />

寫使能信號(FIFO_0 WE 和 FIFO1_WE)的<br />

生成是通過 DQS 和一個外部環回或歸一化<br />

信號完成的。<br />

外部歸一化信號作為輸出送至輸入/輸<br />

出模塊 (IOB),然後再作為輸入送至輸入緩<br />

衝器。這種技術可補償 <strong>FPGA</strong> 與存儲器器<br />

件之間的 IOB、器件和跡線延遲。<br />

寫數據接口生成並控制寫數據命令和<br />

時序。寫數據接口使用 IOB 觸發器和 DCM<br />

的 90 度、180 度和 270 度輸出,發送一個<br />

按照 DDR 和 DDR2 SDRAM 的時序要求與命<br />

令位和數據位正確對齊的 DQS。<br />

此設計的其他方面包括整體控制器狀<br />

態機的邏輯生成和用戶界面。為便於設計<br />

人員使用整個解決方案,<strong>Xilinx</strong> 開發了存儲<br />

器接口生成器 (MIG) 工具。<br />

控制器的設計<br />

以及與 MIG 軟件工具的集成<br />

為了使您的設計完善,集成包括存儲<br />

Spartan-3<br />

Generation<br />

FIFO_0_WE<br />

FIFO_1_WE<br />

器控制器狀態機在內的所有構建模塊至關<br />

重要。控制器狀態機因存儲器架構和系<br />

統參數不同而異。狀態機代碼也可以很複<br />

雜,它可能是多個變量的函數,例如:<br />

• 架構(DDR、DDR2)<br />

• 組數(存儲器器件的外部或內部)<br />

• 數據總線寬度<br />

• 存儲器器件的寬度和厚度<br />

• 組和行存取算法<br />

最後,數據與選通脈衝比 (DQ/DQS) 這<br />

類參數會進一步加大設計的複雜性。控<br />

CLK<br />

Data/DQS<br />

Address<br />

Normalization<br />

Signal<br />

DDR2<br />

SDRAM<br />

制 器 狀 態 機<br />

必 須 按 正 確<br />

順 序 發 出 命<br />

令 , 同 時 還<br />

要 考 慮 存 儲<br />

器 器 件 的 時<br />

序要求。<br />

使用 MIG<br />

軟 件 工 具 可<br />

生 成 完 整 的<br />

設計。該工具作為參考設計和知識產權作<br />

品中的 ISE TM 軟件 CORE Generator TM 套件的<br />

一部分,可從 <strong>Xilinx</strong> 免費獲取。MIG 的設計<br />

流程與傳統 <strong>FPGA</strong> 的設計流程非常相似。<br />

對設計人員的好處是,有了這個軟件工<br />

具,就不必再為物理層接口或存儲器控制<br />

器從頭生成 RTL 代碼。<br />

要設置系統和存儲器參數,可使用 MIG<br />

的圖形用戶界面 (GUI)。例如,選定 <strong>FPGA</strong><br />

器件、封裝方式和速度級別之後,可以選<br />

擇存儲器架構,甚至還可以挑選實際的<br />

<strong>Xilinx</strong> <strong>FPGA</strong> Spartan-3 <strong>FPGA</strong> Spartan-3E <strong>FPGA</strong> Spartan-<strong>3A</strong> <strong>FPGA</strong><br />

開發板 SL361 入門套件 3E 入門套件 <strong>3A</strong><br />

支持的存儲器接口 DDR DDR DDR2<br />

存儲器器件或 DIMM(雙列直插存儲器模<br />

塊)。同是這一個 GUI,還可用來選擇總<br />

線寬度和時鐘頻率。另外一些選項可提供<br />

對 CAS(列訪問 DQS)延遲、突發長度和<br />

引腳分配的控制。<br />

用不了一分鐘,MIG 工具即可生成 RTL<br />

和 UCF 文件(分別是 HDL 代碼和約束文<br />

件)。這些文件是用一個經過硬件驗證的<br />

參考設計庫生成的,所用的參考設計根據<br />

您的輸入進行了修改。輸出文件按模塊分<br />

類,適用於此設計的不同構建模塊,如用<br />

戶界面、物理層和控制器狀態機。<br />

錶 1 – 存儲器接口的低成本開發板<br />

技 術 專 欄<br />

您還享有完全的靈活性,可進一步修<br />

改 RTL 代碼。與提供“黑匣子”實現方法<br />

的其他解決方案不同,此設計中的代碼沒<br />

有加密,從而提供了對設計進行修改和進<br />

一步定制的完全靈活性。修改任何可選代<br />

碼之後,都可再次進行仿真,以驗證整體<br />

設計的功能。<br />

MIG 工具還可生成具有存儲器校驗功<br />

能的可綜合測試平台。該測試平台是一個<br />

設計示例,用於 <strong>Xilinx</strong> 參考設計的功能仿<br />

真和硬件驗證,它可以向存儲器控制器發<br />

出一系列寫命令和讀回命令。您還可將其<br />

用作模板,生成自己的定制測試平台。<br />

設計的最後階段是導入 ISE 項目中的<br />

MIG 文件,將其與 <strong>FPGA</strong> 設計的其余文件合<br />

併(然後進行綜合、佈局和布線),必要<br />

時還會運行其他時序仿真,並進行硬件驗<br />

證。MIG 軟件工具生成一個批處理文件,<br />

其中有相應的綜合、映射、佈局和布線選<br />

項,以幫助您優化生成最終的位文件。<br />

硬件驗證和開發板<br />

參考設計的硬件驗證是確保解決方案<br />

嚴密可靠的最終重要步驟。<br />

<strong>Xilinx</strong> 對在硬件中實現 Spartan-<strong>3A</strong> <strong>FPGA</strong><br />

的 DDR2 SDRAM 存儲器接口進行了全面驗<br />

證。我們用低成本的 Spartan-<strong>3A</strong> 入門套件<br />

板實現了 DDR2 SDRAM 設計,在設計中使<br />

用了板上16 位寬的 DDR2 SDRAM 存儲器器<br />

件和 XC3S700A-FG484 <strong>FPGA</strong>。此參考設計僅<br />

使用了 Spartan-<strong>3A</strong> 器件可用資源的一小部<br />

分:IOB 的 13%、邏輯 Slice 的 9%、BUFG<br />

MUX 的 16% 和八個 DCM 之一。本實現方<br />

法為其他功能留下了大量資源。<br />

<strong>Xilinx</strong> 驗證了各種 Spartan-3 <strong>FPGA</strong> 系<br />

列的存儲器接口設計。錶 1 所示為各種<br />

Spartan-3 <strong>FPGA</strong> 系列開發板的硬件驗證存儲<br />

器接口。<br />

結論<br />

使用低成本 Spartan-3 <strong>FPGA</strong> 系列、存儲<br />

器接口生成器 (MIG) 工具和 <strong>Xilinx</strong> 開發板,<br />

可加快存儲器接口和控制器的設計。<br />

有關存儲器接口解決方案的進一步信息<br />

和詳情,請訪問 www.xilinx.com/cn/memory。<br />

2007年夏季刊 13