Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

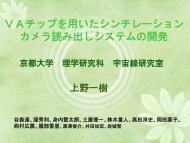

岩 城 智<br />

谷 森 達 , 窪 秀 利 , 身 内 賢 太 朗 , 水 本 哲 矢 ,Parker Joseph,<br />

澤 野 達 哉 , 中 村 輝 石 , 松 岡 佳 大 , 古 村 翔 太 郎 , 佐 藤 快 ,<br />

高 田 淳 史 A<br />

, 岸 本 祐 二 B<br />

, 上 野 一 樹 C<br />

, 株 木 重 人 D<br />

, 黒 澤 俊 介 E<br />

,<br />

田 中 真 伸 F<br />

, 池 野 正 弘 F<br />

, 内 田 智 久 F<br />

,<br />

他 オープンソースコンソーシアム(Open-It)<br />

京 大 理 , 京 大 生 存 圏 研 A<br />

,KEK 放 射 線 科 学 センターB, 理 研 C<br />

,<br />

東 海 大 医 D<br />

, 東 北 大 金 属 研 E<br />

,KEK 素 核 研<br />

F<br />

2011 年 9 月 18 日<br />

日 本 物 理 学 会 2011 年 秋 季 大 会<br />

@ 弘 前 大 学 文 京 町 キャンパス

• Introduction<br />

o Electron Tracking Compton Camera (ETCC)<br />

o 気 球 実 験 SMILE<br />

• CMOS-ASIC<br />

o FE2009bal<br />

o テストパルスによる 性 能 評 価<br />

o μ-PICとの 接 続 試 験<br />

• 新 読 み 出 しボード<br />

• Summary

Sub MeV~ MeV γ 線 による<br />

イメージング<br />

•γ 線 天 文 学 ( 気 球 実 験 SMILE)<br />

• 核 医 療<br />

• micro-TPC<br />

・μ-PICを 用 いた<br />

Time Projection Chamber<br />

・ 反 跳 電 子 の 飛 跡 とエネルギーを 測 定<br />

• シンチレーションカメラ<br />

・Pixel Scintillator Array<br />

+Multi Anode PMT<br />

・ 散 乱 γ 線 の 吸 収 位 置 とエネルギーを 測 定<br />

1event 毎 にコンプトン 散 乱 を 再 構 成<br />

エネルギーと 到 来 方 向 を 一 意 に 決 定

Sub-MeV gamma-ray Imaging<br />

Loaded-on-balloon Experiment<br />

SMILE-Ⅰ 実 験 (2006 年 9 月 1 日 )<br />

• 10×10×15cm 3 ETCC(512ch 読 み 出 し)<br />

• @ 三 陸 35km 4h<br />

• 動 作 実 証 及 び 宇 宙 拡 散 γ・ 大 気 γ 線 測 定<br />

• m-PIC 読 み 出 しにはATLAS TGC ASDを 使 用<br />

ASD(Bipolarプロセス) : 59mW/ch<br />

SMILE-Ⅱ 実 験<br />

• (30 cm) 3 ETCC (1500ch 読 み 出 し)<br />

• @ 大 樹 町 ( 北 海 道 ) 35km 2-3h<br />

長 期 運 用 システムの 試 験 2012<br />

• @キルナ(スウェーデン) 40km ~2w<br />

明 るい 天 体 REP-burstの 観 測 2013~<br />

ATLAS TGC ASD 64ch board<br />

4ch/chip<br />

気 球 では 電 力 、 重 量 及 びスペースは 限 られているため、<br />

省 電 力 &コンパクトな 読 み 出 しシステムが 必 要

• 現 在 μ-PICからの 信 号 は、SONY 製 の<br />

ASD (amplifier-shaper-discriminator) chipで 読 み 出 し<br />

⇒ 生 産 中 止<br />

• 省 電 力 化<br />

ASD : 60mW/ch⇒90W for (30cm) 2 m-PIC<br />

SMILEⅡでは30W 以 下 に 抑 えたい<br />

⇒20mW/ch 以 下 を 目 標<br />

• 回 路 の 高 集 積 化<br />

現 在 ASD chipがかさばっていて、<br />

30cm 角 μ-PICになると 扱 いづらい<br />

ASD:4ch/chip ⇒ 16ch/chipへ<br />

そこで、 低 消 費 電 力 のCMOS ASIC chip を<br />

KEK 回 路 室 と 共 同 開 発 してきた

• MIPトラックを 取 得 したい<br />

⇒ノイズレベル 6000e- (Cd = 100pF)<br />

• 電 子 のエネルギー 取 得<br />

⇒アナログ 出 力 :ダイナミックレンジ±1pC<br />

• 100MHzでサンプリング<br />

⇒タイムウォーク

CAL<br />

Input<br />

ch0<br />

Preamp<br />

PZC<br />

Shaper<br />

Sum<br />

amp<br />

ABuf<br />

AOUT<br />

analog ch0<br />

Amp<br />

×30<br />

Comp<br />

arator<br />

DOUT1<br />

DAC<br />

digital ch0<br />

ch15<br />

Vth<br />

CAL/DAC<br />

Control<br />

analog ch15<br />

digital ch15<br />

DOUT16<br />

構 成<br />

- 電 荷 有 感 型 前 置 増 幅 器 / 波 形 整 形 回 路 /コンパレータ<br />

主 な 仕 様<br />

- 製 造 プロセス:TSMC0.5μmCMOS<br />

- 電 源 :±2.5V<br />

-チャンネル 数 :16ch<br />

- 出 力 :デジタル CMOS2.5V,アナログサム

ASD<br />

FE2009bal<br />

Ch 数 4 16<br />

ピーキングタイム 20ns 30ns<br />

ダイナミックレンジ -1.2~2.0pC ±1pC<br />

ノイズ(Cd=100pF) ~3000e ~6000e<br />

クロストーク 0.5% 以 下 ≪0.5%<br />

( 全 ch)<br />

タイムウォーク<br />

Vth ばらつき 補 償<br />

~6.5ns<br />

(20fC-1pC)<br />

4mm<br />

バイアス 系<br />

電 源 (±2.5V)<br />

パッケージ :<br />

LCP100P<br />

電 源<br />

+2.5V : 47mA<br />

-2.5V : 66mA<br />

⇒17.5mW/ch<br />

(シミュレーション:15mW/ch)<br />

シミュレーションよりは 大 きいが<br />

要 請 値 (20mW 以 下 )はクリア<br />

アナログSum 出 力 、テスト 入 力<br />

DAC 補 正 用 回 路 など<br />

16mm<br />

アナログ 入 力 (16ch)<br />

デジタル 出 力 (16ch)

Qin=0.5pC<br />

Input<br />

Analog Sum<br />

400mV<br />

• 入 力 -1pC~1pC<br />

• Gain ~800mV/pC<br />

• Peaking time ~30ns<br />

シミュレーションとほぼ 一 致

• 64chボード 作 成<br />

(デジタルはLVDSに 変 換 して 出 力 )<br />

FE2009bal 4つで64chのボードを 作 成<br />

Anode、Cathodeとも64chで 読 み 出 し<br />

⇒2.5cm×2.5cmの 有 感 領 域<br />

• データ 取 得 条 件<br />

o 使 用 ガス Ar 90% C2H6 10% 1atm<br />

o Drift Top -4.5kV (0.25kV/cm)<br />

o ⊿GEM : 400V(P140-φ70-100t LCP)<br />

o Anode +420V<br />

ASDでの 測 定 ではGain~40000

線 源 : 109 Cd<br />

400mV<br />

Analog Sum<br />

22keV<br />

Res.=20%(FWHM)<br />

Digital (LVDS)<br />

m-PICからの 信 号 を 確 認

プラシン<br />

z<br />

ガス<br />

m-PIC<br />

10cm<br />

有<br />

感<br />

領<br />

域<br />

プラシン<br />

宇 宙 線 ミューオンの 飛 跡 を 確 認 ,MIPの 取 得 に 成 功<br />

FE2009balの 性 能 はOK<br />

このチップを 用 いた 読 み 出 しシステムを 開 発 する

プロトタイプ(30cm) 3 ETCC<br />

micro-TPC<br />

1m<br />

エンコーダー<br />

ASD<br />

ASD<br />

+VME<br />

(Memory board,FADC,etc)<br />

+NIM(Logic)<br />

• 読 み 出 し 回 路 重 量 : >60kg( 治 具 、ケーブル 等 含 む)<br />

• 気 球 のVesselのサイズ 制 限 (φ90cm)<br />

⇒より 軽 量 &コンパクトな 読 み 出 しボードの 開 発

118mm<br />

220mm<br />

FPGA<br />

8 FE2009bal chips<br />

60W for a (30cm) 2 m-PIC<br />

• 8 FE2009bal chips (128ch).<br />

• 32ch sum analog signal output.<br />

• 10bit 100MHz ADC ×4.<br />

• FPGA : Xilinx Spartan6<br />

(XC6SLX100-2FGG676C) .<br />

• Parallel LVDS output<br />

50MHz, 32bit (1.6Gbps).<br />

• ±2.5V and +3.3V are required.<br />

• Power Consumption : ~5W/board.

(30cm) 2<br />

m-PIC<br />

FE2009bal<br />

(16ch)<br />

×8<br />

Analog<br />

4ch<br />

ADC<br />

Digital<br />

128ch<br />

FPGA<br />

LVDS<br />

32bit×<br />

50MHz<br />

Hit position,<br />

Clock<br />

ADC data<br />

VME<br />

Memory<br />

board<br />

×12 boards<br />

DAC control<br />

Trigger<br />

I/O

10cm<br />

データ 取 得 条 件<br />

o ガス : Ar 90% C2H6 10% 1atm<br />

o Drift Top -4.5kV (0.25kV/cm)<br />

o ⊿GEM : 350V(P140-φ70-50t LCP)<br />

o Anode +450V<br />

ASDでの 測 定 ではGain~50000

109<br />

Cd<br />

200ns<br />

線 源 : 109 Cd 400mV<br />

Analog Sum<br />

Digital

400ns<br />

• FPGAのバグのため()50MHzでサンプリング<br />

• FADCで4ch 分 のアナログ 波 形 が 取 れていることを 確 認<br />

• Hit 信 号 によるトラッキングは 今 後

• m-PICを 用 いたETCCによる 気 球 実 験 SMILEⅡにむけ、<br />

省 電 力 なCMOS ASIC chip FE2009balを 開 発<br />

• FE2009balを 用 いたコンパクトな 読 み 出 しボードを 開 発<br />

消 費 電 力 : 160W ⇒ 60W (30cm) 2 m-PIC<br />

重 量 : 60kg ⇒~20kg<br />

• 新 読 み 出 しボードでのMIPトラックの 取 得<br />

• コンプトンイメージングテスト<br />

• FPGAロジックを 含 めたDAQの 最 適 化<br />

• Flight Model への 組 み 込 み

μ-PIC(というかμ-TPC)の 信 号 を 読 み 出 すのに 必 要 な 仕 様 をおさらい<br />

• ダイナミックレンジについて<br />

1ストリップに 最 大 の 電 荷 が 入 ってくるのは<br />

5.9keV / 26eV * 30000 倍 * e = 1.1pC<br />

Anode、Cathode 両 方 よむので、<br />

ダイナミックレンジは±1pC 以 上<br />

• ノイズレベルについて<br />

最 小 の 電 荷 は Ar ガス 中 をMIPが 走 った 時 。<br />

1ストリップに 落 す 一 次 電 荷 量 は<br />

1.37MeV/(g*cm -2 ) * 1.66g/cm 3 * 400um<br />

= 90eV<br />

⇒90eV / 26eV * 30000 倍 * e = 16fC<br />

統 計 揺 らぎを 考 えると<br />

1e * 30000 = 5fCからとりたい。<br />

⇒ノイズレベル~3fC 以 下 が 必 要<br />

1.37MeV

• ドリフト 速 度 最 速 のCF4で<br />

~10cm/usec<br />

• クロック100MHz(10ns)で<br />

サンプリング<br />

⇒1clkずれるとz 方 向 に<br />

~1mmのずれ<br />

• 最 小 の 電 荷 が5fCなので、<br />

5fC 以 上 の 領 域 で<br />

タイムウォーク10ns 以 下<br />

が 要 求 値<br />

(ASDのタイムウォーク:<br />

20fCからで7ns、Vth=5fC)

• アナログ 出 力<br />

各 chのアナログをSumして 出 力<br />

足 し 合 わせたときにSaturateしないように<br />

適 当 に 減 衰 させる<br />

• デジタル 出 力<br />

これまでLVDS 出 力 だった。<br />

LVDSドライバが 電 力 食 い<br />

⇒CMOS2.5V 出 力 に

• 消 費 電 力 に 関 して<br />

• SMILEⅡにおけるm-TPC 全 読 み 出 しch 数 は<br />

1536ch((30cm) 2 m-PIC)<br />

• これを60W 程 度 で 読 み 出 す(Digital 込 )<br />

• Digitalで 半 分 くらい<br />

⇒Analog 系 は~30W<br />

⇒ 余 裕 をもって18mW/chを 目 標 とする

項 目 目 標 備 考<br />

Ch 数<br />

16ch/chip<br />

ダイナミックレンジ ±1.0pC 以 上 下 方 修 正<br />

ノイズレベル

10cm<br />

構 成<br />

- 電 荷 有 感 型 前 置 増 幅 器 / 波 形 整 形 回 路 /コンパレータ<br />

主 な 仕 様<br />

- 製 造 プロセス:0.5μmCMOS<br />

- 電 源 :±2.5V<br />

-チャンネル 数 :8ch ⇒ もっと 集 積 度 を 上 げたい<br />

- 出 力 :デジタルLVDS,アナログサム<br />

55<br />

FeによるX 線 イメージ<br />

- 消 費 電 力 :30mW/ch ⇒ さらに 消 費 電 力 を 抑 える 必 要 性<br />

8ch/chip<br />

20cm

入 力<br />

preamp<br />

PZ<br />

Shaper<br />

Sum amp<br />

デジタル<br />

-5mV<br />

3.5mV<br />

-11mV<br />

10mV<br />

2mV<br />

0 1 2[us]

-3 -2 -1 0 1 2 3 [V]<br />

-3 -2 -1 0 1 2 3 [V]<br />

-600 -400 -200 0 200 400 600 [mV]<br />

PZ 出 力<br />

Shaper 出 力<br />

Sum amp 出 力<br />

-2 -1 0 1 2<br />

[pC]<br />

-2 -1 0 1 2<br />

[pC]<br />

-2 -1 0 1 2<br />

[pC]

タイムウォーク(ns)<br />

10fC<br />

最 大 6ns<br />

(10fC-300fC)<br />

入 力 電 荷 (fC)<br />

10fC~1pCまででタイムウォークは~6ns<br />

シミュレーション(7ns)と 同 程 度<br />

30

After calibration<br />

: 20mV(0.4fC)<br />

Before calibration<br />

: 300mV(6fC)

2011/1/17

FPGA : Vertex2P XC2VP30 ×8<br />

SDRAM : オプションで512MBまで<br />

Memory Board とのI/F : DX20BM-68S<br />

2011/1/24 追 加

Analog 4ch<br />

ADC<br />

Clock<br />

Data exist<br />

FIFO<br />

Trigger<br />

Digital 128ch<br />

CMOS 2.5<br />

FIFO<br />

Edge<br />

検 出<br />

Data<br />

format<br />

Clear<br />

Transfer<br />

To Memory Board<br />

FPGA<br />

DAC control 3ch<br />

Vth(-1~1V)<br />

DAC<br />

DAC control

シールド<br />

m-PIC<br />

シールド<br />

CR- 基 板<br />

シールド<br />

いわきちっぷ128ch + エンコーダ<br />

いわきちっぷ128ch + エンコーダ<br />

To MB ×2