I.6 LDPC coder/decoder FPGA IP Core - IPrium

I.6 LDPC coder/decoder FPGA IP Core - IPrium

I.6 LDPC coder/decoder FPGA IP Core - IPrium

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>I.6</strong> <strong>LDPC</strong> En<strong>coder</strong>/De<strong>coder</strong> <strong>IP</strong> <strong>Core</strong><br />

Release<br />

Information<br />

Name<br />

Version 1.0<br />

I6-<strong>LDPC</strong>-CODEC<br />

Build date 2013.04<br />

Ordering code<br />

ip-i6-ldpc-codec<br />

Features<br />

The <strong>IP</strong> core implements the <strong>LDPC</strong> (32640, 30592) forward error<br />

correction algorithm for optical lines and is fully compatible with<br />

the recommendation:<br />

1. ITU-T G.975.1 (super-FEC for 2.5G, 10G and 40G optical<br />

networks).<br />

Deliverables<br />

<strong>IP</strong> <strong>Core</strong> Structure<br />

<strong>I.6</strong> <strong>LDPC</strong> En<strong>coder</strong>/De<strong>coder</strong> <strong>IP</strong> <strong>Core</strong> includes:<br />

• VQM/NGC/EDIF netlists for Altera Quartus II, Xilinx ISE, Lattice<br />

Diamond or Microsemi (Actel) Libero SoC;<br />

• <strong>IP</strong> <strong>Core</strong> testbench scripts;<br />

• Design examples for Altera, Xilinx, Lattice, and Microsemi<br />

(Actel) evaluation boards.<br />

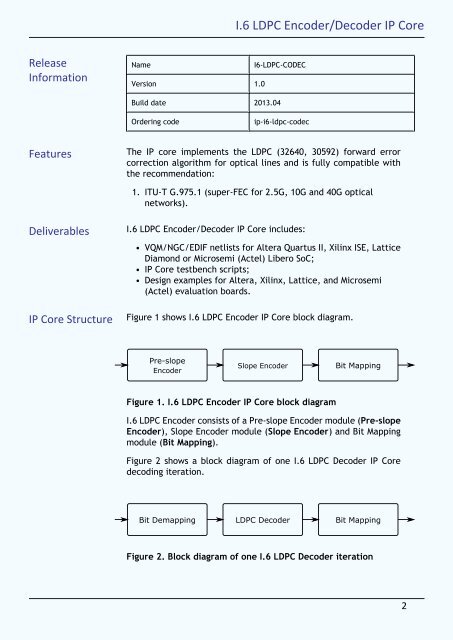

Figure 1 shows <strong>I.6</strong> <strong>LDPC</strong> En<strong>coder</strong> <strong>IP</strong> <strong>Core</strong> block diagram.<br />

Pre-slope<br />

En<strong>coder</strong><br />

Slope En<strong>coder</strong><br />

Bit Mapping<br />

Figure 1. <strong>I.6</strong> <strong>LDPC</strong> En<strong>coder</strong> <strong>IP</strong> <strong>Core</strong> block diagram<br />

<strong>I.6</strong> <strong>LDPC</strong> En<strong>coder</strong> consists of a Pre-slope En<strong>coder</strong> module (Pre-slope<br />

En<strong>coder</strong>), Slope En<strong>coder</strong> module (Slope En<strong>coder</strong>) and Bit Mapping<br />

module (Bit Mapping).<br />

Figure 2 shows a block diagram of one <strong>I.6</strong> <strong>LDPC</strong> De<strong>coder</strong> <strong>IP</strong> <strong>Core</strong><br />

decoding iteration.<br />

Bit Demapping <strong>LDPC</strong> De<strong>coder</strong> Bit Mapping<br />

Figure 2. Block diagram of one <strong>I.6</strong> <strong>LDPC</strong> De<strong>coder</strong> iteration<br />

2