Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

A<br />

B<br />

C<br />

37,42<br />

1<br />

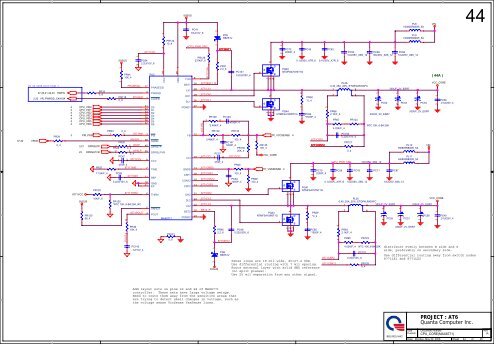

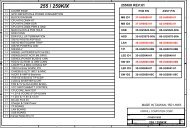

Do we need pull-high ?<br />

37,40,41,42,43 HWPG<br />

2,23 VR_PWRGD_CK410#<br />

PR28<br />

VRON<br />

0_4<br />

4<br />

4<br />

4<br />

4<br />

4<br />

4<br />

4<br />

3<br />

CPU_VID0<br />

CPU_VID1<br />

CPU_VID2<br />

CPU_VID3<br />

CPU_VID4<br />

CPU_VID5<br />

CPU_VID6<br />

3,21<br />

23<br />

8771VCC<br />

PM_PSI#<br />

5VSUS<br />

DPRSLP#<br />

DPRSLPVR<br />

PR120<br />

56_4<br />

PR32<br />

0_6<br />

PR37<br />

71.5K/F_4<br />

PR122<br />

10K/F_6<br />

5VSUS<br />

1<br />

2<br />

PR118<br />

0_6<br />

PR33 0_4<br />

1 2<br />

470P_4<br />

8771TIME<br />

PC65<br />

0.22U/10V_6<br />

PR44<br />

10K_4<br />

POUT<br />

PHASEGD<br />

#CLKEN<br />

8771PSI<br />

8771REF<br />

8771THRM<br />

1 2<br />

1<br />

2<br />

PR125<br />

*NTC 10K_6-B4.25K_NC<br />

8771POUT<br />

PR36<br />

10K_4<br />

2<br />

8771VCC<br />

PC64<br />

2.2U/10V_6<br />

17<br />

PU2<br />

31<br />

D0<br />

32<br />

D1<br />

33<br />

D2<br />

34<br />

D3<br />

35<br />

D4<br />

36<br />

D5<br />

37<br />

D6<br />

VCC 19<br />

#SHDN<br />

PR30<br />

38<br />

SHDN<br />

1 2 DSTP<br />

PR29 0_4<br />

40<br />

DPRSTP<br />

2 1 DPSLP<br />

0_4<br />

39<br />

DPRSLPVR<br />

PC47<br />

1 2 8771CCV 9<br />

CCV<br />

2<br />

1<br />

3<br />

7<br />

11<br />

6<br />

5<br />

PHASEGD<br />

PWRGD<br />

CLKEN<br />

PSI<br />

TIME<br />

REF<br />

18<br />

GND<br />

41<br />

EP<br />

4<br />

THRM<br />

VRHOT<br />

POUT<br />

1<br />

2<br />

PR132<br />

10_8<br />

MAX8771<br />

PR121<br />

0_6<br />

VDD 25<br />

5VSUS<br />

PC41<br />

10U/10V_8<br />

+CPU_PWR_SRC<br />

TON 8<br />

BST1<br />

LX1<br />

DH1<br />

DL1<br />

PGND1<br />

CCI<br />

PR126<br />

237K/F_6<br />

10<br />

GNDS 13<br />

CSP1<br />

CSN12<br />

CSP2<br />

DH2<br />

DL2<br />

BST2<br />

PGND2<br />

30<br />

28<br />

29<br />

26<br />

27<br />

FB 12<br />

LX2<br />

16<br />

15<br />

14<br />

21<br />

24<br />

22<br />

20<br />

23<br />

8771TON<br />

8771BST1_R<br />

8771LX1<br />

8771DH1<br />

8771DL1<br />

8771FB<br />

8771CCI<br />

8771GNDS<br />

8771CSP1<br />

8771CSN12<br />

8771CSP2<br />

8771DH2<br />

8771DL2<br />

8771LX2<br />

BST2_R<br />

2<br />

1<br />

8771BST1<br />

PR31<br />

2.2_6<br />

PR129 PC149<br />

1 2<br />

*4700P_4<br />

*3.48K/F_4<br />

PR130<br />

3.48K/F_4<br />

PC57<br />

1 2<br />

470P_4<br />

PR46<br />

2.2_6<br />

PD5<br />

RB751V<br />

8771BST2<br />

PR133<br />

100_4<br />

PC147<br />

1000P_4<br />

PR136<br />

20K_4<br />

8771CCI2<br />

PR45<br />

100_4<br />

3<br />

PC141<br />

0.22U/25V_6<br />

PC63<br />

1000P_4<br />

PC49<br />

0.22U/25V_6<br />

PR49<br />

100_4<br />

4<br />

4<br />

G<br />

G<br />

PR135<br />

100_4<br />

5<br />

5<br />

D<br />

S<br />

D<br />

VCC_CORE<br />

TP_VCCSENSE 4<br />

TP_VSSSENSE 4<br />

PQ43<br />

NTMFS4108NT1G<br />

1<br />

2<br />

3<br />

S<br />

PQ44<br />

NTMFS4108NT1G<br />

1<br />

2<br />

3<br />

1<br />

2<br />

4<br />

4<br />

PC72<br />

2200P_4<br />

PQ40<br />

NTMFS4707NT1G<br />

G<br />

G<br />

5<br />

5<br />

D<br />

S<br />

1<br />

2<br />

3<br />

D<br />

S<br />

1<br />

2<br />

3<br />

1 2<br />

PC45<br />

0.1U/50V_X7R_6<br />

PR62<br />

*0_4<br />

PC86<br />

*1500P_4<br />

8771CSP1<br />

8771CSN12<br />

1<br />

2<br />

PC85<br />

*1500P_4<br />

PC42<br />

0.1U/50V_X7R_6<br />

1 2<br />

PC70<br />

2200P_4<br />

PQ41<br />

NTMFS4707NT1G<br />

1 2<br />

PR59<br />

*0_4<br />

PR67<br />

4.02K/F_4<br />

4<br />

PL26<br />

0.45_25A_20%_ETQP4LR45XFC<br />

1 2<br />

3 4<br />

PR66<br />

2.1K/F_4<br />

+CPU_PWR_SRC<br />

PC58<br />

0.1U/50V_X7R_6<br />

1 2<br />

PC50<br />

10U/25V_X6S_12<br />

PC150<br />

0.22U/10V_6<br />

PR127<br />

0_4<br />

PC87<br />

10U/25V_X6S_12<br />

PL25<br />

0.45_25A_20%_ETQP4LR45XFC<br />

1 2 330UF_2V_ESR7<br />

3 4<br />

PR64<br />

2.1K/F_4<br />

PR65<br />

PR124<br />

PC78<br />

10U/25V_X6S_12<br />

PC68<br />

10U/25V_X6S_12<br />

1<br />

2<br />

PC52<br />

330UF_2V_ESR7<br />

NTC 10K_6-B4.25K<br />

10U/25V_X6S_12<br />

PR123<br />

PC71<br />

1<br />

2<br />

330UF_2V_ESR7<br />

PC55<br />

1<br />

2<br />

1<br />

2<br />

PL8<br />

HI0805R800R_5A<br />

PL9<br />

HI0805R800R_5A<br />

PC62<br />

10U/25V_X6S_12<br />

PC53<br />

PL10<br />

HI0805R800R_5A<br />

PL11<br />

HI0805R800R_5A<br />

PC51<br />

330UF_2V_ESR7<br />

1<br />

2<br />

VIN<br />

330UF_2V_ESR7<br />

1<br />

2<br />

PC54<br />

330UF_2V_ESR7<br />

PC56<br />

VIN<br />

5<br />

( 44A )<br />

VCC_CORE<br />

1<br />

2<br />

VCC_CORE<br />

1<br />

2<br />

PC39<br />

.01U/25V_4<br />

PC40<br />

.01U/25V_4<br />

44<br />

A<br />

B<br />

C<br />

PC142<br />

.1U/10V_4<br />

2 1<br />

5VSUS<br />

PD6<br />

RB751V<br />

Sense lines are 18 mil wide, Z0=27.4 Ohm.<br />

Use differential routing with 7 mil spacing.<br />

Route external layer with solid GND reference<br />

(no split planes).<br />

Use 25 mil separation from any other signal.<br />

8771CSP2<br />

8771CSN12<br />

4.02K/F_4 NTC 10K_6-B4.25K<br />

PC151<br />

0.22U/10V_6<br />

PR128<br />

0_4<br />

distribute evenly between N side and S<br />

side, preferably on secondary side.<br />

Use differential routing away from switch nodes<br />

8771LX1 and 8771LX2<br />

D<br />

Add layout note on pins 22 and 28 of MAX8771<br />

controller. These nets have large voltage swings.<br />

Need to route them away from the sensitive areas that<br />

are trying to detect small changes in voltage, such as<br />

the voltage sense VccSense VssSense lines.<br />

D<br />

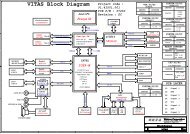

PROJECT : <strong>AT6</strong><br />

Quanta Computer Inc.<br />

1<br />

2<br />

3<br />

4<br />

NB5/RD1/HW2<br />

Size Document Number Rev<br />

Custom CPU_CORE(MAX8771)<br />

1A<br />

Date: Monday, May 22, 2006 Sheet 44 of 45<br />

5