NAU7802 24-bit ADC - ChipCAD

NAU7802 24-bit ADC - ChipCAD

NAU7802 24-bit ADC - ChipCAD

- No tags were found...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

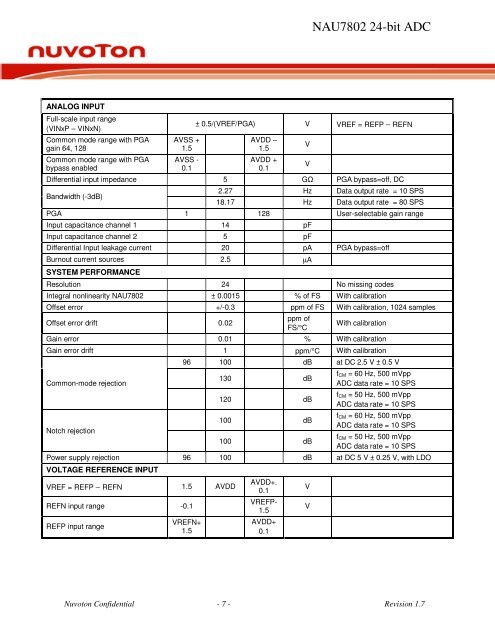

<strong>NAU7802</strong> <strong>24</strong>-<strong>bit</strong> <strong>ADC</strong>ANALOG INPUTFull-scale input range(VINxP – VINxN)Common mode range with PGAgain 64, 128Common mode range with PGAbypass enabledAVSS +1.5AVSS -0.1± 0.5/(VREF/PGA) V VREF = REFP − REFNAVDD –1.5AVDD +0.1Differential input impedance 5 GΩ PGA bypass=off, DCBandwidth (-3dB)VV2.27 Hz Data output rate = 10 SPS18.17 Hz Data output rate = 80 SPSPGA 1 128 User-selectable gain rangeInput capacitance channel 1 14 pFInput capacitance channel 2 5 pFDifferential Input leakage current 20 pA PGA bypass=offBurnout current sources 2.5 µASYSTEM PERFORMANCEResolution <strong>24</strong> No missing codesIntegral nonlinearity <strong>NAU7802</strong> ± 0.0015 % of FS With calibrationOffset error +/-0.3 ppm of FS With calibration, 10<strong>24</strong> samplesOffset error drift 0.02ppm ofFS/°CWith calibrationGain error 0.01 % With calibrationGain error drift 1 ppm/°C With calibrationCommon-mode rejectionNotch rejection96 100 dB at DC 2.5 V ± 0.5 V130 dB120 dB100 dB100 dBf CM = 60 Hz, 500 mVpp<strong>ADC</strong> data rate = 10 SPSf CM = 50 Hz, 500 mVpp<strong>ADC</strong> data rate = 10 SPSf CM = 60 Hz, 500 mVpp<strong>ADC</strong> data rate = 10 SPSf CM = 50 Hz, 500 mVpp<strong>ADC</strong> data rate = 10 SPSPower supply rejection 96 100 dB at DC 5 V ± 0.25 V, with LDOVOLTAGE REFERENCE INPUTVREF = REFP − REFN 1.5 AVDDREFN input range -0.1REFP input rangeVREFN+1.5AVDD+.0.1VREFP-1.5AVDD+0.1VVNuvoton Confidential - 7 - Revision 1.7