Simulation-based Verification with APRICOT Framework using High ...

Simulation-based Verification with APRICOT Framework using High ...

Simulation-based Verification with APRICOT Framework using High ...

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

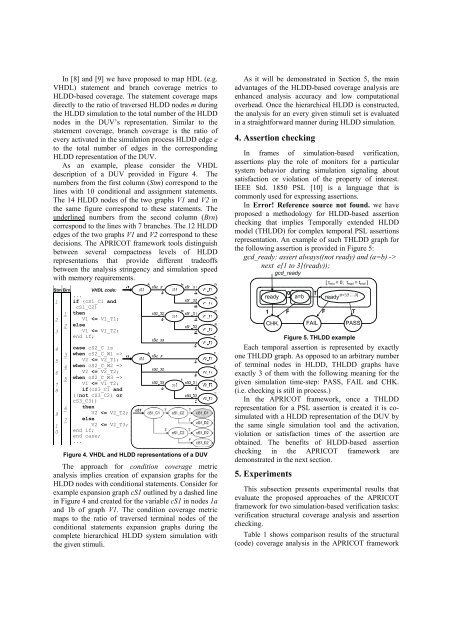

In [8] and [9] we have proposed to map HDL (e.g.VHDL) statement and branch coverage metrics toHLDD-<strong>based</strong> coverage. The statement coverage mapsdirectly to the ratio of traversed HLDD nodes m duringthe HLDD simulation to the total number of the HLDDnodes in the DUV’s representation. Similar to thestatement coverage, branch coverage is the ratio ofevery activated in the simulation process HLDD edge eto the total number of edges in the correspondingHLDD representation of the DUV.As an example, please consider the VHDLdescription of a DUV provided in Figure 4. Thenumbers from the first column (Stm) correspond to thelines <strong>with</strong> 10 conditional and assignment statements.The 14 HLDD nodes of the two graphs V1 and V2 inthe same figure correspond to these statements. Theunderlined numbers from the second column (Brn)correspond to the lines <strong>with</strong> 7 branches. The 12 HLDDedges of the two graphs V1 and V2 correspond to thesedecisions. The <strong>APRICOT</strong> framework tools distinguishbetween several compactness levels of HLDDrepresentations that provide different tradeoffsbetween the analysis stringency and simulation speed<strong>with</strong> memory requirements.Stm Brn VHDL code:...1 if (cS1_C1 andcS1_C2)1 then2 V1