the Elbrus Architecture Series for Servers and Supercomputers

1P7sT8P

1P7sT8P

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

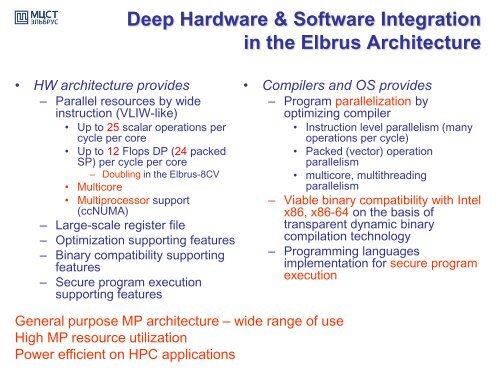

Deep Hardware & Software Integration<br />

in <strong>the</strong> <strong>Elbrus</strong> <strong>Architecture</strong><br />

• HW architecture provides<br />

– Parallel resources by wide<br />

instruction (VLIW-like)<br />

• Up to 25 scalar operations per<br />

cycle per core<br />

• Up to 12 Flops DP (24 packed<br />

SP) per cycle per core<br />

– Doubling in <strong>the</strong> <strong>Elbrus</strong>-8CV<br />

• Multicore<br />

• Multiprocessor support<br />

(ccNUMA)<br />

– Large-scale register file<br />

– Optimization supporting features<br />

– Binary compatibility supporting<br />

features<br />

– Secure program execution<br />

supporting features<br />

General purpose MP architecture – wide range of use<br />

High MP resource utilization<br />

Power efficient on HPC applications<br />

• Compilers <strong>and</strong> OS provides<br />

– Program parallelization by<br />

optimizing compiler<br />

• Instruction level parallelism (many<br />

operations per cycle)<br />

• Packed (vector) operation<br />

parallelism<br />

• multicore, multithreading<br />

parallelism<br />

– Viable binary compatibility with Intel<br />

x86, x86-64 on <strong>the</strong> basis of<br />

transparent dynamic binary<br />

compilation technology<br />

– Programming languages<br />

implementation <strong>for</strong> secure program<br />

execution