Anexo 2. - Departamento de TecnologÃa Electrónica

Anexo 2. - Departamento de TecnologÃa Electrónica

Anexo 2. - Departamento de TecnologÃa Electrónica

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

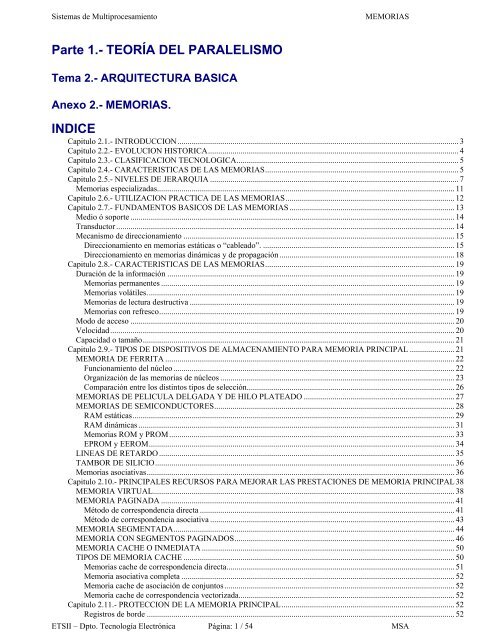

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASParte 1.- TEORÍA DEL PARALELISMOTema <strong>2.</strong>- ARQUITECTURA BASICA<strong>Anexo</strong> <strong>2.</strong>- MEMORIAS.INDICECapitulo <strong>2.</strong>1.- INTRODUCCION.......................................................................................................................................... 3Capitulo <strong>2.</strong><strong>2.</strong>- EVOLUCION HISTORICA........................................................................................................................... 4Capitulo <strong>2.</strong>3.- CLASIFICACION TECNOLOGICA............................................................................................................. 5Capitulo <strong>2.</strong>4.- CARACTERISTICAS DE LAS MEMORIAS............................................................................................... 5Capitulo <strong>2.</strong>5.- NIVELES DE JERARQUIA .......................................................................................................................... 7Memorias especializadas.................................................................................................................................................. 11Capitulo <strong>2.</strong>6.- UTILIZACION PRACTICA DE LAS MEMORIAS................................................................................... 12Capitulo <strong>2.</strong>7.- FUNDAMENTOS BASICOS DE LAS MEMORIAS ................................................................................. 13Medio ó soporte ............................................................................................................................................................... 14Transductor ...................................................................................................................................................................... 14Mecanismo <strong>de</strong> direccionamiento ..................................................................................................................................... 15Direccionamiento en memorias estáticas o “cableado”. .............................................................................................. 15Direccionamiento en memorias dinámicas y <strong>de</strong> propagación...................................................................................... 18Capitulo <strong>2.</strong>8.- CARACTERISTICAS DE LAS MEMORIAS............................................................................................. 19Duración <strong>de</strong> la información ............................................................................................................................................. 19Memorias permanentes ................................................................................................................................................ 19Memorias volátiles....................................................................................................................................................... 19Memorias <strong>de</strong> lectura <strong>de</strong>structiva .................................................................................................................................. 19Memorias con refresco................................................................................................................................................. 19Modo <strong>de</strong> acceso ............................................................................................................................................................... 20Velocidad......................................................................................................................................................................... 20Capacidad o tamaño......................................................................................................................................................... 21Capitulo <strong>2.</strong>9.- TIPOS DE DISPOSITIVOS DE ALMACENAMIENTO PARA MEMORIA PRINCIPAL ...................... 21MEMORIA DE FERRITA .............................................................................................................................................. 22Funcionamiento <strong>de</strong>l núcleo .......................................................................................................................................... 22Organización <strong>de</strong> las memorias <strong>de</strong> núcleos ................................................................................................................... 23Comparación entre los distintos tipos <strong>de</strong> selección...................................................................................................... 26MEMORIAS DE PELICULA DELGADA Y DE HILO PLATEADO .......................................................................... 27MEMORIAS DE SEMICONDUCTORES...................................................................................................................... 28RAM estáticas.............................................................................................................................................................. 29RAM dinámicas ........................................................................................................................................................... 31Memorias ROM y PROM............................................................................................................................................ 33EPROM y EEROM...................................................................................................................................................... 34LINEAS DE RETARDO ................................................................................................................................................. 35TAMBOR DE SILICIO................................................................................................................................................... 36Memorias asociativas....................................................................................................................................................... 36Capitulo <strong>2.</strong>10.- PRINCIPALES RECURSOS PARA MEJORAR LAS PRESTACIONES DE MEMORIA PRINCIPAL 38MEMORIA VIRTUAL.................................................................................................................................................... 38MEMORIA PAGINADA ................................................................................................................................................ 41Método <strong>de</strong> correspon<strong>de</strong>ncia directa ............................................................................................................................. 41Método <strong>de</strong> correspon<strong>de</strong>ncia asociativa ........................................................................................................................ 43MEMORIA SEGMENTADA.......................................................................................................................................... 44MEMORIA CON SEGMENTOS PAGINADOS............................................................................................................ 46MEMORIA CACHE O INMEDIATA ............................................................................................................................ 50TIPOS DE MEMORIA CACHE ..................................................................................................................................... 50Memorias cache <strong>de</strong> correspon<strong>de</strong>ncia directa................................................................................................................ 51Memoria asociativa completa ...................................................................................................................................... 52Memoria cache <strong>de</strong> asociación <strong>de</strong> conjuntos................................................................................................................. 52Memoria cache <strong>de</strong> correspon<strong>de</strong>ncia vectorizada.......................................................................................................... 52Capitulo <strong>2.</strong>11.- PROTECCION DE LA MEMORIA PRINCIPAL..................................................................................... 52Registros <strong>de</strong> bor<strong>de</strong> ....................................................................................................................................................... 52ETSII – Dpto. Tecnología Electrónica Página: 1 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASCapitulo <strong>2.</strong>1.- INTRODUCCIONLlamaremos memoria a todo dispositivo electrónico capaz <strong>de</strong> almacenar informaciones, <strong>de</strong> tal suerte que elórgano que se sirva <strong>de</strong> él pueda acce<strong>de</strong>r a la información solicitada en cualquier momento.En consecuencia, no consi<strong>de</strong>ramos como memorias las cintas y tarjetas perforadas, pero sí a la cinta magnéticauna vez montada en el dispositivo <strong>de</strong> lectura.La memoria es un bloque fundamental <strong>de</strong>l computador, cuya misión consiste en almacenar los datos y lasinstrucciones.La UCP (Unidad Central <strong>de</strong> Proceso), mediante su Unidad <strong>de</strong> Control y con el apoyo <strong>de</strong> los registros <strong>de</strong> trabajo,se encarga <strong>de</strong> buscar las instrucciones y datos en la memoria principal, realizar las operaciones a<strong>de</strong>cuadas con laALU y sacar o introducir información a/<strong>de</strong>s<strong>de</strong> los periféricos exteriores a través <strong>de</strong> los módulos <strong>de</strong> Entrada ySalida.Las transferencias entre bloques <strong>de</strong>l computador se hacen por un conjunto <strong>de</strong> líneas, que reciben el nombre <strong>de</strong>colectores o buses.A veces, la memoria principal no tiene la suficiente capacidad para contener todos los datos e instrucciones, encuyo caso se precisan otras memorias auxiliares o secundarias, que funcionan como periféricos <strong>de</strong>l sistema ycuya información se trasvasa a la memoria principal cuando se necesita.La memoria sólo pue<strong>de</strong> realizar dos operaciones básicas: lectura y escritura.En la lectura, el dispositivo <strong>de</strong> memoria <strong>de</strong>be recibir una dirección <strong>de</strong> la posición <strong>de</strong> la que se quiere extraer lainformación <strong>de</strong>positada previamente.En la escritura, a<strong>de</strong>más <strong>de</strong> la dirección, se <strong>de</strong>be suministrar la información que se <strong>de</strong>sea grabar.La mayoría <strong>de</strong> las memorias sólo son capaces <strong>de</strong> almacenar en sus celdas unPor tanto, se <strong>de</strong>nomina punto <strong>de</strong> memoria al elemento que almacena un bit.bit, puesto a 1 ó 0.ETSII – Dpto. Tecnología Electrónica Página: 3 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASLa implementación práctica, <strong>de</strong> un punto <strong>de</strong> memoria es muy diversa y <strong>de</strong>pen<strong>de</strong> <strong>de</strong> la tecnología <strong>de</strong> fabricación.El punto <strong>de</strong> memoria pue<strong>de</strong> ser perfectamente <strong>de</strong>finido e individualizado en el espacio y constará, a<strong>de</strong>más <strong>de</strong>ldispositivo <strong>de</strong> almacenamiento, <strong>de</strong> los <strong>de</strong> lectura y escritura: es el caso <strong>de</strong>l biestable electrónico (flip-flops) o <strong>de</strong>lnúcleo <strong>de</strong> ferrita.Pue<strong>de</strong> correspon<strong>de</strong>r a una zona <strong>de</strong> una superficie continua, como suce<strong>de</strong> en una cinta magnética.Incluso pue<strong>de</strong> no tener soporte fijo como es el caso <strong>de</strong> un impulso eléctrico que, entre otros, recircula por unalínea <strong>de</strong> retardo cerrada sobre sí misma y como ocurre con las memorias <strong>de</strong> burbujas magnéticas.Capitulo <strong>2.</strong><strong>2.</strong>- EVOLUCION HISTORICAEn los calculadores <strong>de</strong> la década <strong>de</strong> los 30 se emplean tarjetas perforadas como memorias.La dirección <strong>de</strong> las posiciones quedaba <strong>de</strong>terminada por la posición <strong>de</strong> ruedas <strong>de</strong>ntadas.Luego se emplearon relés electromagnéticos.El computador ENIAC utilizaba, en 1946, válvulas electrónicas <strong>de</strong> vacío para construir sus biestables queactuaban como punto <strong>de</strong> memoria. A<strong>de</strong>más, tenía una ROM <strong>de</strong> 4 Kbits construida a base <strong>de</strong> resistencias.Al comienzo <strong>de</strong> la década <strong>de</strong> los 50, se usaron las líneas <strong>de</strong> retardo <strong>de</strong> mercurio con 1 Kbit por línea, comomemoria. Igualmente se empleó el tubo <strong>de</strong> Williams, que tenía una capacidad <strong>de</strong> 1.200 bits y consistía en un tubo<strong>de</strong> rayos catódicos con memoria.El UNIVAC 1 introdujo en 1951 la primera unidad comercial <strong>de</strong> banda magnética, que tenía una capacidad <strong>de</strong> 1,44Mbit y una velocidad <strong>de</strong> 100 pulgadas/s.El primer computador comercial que usó como memoria principal al tambor magnético fue el IBM 650 en 1954.Dicho tambor giraba a 1<strong>2.</strong>500 r.p.m. y tenía una capacidad <strong>de</strong> 120 Kbits.En 1953, el MIT dispuso <strong>de</strong> la primera memoria operativa <strong>de</strong> ferritas, que fue muy popular hasta mediados <strong>de</strong> losaños 70.Fue IBM, en 1968, quien diseñó la primera memoria comercial <strong>de</strong> semiconductores.Tenía una capacidad <strong>de</strong> 64 bits.También, el mo<strong>de</strong>lo 350 <strong>de</strong> IBM en 1956 fue quien utilizó el primer disco con brazo móvil y cabeza flotante.Su capacidad era <strong>de</strong> 40 Mbits y su tiempo <strong>de</strong> acceso, <strong>de</strong> 500 ms.Tecnologías nuevas, como la <strong>de</strong> burbujas magnéticas, efecto Josephson, acoplamiento <strong>de</strong> carga, <strong>de</strong> tipo óptico yotras, compiten en la actualidad por <strong>de</strong>splazar a las memorias <strong>de</strong> semiconductor basadas en silicio, que ya hanalcanzadocapacida<strong>de</strong>s superiores a 1 GB en una pastilla con rapidísimo tiempo <strong>de</strong> acceso y coste razonable.ETSII – Dpto. Tecnología Electrónica Página: 4 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASCapitulo <strong>2.</strong>3.- CLASIFICACION TECNOLOGICAMuy diversos fenómenos físicos pue<strong>de</strong>n utilizarse para realizar el punto <strong>de</strong> memoria.Des<strong>de</strong> este punto <strong>de</strong> vista es posible distinguir tres gran<strong>de</strong>s clases <strong>de</strong> memorias.1. Las memorias estáticas, divisibles en dos grupos:a) las memorias a las que se acce<strong>de</strong> por impulsos eléctricos, como por ejemplo los biestables <strong>de</strong>semiconductores, los núcleos <strong>de</strong> ferrita, las memorias <strong>de</strong> película magnética <strong>de</strong>lgada en la unidadcentral, yb) las memorias a las que se acce<strong>de</strong> por haces luminosos o electrónicos, <strong>de</strong> posible uso en el futuro<strong>2.</strong> Las memorias <strong>de</strong> propagación, en las cuales las discontinuida<strong>de</strong>s físicas se propagan <strong>de</strong> maneracíclica. Citemos las vibraciones electromagnéticas en líneas <strong>de</strong> retardo y las sónicas en las líneasmagnetoestrictivas, que se utilizan en aplicaciones peculiares.Citemos también el <strong>de</strong>splazamiento <strong>de</strong> burbujas magnéticas bajo el efecto <strong>de</strong> un campo rotatorio,fenómeno que pue<strong>de</strong> constituir la base <strong>de</strong> las memorias auxiliares <strong>de</strong>l futuro.3. Las memorias dinámicas, en las cuales se usa <strong>de</strong> la permanencia <strong>de</strong> una superficie magnética, que sehace <strong>de</strong>sfilar ante unas cabezas <strong>de</strong> lectura y escritura, para registrar sobre ella la información.Es el campo <strong>de</strong> las actuales memorias auxiliares: cintas magnéticas, discos y tambores, láminas magnéticas.Capitulo <strong>2.</strong>4.- CARACTERISTICAS DE LAS MEMORIAS‣ Volatilidad.En las memorias estáticas gobernadas por conmutación electrónica, se dice que la informaciónalmacenada es volátil si corre el riesgo <strong>de</strong> verse alterada por un fallo <strong>de</strong> alimentación eléctrica (es el caso<strong>de</strong> las memorias constituidas por biestables electrónicos) y no volátil en el caso contrario (utilización <strong>de</strong>fenómenos magnéticos remanentes, por ejemplo).‣ Lectura y escritura.Son las operaciones básicas <strong>de</strong> las memorias.Se realiza escritura cuando se registran informaciones en la memoria y lectura cuando se extraeninformaciones previamente registradas.La lectura pue<strong>de</strong> ser <strong>de</strong>structiva (la información leída se borra <strong>de</strong> la memoria) o no <strong>de</strong>structiva.La escritura pue<strong>de</strong> exigir o no exigir un borrado previo.Las memorias <strong>de</strong> semiconductores son <strong>de</strong> lectura no <strong>de</strong>structiva y no obligan forzosamente a un borradoprevio a la escritura, mientras que en las memorias <strong>de</strong> núcleos la lectura es <strong>de</strong>structiva y la escritura exigeun borrado previo.‣ Direccionamiento.Para localizar una información <strong>de</strong>ntro <strong>de</strong> una memoria, la computadora <strong>de</strong>be saber dón<strong>de</strong> la ha colocadoanteriormente. Es la función <strong>de</strong>l direccionamiento.En las memorias en que el punto <strong>de</strong> memoria está perfectamente individualizado, el emplazamiento <strong>de</strong> lasinformaciones y, por consiguiente, su dirección exacta, preexiste a toda operación <strong>de</strong> almacenamiento:éste es el caso <strong>de</strong> las memorias <strong>de</strong> núcleos, don<strong>de</strong> cada célula <strong>de</strong> memoria posee su dirección.Por el contrario, en memorias tales como las cintas magnéticas, el emplazamiento <strong>de</strong> las informaciones<strong>de</strong>pen<strong>de</strong> <strong>de</strong> la operación <strong>de</strong> registro <strong>de</strong> las mismas.Una información no es individualmente direccionable y no existe relación entre dirección y emplazamiento.Las informaciones se agrupan por bloques o registros. La dirección <strong>de</strong> la información consta <strong>de</strong> doselementos: el nombre <strong>de</strong>l registro, o indicativo, y el número <strong>de</strong> or<strong>de</strong>n <strong>de</strong> la información <strong>de</strong>ntro <strong>de</strong>l registro.De hecho, no se tiene físicamente acceso más que al conjunto <strong>de</strong>l registro.ETSII – Dpto. Tecnología Electrónica Página: 5 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIAS‣ Modo <strong>de</strong> acceso.En el caso <strong>de</strong> las memorias <strong>de</strong> núcleos, se tiene acceso directamente a cualquier información, cuyadirección sea conocida, en una cantidad <strong>de</strong> tiempo in<strong>de</strong>pendiente <strong>de</strong> dicha dirección.El acceso a este tipo <strong>de</strong> memoria es aleatorio, o directo, o selectivo.Opuestamente, para acce<strong>de</strong>r a una información en cinta magnética, es necesario <strong>de</strong>senrollar la cinta,leyendo los indicativos <strong>de</strong> los registros, hasta encontrar el que se busca. El acceso a la información eneste tipo <strong>de</strong> memoria es secuencial. A título <strong>de</strong> ejemplo, el acceso a ciertos discos con cabezas móviles esselectivo al nivel <strong>de</strong> elección <strong>de</strong> la cabeza y <strong>de</strong> su posicionamiento, o sea al nivel <strong>de</strong> la pista, y secuencialen el interior <strong>de</strong> la pista (figura).A menudo se llaman memorias <strong>de</strong> acceso por bloques a las memorias <strong>de</strong> propagación y las memoriasmagnéticas dinámicas, en las que, para acce<strong>de</strong>r a una información, es preciso esperar a que ésta pasepor el dispositivo <strong>de</strong> lectura/escritura. En estas condiciones, las informaciones no son manipuladasindividualmente, sino bajo el régimen <strong>de</strong> bloques. La utilización <strong>de</strong> una información individual implica unatransferencia previa <strong>de</strong>l bloque a la memoria central.Por lo que respecta a la medida <strong>de</strong> la eficacia operativa, esto nos conduce a distinguir el tiempo <strong>de</strong> accesoa la primera información <strong>de</strong>l bloque, y el caudal <strong>de</strong> las informaciones contenidas en el bloque entre lamemoria auxiliar y la memoria central.‣ Tiempo <strong>de</strong> acceso.Es el tiempo que transcurre entre el instante en que se lanza una operación <strong>de</strong> lectura en memoria y elinstante en que se dispone <strong>de</strong> la primera información buscada.En las memorias estáticas es in<strong>de</strong>pendiente, en general, <strong>de</strong>l emplazamiento <strong>de</strong> las informaciones.Para calcular el tiempo <strong>de</strong> acceso en las memorias magnéticas dinámicas pue<strong>de</strong> <strong>de</strong>spreciarse la duración<strong>de</strong> las conmutaciones electrónicas ante los tiempos <strong>de</strong> posicionamiento. Es así como el tiempo <strong>de</strong> acceso<strong>de</strong> un tambor magnético poseedor <strong>de</strong> una cabeza por pista <strong>de</strong>pen<strong>de</strong> <strong>de</strong> las posiciones relativas <strong>de</strong> lainformación buscada y <strong>de</strong> la información situada en trance <strong>de</strong> lectura o <strong>de</strong> escritura.Iguala, en promedio, a la mitad <strong>de</strong>l tiempo total <strong>de</strong> rotación. El tiempo <strong>de</strong> acceso <strong>de</strong> una pila <strong>de</strong> discos concabezas móviles compren<strong>de</strong> el tiempo <strong>de</strong> posicionamiento <strong>de</strong> las cabezas y el tiempo <strong>de</strong> rotación.La noción <strong>de</strong> tiempo <strong>de</strong> acceso no tiene mucho sentido en lo que atañe a la cinta magnética: pue<strong>de</strong> llegara ser <strong>de</strong> varios minutos en la hipótesis favorable <strong>de</strong> que la cinta esté ya montada en el bobinador.‣ Caudal: así se llama al número máximo <strong>de</strong> informaciones leídas o escritas por unidad <strong>de</strong> tiempo.Para las memorias <strong>de</strong> acceso por bloques se supone que las informaciones están situadas en lugaressucesivos <strong>de</strong> la memoria.El caudal se expresa generalmente en kilo-informaciones o mega-informaciones por segundo.Por ejemplo, podrá hablarse <strong>de</strong> una velocidad <strong>de</strong> transferencia o caudal <strong>de</strong> un mega-octeto por segundo.El caudal <strong>de</strong> un tambor magnético es igual al número <strong>de</strong> palabras por pista dividido por el tiempo <strong>de</strong>rotación. La duración <strong>de</strong> una operación <strong>de</strong> entrada-salida sobre un tambor es la suma <strong>de</strong>l tiempo <strong>de</strong>acceso y <strong>de</strong>l tiempo real <strong>de</strong> transferencia, este último inversamente proporcional al caudal.ETSII – Dpto. Tecnología Electrónica Página: 6 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIAS‣ Capacidad.Es el número <strong>de</strong> informaciones que contiene la memoria.Se hablará, por ejemplo, <strong>de</strong> una memoria <strong>de</strong> núcleos <strong>de</strong> 4.096 palabras, <strong>de</strong> un disco <strong>de</strong> 4 millones <strong>de</strong>octetos. Habida cuenta <strong>de</strong>l direccionamiento binario, las capacida<strong>de</strong>s <strong>de</strong> las memorias se expresanhabitualmente por potencias <strong>de</strong>dos: 1024, 4096, 8192 palabras, etc.‣ Intercambiabilidad.En las memorias magnéticas dinámicas los soportes <strong>de</strong> información son frecuentemente indisociables <strong>de</strong>su unidad <strong>de</strong> explotación, como suce<strong>de</strong> en los tambores o discos <strong>de</strong> cabezas fijas; también pue<strong>de</strong>n serintercambiables, como <strong>de</strong>terminados discos <strong>de</strong> cabezas móviles o como las cintas magnéticas.Capitulo <strong>2.</strong>5.- NIVELES DE JERARQUIALa memoria principal, abastece a la UCP <strong>de</strong> datos e instrucciones.Como la UCP se construye con circuitos integrados rapidísimos, obliga a que la memoria emplee un tiempomínimo en grabar y obtener información.Sin embargo, las memorias rápidas son <strong>de</strong> pequeña capacidad, por lo que existirá un nivel veloz, pero <strong>de</strong> pocotamaño, en el computador, que actúe como memoria principal así como niveles sucesivos <strong>de</strong> menor rapi<strong>de</strong>z ymayor capacidad.La información se <strong>de</strong>posita en uno <strong>de</strong> los niveles <strong>de</strong> acuerdo a su prioridad <strong>de</strong> uso.Así, cuando un programa o unos datos <strong>de</strong> archivo son poco empleados, se almacenan en el nivel inferior máslento y <strong>de</strong> mayor capacidad; si en un momento <strong>de</strong>terminado se necesitan, se trasladan al nivel superior másrápido.A<strong>de</strong>más <strong>de</strong> la velocidad operativa <strong>de</strong> una memoria o tiempo <strong>de</strong> acceso a la información y la capacidad <strong>de</strong>almacenamiento, existe otra propiedad fundamental, que influye en la <strong>de</strong>terminación <strong>de</strong> su nivel jerárquico; setrata <strong>de</strong>l coste/bit.Estas tres características son contrapuestas, es <strong>de</strong>cir, que si se <strong>de</strong>sea un tiempo <strong>de</strong> acceso muy bajo, el coste/bitserá alto y la capacidad o tamaño será bajo.ETSII – Dpto. Tecnología Electrónica Página: 7 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASLa memoria i<strong>de</strong>al <strong>de</strong>be poseer una capacidad elevada junto a un tiempo <strong>de</strong> acceso muy pequeño y un precioreducido. Dichas características, por ahora, son tecnológica y económicamente irreconciliables.ETSII – Dpto. Tecnología Electrónica Página: 8 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASHay que recurrir a una "especialización", usando memorias muy rápidas y <strong>de</strong> pequeña capacidad en aquellaspartes <strong>de</strong>l sistema en las que la velocidad es el factor predominante.Las memorias lentas y <strong>de</strong> gran capacidad se <strong>de</strong>stinarán a las partes don<strong>de</strong> prime o sobresalga el factorcapacidad.Se ha llegado a establecer una jerarquía <strong>de</strong> las memorias, sobre todo a dos niveles:‣ Memoria central relativamente rápida pero <strong>de</strong> capacidad bastante limitada;‣ Memoria auxiliar <strong>de</strong> mucha mayor capacidad pero con un tiempo <strong>de</strong> acceso consi<strong>de</strong>rable.Se pue<strong>de</strong>n distinguir los siguientes niveles jerárquicos:a) Memorias cache o tampón.Son <strong>de</strong> acceso aleatorio, caracterizadas por su elevada eficacia y baja capacidad (16 Kbyte).Se utilizan en las máquinas <strong>de</strong> la tercera generación en funciones <strong>de</strong> memoria local o tampón en la unidadcentral o en los canales.Tecnológicamente, se fabrican con semiconductores generalmente, excepcionalmente con películasmagnéticas finas.Sus tiempos <strong>de</strong> acceso oscilan entre los 20 y los 200 ns.b) Memoria central o principal.De acceso aleatorio puesto que en ella busca la unidad central precisamente la información que necesita,Sin embargo, en la primera generación se utilizaron tambores magnéticos y líneas <strong>de</strong> magnetoestricciónpara estas funciones. También fue el campo predilecto <strong>de</strong> las memorias magnéticas estáticas: memorias<strong>de</strong> núcleos, menos frecuentemente memorias <strong>de</strong> película magnética fina;Hoy, es se comienza a utilizar memorias <strong>de</strong> semiconductores.Capacidad no muy alta (128 KB - 100 MB) y tiempo <strong>de</strong> acceso comprendido entre los 200 ns y los 2 us.Generalmente están fabricadas con semiconductores.Actualmente, la capacidad <strong>de</strong> la memoria central sigue la ley <strong>de</strong> la duplicación cada dos años.c) Memorias intermedias.Suelen ser <strong>de</strong> acceso secuencialEsta primera clase <strong>de</strong> memoria auxiliar incluye memorias <strong>de</strong> capacidad bastante gran<strong>de</strong> (varios millones<strong>de</strong> caracteres, 10 G) con tiempos <strong>de</strong> acceso muy parecidos a los <strong>de</strong> las memorias centrales (variosmicrosegundos a varios ms).Actualmente, las soluciones magnéticas estáticas son las únicas disponibles.Realmente este nivel no se ha extendido mucho y suele ser sustituido por un nivel <strong>de</strong> memoria secundariareferente al disco <strong>de</strong> cabeza fija y <strong>de</strong> uso exclusivo <strong>de</strong>l Sistema Operativo y por el nivel <strong>de</strong> memoriaauxiliar, que incluye a los discos móviles y las cintas.d) Memorias auxiliares.Son memorias <strong>de</strong> acceso selectivo, caracterizadas por capacida<strong>de</strong>s mucho mayores, tiempos <strong>de</strong> accesoconsi<strong>de</strong>rables y gran<strong>de</strong>s velocida<strong>de</strong>s <strong>de</strong> transferencia.Se acce<strong>de</strong> en ellas a bloques <strong>de</strong> información que son transferidos a memoria central para ser utilizadosallí. En el momento presente es campo casi exclusivo <strong>de</strong> las memorias magnéticas dinámicas, cuyo bajocoste por bit autoriza capacida<strong>de</strong>s importantes y cuyo caudal pue<strong>de</strong> alcanzar varios mega-caracteres porsegundo: se distinguen los tambores y discos con cabezas fijas (tiempo <strong>de</strong> acceso <strong>de</strong> 5 a 20 ms), losdiscos con cabezas móviles, frecuentemente intercambiables (tiempo <strong>de</strong> acceso: 50 a 100 ms), lasmemorias con láminas magnéticas (tiempo <strong>de</strong> acceso: 200 a 600 ms).e) Memorias ficheros.Son las cintas magnéticas, caracterizadas por su acceso secuencial, que implica tiempos <strong>de</strong> acceso <strong>de</strong>hasta varios minutos, y por su intercambiabilidad que procura una capacidad casi infinita <strong>de</strong>almacenamiento, pero que implica manipulaciones humanas <strong>de</strong> búsqueda y montaje en los bobinadores.Este carácter <strong>de</strong> intercambiabilidad sirve también para permutar informaciones entre computadores.El caudal <strong>de</strong> las cintas magnéticas pue<strong>de</strong> oscilar entre 15 y 300 kilo-caracteres por segundos.ETSII – Dpto. Tecnología Electrónica Página: 9 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASEn la tabla se recoge una clasificación jerárquica <strong>de</strong> la memoria, junto a sus características más relevantes.Zonas <strong>de</strong> utilización <strong>de</strong> las diferentes clases <strong>de</strong> memorias, habida cuenta <strong>de</strong> las limitaciones tecnológicas y <strong>de</strong> lasconsi<strong>de</strong>raciones <strong>de</strong> precio.ETSII – Dpto. Tecnología Electrónica Página: 10 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASMemorias especializadasDentro <strong>de</strong> esta categoría incluimos aquellas memorias que, por la peculiaridad <strong>de</strong> su funcionamiento, estánabocadas a aplicaciones especiales.Distinguiremos tres tipos: las pilas y colas <strong>de</strong> espera cableadas, las memorias muertas o reinscriptibles, y lasmemorias asociativas.‣ Las pilas y colas <strong>de</strong> espera cableadas.Se caracteriza a menudo por el hecho <strong>de</strong> que ciertas operaciones implican un <strong>de</strong>splazamiento global <strong>de</strong>toda la información contenida en la memoria.Así, por ejemplo, la inserción <strong>de</strong> una información en una pila cableada "empuja" el contenido <strong>de</strong> la pila enun "peldaño" mientras que la extracción "atrae” el contenido <strong>de</strong> la pila en un peldaño.Pue<strong>de</strong>n materializarse tales memorias en pequeña capacidad por medio <strong>de</strong> lógicas celulares a base <strong>de</strong>semiconductores.Las colas <strong>de</strong> espera cableadas se emplean con frecuencia para compensar la diferencia <strong>de</strong> caudal <strong>de</strong> dosórganos entre los que se establece una comunicación. En tales casos, se <strong>de</strong>nominan memorias-tampón.‣ Memorias muertas.Las memorias muertas o memorias <strong>de</strong> sólo lectura son memorias que no pue<strong>de</strong>n operarse más que enlectura.Las memorias reinscriptibles permiten una lectura rápida, pero una reescritura lenta.Se utilizan en el campo <strong>de</strong> la microprogramación.‣ Memorias asociativas.En las memorias <strong>de</strong> acceso aleatorio, se proporciona una dirección y se recupera la información en ellacontenida.Las memorias asociativas, o memorias direccionables por el contenido, respon<strong>de</strong>n al problema siguiente:¿está contenida en la memoria una <strong>de</strong>terirnínada información, llamada <strong>de</strong>scriptor? y, sí está contenida,¿ en que posición?ETSII – Dpto. Tecnología Electrónica Página: 11 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASCapitulo <strong>2.</strong>6.- UTILIZACION PRACTICA DE LAS MEMORIASA nivel <strong>de</strong> sistema, los dispositivos <strong>de</strong> memoria pue<strong>de</strong>n contemplarse como bloques a los que hay que suministraruna dirección y una señal <strong>de</strong> control para especificar la operación que se <strong>de</strong>sea realizar; a<strong>de</strong>más, hay que enviaro recibir el dato o bloque correspondiente.Las memorias <strong>de</strong> acceso aleatorio utilizan acceso individualizado a nivel <strong>de</strong> palabra.Para hacer la conexión con el resto <strong>de</strong>l sistema, se suelen emplear dos registros, uno que almacena la dirección yel otro, el dato a leer o escribir.El registro D <strong>de</strong> direcciones tendrá una longitud d, tal que 2 sea mayor o igual que la capacidad <strong>de</strong> la memoria.El registro M <strong>de</strong> datos tendrá una longitud m igual al tamaño <strong>de</strong> la palabra con que trabaja la memoria.Ambos registros se encuentran conectados a los buses <strong>de</strong>l sistema.Las señales <strong>de</strong> control indicarán a la memoria el tipo <strong>de</strong> operación a realizar, así como el comienzo <strong>de</strong> dichaoperación. La memoria, a su vez, pue<strong>de</strong> generar una señal <strong>de</strong> control <strong>de</strong> fin <strong>de</strong> la operación, muy útil en lasincronización con el sistema.dETSII – Dpto. Tecnología Electrónica Página: 12 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASExiste la posibilidad <strong>de</strong> construir memorias con varias parejas <strong>de</strong> registros D y M, llamadas memoriasmultipuerta.Las memorias <strong>de</strong> acceso aleatorio forman la memoria principal <strong>de</strong>l sistema y su conexión es directa a los buses<strong>de</strong>l mismo.Sin embargo, las memorias dinámicas forman la memoria auxiliar y su conexión se efectúa mediante una unidad<strong>de</strong> intercambio.Capitulo <strong>2.</strong>7.- FUNDAMENTOS BASICOS DE LAS MEMORIASPara que un dispositivo <strong>de</strong> memoria pueda realizar sus funciones principales <strong>de</strong> lectura y escritura, ha <strong>de</strong> disponer<strong>de</strong> tres elementos:1. Medio o soporte:Don<strong>de</strong> se almacenan estados <strong>de</strong> energía diferentes, que codifican la información guardada.<strong>2.</strong> Transductores:Tanto en la lectura como para la escritura, son capaces <strong>de</strong> generar la energía necesaria en la grabación y<strong>de</strong>tectar el estado existente en la lectura.3. Mecanismo <strong>de</strong> direccionamiento:Permite leer y escribir la información en el lugar y tiempos precisos.ETSII – Dpto. Tecnología Electrónica Página: 13 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASMedio ó soportePara que un medio sirva como almacén <strong>de</strong> información, ha <strong>de</strong> presentar, al menos, dos estados estables (osemiestables), que se caractericen por una magnitud física discreta, por ejemplo, el momento magnético, la cargaeléctrica, la corriente, etc.A<strong>de</strong>más, se ha <strong>de</strong> po<strong>de</strong>r pasar <strong>de</strong> un estado a otro mediante la aplicación <strong>de</strong> una señal (energía) externa, y se ha<strong>de</strong> po<strong>de</strong>r <strong>de</strong>tectar el estado existente en un momento <strong>de</strong>terminado. Finalmente, ha <strong>de</strong> ser posible cambiar <strong>de</strong>estado tantas veces como se quiera sin que sufra o se modifique el medio.Los medios o soportes más empleados son los <strong>de</strong> tipo magnético.Se construyen <strong>de</strong> forma que presenten una dirección preferente <strong>de</strong> magnetización, que llamaremos A B.Si se magnetiza mediante un campo externo el medio en el sentido A B, tenemos un estado, mientras que, sise magnetiza en sentido contrario A B, tenemos el otro.Los medios pue<strong>de</strong>n ser discretos o continuos.En el primer caso se emplea un dispositivo físico aislado para almacenar cada bit, mientras que en el segundo sealmacenan unos a continuación <strong>de</strong> otros en el mismo medio, distinguiéndose entre sí por el método <strong>de</strong> escritura.El toro <strong>de</strong> ferrita y el biestable son medios discretos, y la cinta o el disco son medios continuos.En general, los medios discretos son más caros que los continuos, pero requieren unos transductores mássencillos y presentan un direccionamiento más rápido y sencillo.Los medios pue<strong>de</strong>n clasificarse atendiendo al tiempo que la información permanece grabada sobre ellos.Hay tres tipos:1) La información se mantiene <strong>de</strong> forma permanente. Suele ser lo normal en medios magnéticos.Se dice que la memoria es no volátil.2) La información <strong>de</strong>saparece cuando se <strong>de</strong>ja <strong>de</strong> alimentar o suministrar energía a la memoria.Por ejemplo, esto ocurre con las memorias con semiconductores, tipo RAM.Entonces la memoria es volátil.3) La información se va <strong>de</strong>gradando paulatinamente y llega un momento en que no se pue<strong>de</strong> leer.Esto suce<strong>de</strong> con los con<strong>de</strong>nsadores, que, cuando están cargados con una tensión, pue<strong>de</strong>n representar unestado, y <strong>de</strong>scargados, el otro.Sin embargo, los con<strong>de</strong>nsadores, al no ser perfectos, van <strong>de</strong>scargándose hasta que pier<strong>de</strong>n lainformación, Para que estos tipos <strong>de</strong> memoria sean útiles, hay que recargar a todos sus elementosperiódicamente para compensar las pérdidas; esta acción se conoce como refresco.Finalmente, y como ya se ha dicho, hay medios que guardan una equivalencia entre una posición física y un punto<strong>de</strong> memoria, es <strong>de</strong>cir, la información permanece fija en el medio, como en un disco, pero hay otros medios en losque la información se traslada, como en las memorias <strong>de</strong> burbujas magnéticas.TransductorHay transductores <strong>de</strong> lectura y <strong>de</strong> escritura.La función <strong>de</strong> los transductores <strong>de</strong> escritura es suministrar la energía necesaria al medio para que adopte elestado <strong>de</strong>seado.Por otro lado, la función <strong>de</strong> los transductores <strong>de</strong> lectura es <strong>de</strong>tectar las magnitu<strong>de</strong>s físicas para reconocer elestado en que se encuentra el medio.Los transductores suelen ser caros, por lo que se tien<strong>de</strong> a reducir su número, pero <strong>de</strong>be existir un compromisoentre el número <strong>de</strong> transductores y la velocidad <strong>de</strong> la memoria: si hay pocos transductores, la memoria será lenta.Los transductores pue<strong>de</strong>n estar físicamente unidos al medio o pue<strong>de</strong>n ser in<strong>de</strong>pendientes <strong>de</strong> él.En el primer caso, hay un cableado que permite acce<strong>de</strong>r al punto <strong>de</strong> memoria <strong>de</strong>seado.En el segundo, el punto <strong>de</strong> memoria al que se quiere acce<strong>de</strong>r <strong>de</strong>be posicionarse frente al transductor para realizarla operación <strong>de</strong> lectura y escritura.ETSII – Dpto. Tecnología Electrónica Página: 14 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASComo ejemplos <strong>de</strong> estas dos situaciones se pue<strong>de</strong>n citar las memorias <strong>de</strong> ferritas, en la cual los transductoresestán unidos <strong>de</strong> forma fija a las ferritas por conductores eléctricos, y la cinta magnética, en la que se <strong>de</strong>beenfrentar al cabezal <strong>de</strong> lectura/escritura la zona a la que se preten<strong>de</strong> acce<strong>de</strong>r.Reciben el nombre <strong>de</strong> memorias estáticas las que tienen el transductor unido al medio y dinámicas aquéllasen las que <strong>de</strong>be moverse el medio para posicionarse frente al transductor.Los transductores <strong>de</strong> las memorias dinámicas, por lo general, trabajan con unos niveles <strong>de</strong> señal muy bajos, por loque son más caros que los fijos.De todas formas, la relación número <strong>de</strong> bits por sensor es mucho mayor que en las estáticas, en las cuales lostransductores están cableados a unos pocos puntos <strong>de</strong> memoria, por lo que el coste final por bit es mucho menor.Mecanismo <strong>de</strong> direccionamientoSe encarga <strong>de</strong> seleccionar el punto <strong>de</strong> memoria <strong>de</strong>seado.En una memoria estática el mecanismo <strong>de</strong> direccionamiento es inherente a su propia construcción.El conexionado <strong>de</strong> los transductores, junto a la selección <strong>de</strong> estos últimos, específica <strong>de</strong> forma inequívoca elpunto <strong>de</strong> memoria al que se acce<strong>de</strong>. Por este motivo, este tipo <strong>de</strong> memorias reciben la <strong>de</strong>nominación <strong>de</strong>memorias <strong>de</strong> direccionamiento cableado.Por el contrario, en las memorias dinámicas, al estar compartidos los transductores, no existe la mencionadarelación. La selección se consigue mediante la Unidad <strong>de</strong> Control que interpreta una información adicional, que sellama información <strong>de</strong> direccionamiento, y que se almacena junto a los datos.A continuación se presentan los diferentes tipos <strong>de</strong> direccionamientos:Direccionamiento en memorias estáticas o “cableado”.El mecanismo <strong>de</strong> direccionamiento <strong>de</strong> una memoria estática ofrece dos formas típicas llamadas 2D y 3D.mPara analizarlas se consi<strong>de</strong>ra que la memoria tiene 2 palabras <strong>de</strong> n bits cada una.Se <strong>de</strong>sea acce<strong>de</strong>r a los n bits <strong>de</strong> una palabra, cuya dirección precisa <strong>de</strong> m bits para que que<strong>de</strong> <strong>de</strong>finida.Direccionamiento 2D: En este direccionamiento todos lo s bits <strong>de</strong> la misma posición en cada palabra (bits 0, 1,...)están conectados a la misma pareja <strong>de</strong> transductores.Habrá n parejas <strong>de</strong> transductores.mm * 2Para seleccionar la palabra <strong>de</strong>seada se <strong>de</strong>codifican los m bits <strong>de</strong> dirección en un <strong>de</strong>codificador , que tieneuna señal <strong>de</strong> salida individualizada para cada palabra <strong>de</strong> memoria.Se usa la misma conexión para la lectura que para la escritura, bastando activar al transductor correspondientepara <strong>de</strong>finir la operación.ETSII – Dpto. Tecnología Electrónica Página: 15 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASDireccionamiento 3D: Como indica la figura se establecen n planos <strong>de</strong> memoria (uno para cada bit <strong>de</strong> la palabra).Dentro <strong>de</strong> cada plano se selecciona el punto <strong>de</strong> memoria haciendo coincidir las líneas <strong>de</strong> selección X e Y.ETSII – Dpto. Tecnología Electrónica Página: 16 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASmx myLa dirección <strong>de</strong> m bits se divi<strong>de</strong> en dos partes mx y my, que se <strong>de</strong>codifican en dos <strong>de</strong>codificadores <strong>de</strong> 2 y 2 .mx mymx+myLas señales <strong>de</strong> salida 2 + 2 se usan como coor<strong>de</strong>nadas que seleccionan entre las 2m= 2 posiciones<strong>de</strong> cada plano <strong>de</strong> la memoria.Cada plano tiene una pareja <strong>de</strong> transductores <strong>de</strong> lectura y escritura, que están conectados a todos los puntos <strong>de</strong>lplano.La ventaja <strong>de</strong>l método 3D estriba en que dos <strong>de</strong>codificadores <strong>de</strong> mx y my entradas son mucho más sencillos queuno <strong>de</strong> mx+my=m entradas. Como inconveniente, el punto <strong>de</strong> memoria es más complejo, puesto que <strong>de</strong>be sercapaz <strong>de</strong> activarse sólo cuando sus dos líneas x e y estén activas.Direccionamiento 2D1/2: Es un direccionamiento en el que se emplean más transductores que los n necesarios enlos casos anteriores.La selección <strong>de</strong> los puntos <strong>de</strong> memoria se hace mediante la coinci<strong>de</strong>ncia <strong>de</strong> una línea <strong>de</strong> <strong>de</strong>codificación X y laelección <strong>de</strong>l bloque <strong>de</strong> transductores a<strong>de</strong>cuado.ETSII – Dpto. Tecnología Electrónica Página: 17 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASDireccionamiento en memorias dinámicas y <strong>de</strong> propagaciónEn estas memorias hay que añadir una información adicional <strong>de</strong> direccionamiento, que se almacena ocupandoparte <strong>de</strong> los puntos <strong>de</strong> memoria.La técnica más empleada consiste en empaquetar la información en bloques o registros a los que se aña<strong>de</strong> unacabecera, que, entre otras cosas, incluye una i<strong>de</strong>ntificación <strong>de</strong>l bloque o registro.La unidad <strong>de</strong> control <strong>de</strong>l dispositivo <strong>de</strong>berá interpretar este i<strong>de</strong>ntificador para po<strong>de</strong>r seleccionar la posición <strong>de</strong>memoria requerida. Generalmente, estas memorias se usan para seleccionar bloques enteros y no posicionesindividualizadas. Esto significa que la lectura y escritura se hacen a nivel <strong>de</strong> bloque y no <strong>de</strong> palabra.A<strong>de</strong>más, dado que el medio o soporte es continuo, es necesario disponer <strong>de</strong> una señal <strong>de</strong> reloj que permitadiferenciar los puntos <strong>de</strong> memoria consecutivos. Esta señal <strong>de</strong> reloj pue<strong>de</strong> ser externa, pero suele grabarse en elmedio para evitar problemas <strong>de</strong> sincronización.Obsérvese que, a la menor diferencia entre el reloj y la velocidad a la que el medio pasa por <strong>de</strong>lante <strong>de</strong>ltransductor, producirá una interpretación errónea <strong>de</strong> la información, al haberse perdido la sincronización. Si laseñal <strong>de</strong> reloj está grabada, las variaciones <strong>de</strong> velocidad producen una variación idéntica en el reloj, por lo que nose pier<strong>de</strong> el sincronismo.Lo mismo ocurre en las memorias <strong>de</strong> propagación don<strong>de</strong> la velocidad <strong>de</strong> movimiento <strong>de</strong> la información <strong>de</strong>be estarsincronizada con el reloj.Finalmente, se establecen las diferencias entre los dispositivos <strong>de</strong> acceso secuencial, frente a los <strong>de</strong> acceso odireccionamiento directo.En los primeros sólo existe un transductor, por lo que, para acce<strong>de</strong>r a una posición, se <strong>de</strong>be recorrer todo elmedio hasta alcanzar la posición <strong>de</strong>seada. Esto suce<strong>de</strong> con la cinta magnética.En los dispositivos <strong>de</strong> acceso directo hay varios transductores colocados en diversas posiciones, <strong>de</strong> forma que sepue<strong>de</strong> pasar <strong>de</strong> una posición a otra seleccionando el transductor a<strong>de</strong>cuado. Dentro <strong>de</strong> la zona asignada a cadatransductor, el funcionamiento sigue siendo <strong>de</strong> tipo secuencial, pero, al ser menor esta zona, el tiempo perdido enesperar que la posición <strong>de</strong>seada alcance el transductor, es menor que si todo el dispositivo fuese <strong>de</strong> accesosecuencial.Ejemplos <strong>de</strong> memorias dinámicas <strong>de</strong> acceso directo son los discos y los tambores, y <strong>de</strong> memoria <strong>de</strong> propagación<strong>de</strong> acceso directo, las memorias <strong>de</strong> burbujas magnéticas.ETSII – Dpto. Tecnología Electrónica Página: 18 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASCapitulo <strong>2.</strong>8.- CARACTERISTICAS DE LAS MEMORIASSe ofrece un estudio <strong>de</strong>tallado <strong>de</strong> las 4 características que mejor <strong>de</strong>finen y diferencian a los diferentes tipos <strong>de</strong>memorias:- Duración <strong>de</strong> la información.- Modo <strong>de</strong> acceso.- Velocidad.- Capacidad o tamaño.También existen otras propieda<strong>de</strong>s secundarias que, frecuentemente, se <strong>de</strong>ben tener en cuenta como son lapotencia o consumo, el coste, la <strong>de</strong>nsidad <strong>de</strong> bits y las recomendaciones <strong>de</strong> uso, entre otras.Duración <strong>de</strong> la informaciónEn relación con la permanencia <strong>de</strong> la información grabada en las memorias, hay 4 posibilida<strong>de</strong>s:Memorias permanentesSon las que contienen siempre la misma información y no pue<strong>de</strong>n borrarse.La información pue<strong>de</strong> haberse grabado en el proceso <strong>de</strong> fabricación <strong>de</strong> la memoria o pue<strong>de</strong> haberse efectuadoposteriormente en un proceso <strong>de</strong> grabado <strong>de</strong>structivo o permanente.Como ejemplos <strong>de</strong> este tipo <strong>de</strong> memorias se pue<strong>de</strong>n citar las tarjetas y cintas <strong>de</strong> papel perforado y las memorias<strong>de</strong> semiconductores tipo ROM.En contraposición a este tipo <strong>de</strong> memorias <strong>de</strong> sólo lectura, están las <strong>de</strong> lecturaescritura, que pue<strong>de</strong>n grabarsecuantas veces se quiera. Como alternativa intermedia están las memorias que, para borrarse, precisan <strong>de</strong> uncomplejo proceso especial, como las <strong>de</strong> tipo EPROM.Memorias volátiles.Precisan estar continuamente alimentadas <strong>de</strong> energía.Si se corta dicho suministro se borra la información que poseen.En contraposición, están las memorias no volátiles, en las que permanece la información aunque se elimine laalimentación.Memorias <strong>de</strong> lectura <strong>de</strong>structivaSon memorias cuya lectura implica el borrado <strong>de</strong> la información.Para que la información no <strong>de</strong>saparezca, se requiere una escritura, posterior a la lectura, que vuelva a grabar loque se ha leído.El ejemplo clásico <strong>de</strong> este tipo <strong>de</strong> memorias es el <strong>de</strong> ferritas.Entre las memorias <strong>de</strong> lectura no <strong>de</strong>structiva <strong>de</strong>stacan las <strong>de</strong> semiconductores, discos y banda magnética.Memorias con refrescoLa información sólo dura un cierto tiempo.Para que la información no <strong>de</strong>saparezca, hay que re-grabar la información <strong>de</strong> forma periódica (refresco).ETSII – Dpto. Tecnología Electrónica Página: 19 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASModo <strong>de</strong> accesoEl modo <strong>de</strong> acceso <strong>de</strong> las memorias pue<strong>de</strong> ser por palabras o por bloques.En el primer caso, en cada operación <strong>de</strong> lectura o escritura se transmite una sola palabra.En el segundo, cada operación implica un bloque completo <strong>de</strong> información.El acceso por palabra, llamado acceso aleatorio, solamente se emplea en las memorias estáticas, en las que eltiempo para direccionar cualquier punto <strong>de</strong> memoria siempre es el mismo. Por este motivo se suelen <strong>de</strong>nominar alas memorias estáticas, memorias <strong>de</strong> acceso aleatorio o <strong>de</strong> tipo RAM (Random Access Memory).El acceso por bloques se utiliza en memorias dinámicas y <strong>de</strong> propagación.Este acceso tiene su justificación en que estas memorias tardan bastante en alcanzar el punto don<strong>de</strong> estáalmacenado el primer dato <strong>de</strong> un bloque, pero tardan muy poco en acce<strong>de</strong>r a los siguientes. Para obtener un buenrendimiento <strong>de</strong>l dispositivo, conviene acce<strong>de</strong>r en bloques <strong>de</strong> un tamaño <strong>de</strong>terminado, que justifiquen el tiempoperdido en el acceso a la zona <strong>de</strong>l bloque.Los computadores actuales disponen <strong>de</strong> una memoria principal <strong>de</strong> acceso aleatorio y una memoria secundaria <strong>de</strong>acceso por bloques.VelocidadEn términos generales, la velocidad <strong>de</strong> la memoria será el "tiempo que tar<strong>de</strong> en realizar una operación <strong>de</strong> lecturao escritura". Debido a las peculiarida<strong>de</strong>s <strong>de</strong> las memorias, la cuantificación <strong>de</strong> este concepto requiere analizar lostiempos <strong>de</strong> las distintas fases <strong>de</strong> las operaciones <strong>de</strong> lectura y escritura.Se analizan en principio las memorias estáticas o <strong>de</strong> direccionamiento cableado. En ellas, dado que todos lospuntos <strong>de</strong> almacenamiento están cableados <strong>de</strong> forma equivalente, los tiempos son in<strong>de</strong>pendientes <strong>de</strong> la dirección.El tiempo <strong>de</strong> acceso o tiempo <strong>de</strong> lectura, ta, es el tiempo que tarda la memoria en suministrar una palabra<strong>de</strong>s<strong>de</strong> el momento en que se proporciona la dirección y la señal <strong>de</strong> lectura.El tiempo <strong>de</strong> escritura, te, es el tiempo que tarda la memoria en grabar información <strong>de</strong>s<strong>de</strong> el momento enque se suministra la dirección, la información y la señal <strong>de</strong> escritura.En las memorias dinámicas y <strong>de</strong> propagación hay que consi<strong>de</strong>rar el tiempo que se tarda en hacer coincidir eltransductor con la información y la velocidad a que se escriben o leen palabras consecutivas,En las memorias dinámicas se llama "tiempo <strong>de</strong> acceso" al tiempo que tarda el transductor móvil enalcanzar la posición <strong>de</strong>seada más el tiempo que tarda la zona buscada <strong>de</strong>l medio en llegar a estar frenteal transductor.Para las memorias <strong>de</strong> propagación, es el tiempo que tarda la información buscada en pasar frente altransductor.En ambos casos, una vez accedida la zona <strong>de</strong>seada, pue<strong>de</strong>n escribirse o leerse una serie <strong>de</strong> palabras a altavelocidad. Se hace referencia a la velocidad o ca<strong>de</strong>ncia <strong>de</strong> transferencia y se expresa en bytes/s, Kbytes/s oMbytes/s. Esta ca<strong>de</strong>ncia está <strong>de</strong>terminada por la velocidad <strong>de</strong>l soporte, así como por el espacio ocupado por cadapunto <strong>de</strong> memoria (<strong>de</strong>nsidad <strong>de</strong> grabación).ETSII – Dpto. Tecnología Electrónica Página: 20 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASCapacidad o tamañoSe <strong>de</strong>nomina "capacidad" o "tamaño" a la cantidad <strong>de</strong> información que pue<strong>de</strong> almacenar una memoria.La capacidad se pue<strong>de</strong> expresar en unida<strong>de</strong>s <strong>de</strong> bits, bytes o palabras, aunque lo más corriente es hacerlo enbytes.Se emplean los prefijos: Kilo = K = 2 10 = 1024 , M = Mega =1024 K, G = Giga = 1024 M, T = Tera = 1024 G.En las memorias <strong>de</strong> direccionamiento cableado existe una relación directa entre los bits necesarios para llevar acabo el direccionamiento y la capacidad. En efecto, si la memoria tiene H bytes y se acce<strong>de</strong> a nivel <strong>de</strong> byte,significa que se necesitan H direcciones distintas, luego se requerirán m bits <strong>de</strong> dirección, <strong>de</strong> forma que 2 m ≥ H .Como las memorias dinámicas y <strong>de</strong> propagación almacenan, a<strong>de</strong>más <strong>de</strong> los datos, información <strong>de</strong>direccionamiento y reloj, hay que distinguir entre capacidad neta o útil, que es la capacidad <strong>de</strong> almacenamiento <strong>de</strong>información <strong>de</strong> usuario y la capacidad bruta, que se halla sumando a la neta, la <strong>de</strong> direccionamiento y reloj.La capacidad bruta <strong>de</strong> una memoria dinámica viene dada por el tamaño <strong>de</strong>l soporte y por la <strong>de</strong>nsidad <strong>de</strong>grabación. El tamaño se pue<strong>de</strong> expresar como la longitud total <strong>de</strong> pista utilizada y la <strong>de</strong>nsidad <strong>de</strong> grabación vienedada por la longitud <strong>de</strong> pista necesaria para grabar un punto <strong>de</strong> memoria.Algunas memorias dinámicas están hechas <strong>de</strong> forma tal, que el soporte es intercambiable.Capitulo <strong>2.</strong>9. - TIPOS DE DISPOSITIVOS DE ALMACENAMIENTO PARA MEMORIAPRINCIPALETSII – Dpto. Tecnología Electrónica Página: 21 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASSe pasa a realizar una revisión <strong>de</strong> los distintos dispositivos <strong>de</strong> almacenamiento más usados en la memoriaprincipal:- Memorias <strong>de</strong> ferritas.- Memorias <strong>de</strong> película <strong>de</strong>lgada e hilo plateado.- Memorias <strong>de</strong> semiconductores.- Tambor <strong>de</strong> silicio.En la tabla se ofrece una clasificación, más <strong>de</strong>tallada, <strong>de</strong> las memorias <strong>de</strong> tipo "electrónico" o <strong>de</strong> semiconductores.La <strong>de</strong>scripción <strong>de</strong> una memoria estática, funcionando en conmutación electrónica, compren<strong>de</strong> dos partes:‣ el funcionamiento <strong>de</strong>l punto <strong>de</strong> memoria y‣ la organización general <strong>de</strong> la memoria, esencialmente ligada a la técnica <strong>de</strong> selección.Si la primera parte <strong>de</strong> esta <strong>de</strong>scripción, funcionamiento <strong>de</strong>l punto <strong>de</strong> memoria, es evi<strong>de</strong>ntemente específica <strong>de</strong>cada clase <strong>de</strong> memoria, la segunda, organización y forma <strong>de</strong> selección, sería igualmente válida para otras clases<strong>de</strong> memoria, como pudieran ser las <strong>de</strong> semiconductores.MEMORIA DE FERRITAAunque hoy en día están en <strong>de</strong>suso, la práctica totalidad <strong>de</strong> las memorias principales, <strong>de</strong>s<strong>de</strong> mediados <strong>de</strong> ladécada <strong>de</strong> los 50, hasta los años 70, se han construido con ferritas. Una muestra <strong>de</strong> la importancia <strong>de</strong> estedispositivo histórico es que el escudo <strong>de</strong> las Faculta<strong>de</strong>s y Escuelas <strong>de</strong> Informática se basa en un toro <strong>de</strong> ferrita.Funcionamiento <strong>de</strong>l núcleoLas memorias <strong>de</strong> núcleos utilizan núcleos toroidales <strong>de</strong> ferrita (toro o anillo <strong>de</strong> ferrita, material ferromagnético)como punto <strong>de</strong> memoria. Las primeras ferritas tenían un diámetro exterior <strong>de</strong> 0,3 cm y las últimas <strong>de</strong> 0,05 cm.El punto <strong>de</strong> memoria presenta dos direcciones <strong>de</strong> magnetización.Cuando una corriente eléctrica <strong>de</strong> intensidad suficiente” I” atraviesa el núcleo (4a), éste se imanta en el sentidodado por la regla <strong>de</strong>l sacacorchos <strong>de</strong> MaxweIl (punto A <strong>de</strong>l ciclo <strong>de</strong> histéresis) y permanece imantado, incluso enausencia <strong>de</strong> corriente (punto A1 <strong>de</strong>l ciclo).Si se envía un impulso ” - I”, el núcleo se imantará en el otro sentido (punto B, <strong>de</strong>spués retorno al punto B1).Se suele llamar basculamiento <strong>de</strong>l núcleo a esta inversión <strong>de</strong>l sentido <strong>de</strong> su imantación.ETSII – Dpto. Tecnología Electrónica Página: 22 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASPor consiguiente, el núcleo <strong>de</strong> ferrita presenta dos estados estables A1 y B1 y pue<strong>de</strong> servir como elemento <strong>de</strong>memoria. Por convenio, diremos que el núcleo está en el estado 1 en el punto A1 y en el estado 0 en el punto B1.Obsérvese que el núcleo permanecerá en su estado mientras no se vea atravesado por corrientes <strong>de</strong> intensidadsuperior a J, en valor absoluto. En particular, una corriente <strong>de</strong> valor I/2 no es capaz <strong>de</strong> hacerlo bascular.Sabemos ya realizar la operación <strong>de</strong> escritura <strong>de</strong> un dígito sobre el toro: se escribe el dígito 1 enviando un impulso+ 1 y el dígito 0 enviando un impulso - 1.La información contenida en el núcleo pue<strong>de</strong> leerse empleando las leyes <strong>de</strong> la inducción magnética: al bascular elnúcleo, la variación producida <strong>de</strong>l campo magnético induce una corriente en un hilo <strong>de</strong> lectura que lo atraviesa. Siel núcleo estaba en 1 (4b), la corriente ” - I”, por el hilo F1 lo hace bascular y se recupera una corriente inducidaen el hilo F<strong>2.</strong>Si el núcleo estaba en 0, no pasa nada.Por tanto, la presencia <strong>de</strong> un impulso en el hilo F2 <strong>de</strong> lectura es indicativa <strong>de</strong>l contenido <strong>de</strong>l núcleo pero nóteseque esta lectura es <strong>de</strong>structiva ya que, al final <strong>de</strong> la operación, el núcleo queda en el estado 0.Organización <strong>de</strong> las memorias <strong>de</strong> núcleosLa conexión a los transductores se realiza mediante hilos <strong>de</strong> cobre barnizados, que pasan por el interior <strong>de</strong> lasferritas. Esta parte <strong>de</strong>l proceso <strong>de</strong> fabricación consistía en "coser" las ferritas y se hacía a mano. Era fácil que, alcoserlas, hubiera roturas <strong>de</strong> ferritas, lo que obligaba a difíciles reparaciones.La conexión se hacía con 2, 3 ó 4 hilos.Se distinguen tres tipos <strong>de</strong> selección, que correspon<strong>de</strong>n a distintas organizaciones <strong>de</strong> las memorias:‣ la selección lineal o selección en dos dimensiones (2D);‣ las selecciones por coinci<strong>de</strong>ncia <strong>de</strong> corrientes, que compren<strong>de</strong>n la selección en tres dimensiones (3D) y‣ la selección en dos dimensiones y media (2 1/2 D).Organización por palabras (u organización 2D)La memoria más sencilla consiste en una matriz <strong>de</strong> núcleos, cada uno <strong>de</strong> ellos atravesado por dos hilosperpendiculares, un hilo <strong>de</strong> palabra y un hilo <strong>de</strong> bit. Los núcleos <strong>de</strong> una misma fila memorizan una palabra.Se dice que una memoria así concebida está organizada por palabras y que su selección es lineal o en dosdimensiones (2D).ETSII – Dpto. Tecnología Electrónica Página: 23 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASPara escribir una <strong>de</strong>terminada configuración binaria en una palabra <strong>de</strong> la memoria (supuesta previamente a cero)se envía una corriente I/2 por el hilo <strong>de</strong> palabra correspondiente y una corriente I/2 por todos los hilos <strong>de</strong> bit, a losque les corresponda un 1 en la configuración binaria. (4c).Únicamente los núcleos que se vean atravesados simultáneamente por las dos corrientes bascularán, puesto quela corriente I/2 por sí sola es incapaz <strong>de</strong> provocar el basculamiento <strong>de</strong> un núcleo.La operación <strong>de</strong> lectura <strong>de</strong> una palabra consiste en enviar una corriente - I por el hilo <strong>de</strong> palabra: los núcleos <strong>de</strong>esta palabra que estuvieran a 1 basculan y se recupera una corriente inducida en los correspondientes hilos <strong>de</strong>bits.Se observa que la lectura es <strong>de</strong>structiva, puesto que pone a cero a todos los bits <strong>de</strong> la palabra, y la escritura exigeuna puesta a cero previa.Entonces, se conviene en dividir toda operación concerniente a la memoria en dos fases: una fase <strong>de</strong> lectura yuna fase <strong>de</strong> escritura.En el caso <strong>de</strong> una búsqueda en memoria, la segunda fase tiene por objetivo re-escribir la palabra leída: por tanto,al nivel <strong>de</strong>l ciclo la memoria no es <strong>de</strong>structiva.En el caso <strong>de</strong> un registro en memoria, la primera fase persigue poner a cero la palabra en la que se quiere escribir(fig. 6).Se <strong>de</strong>nomina tiempo <strong>de</strong> acceso al tiempo necesario a la obtención <strong>de</strong> la información buscada, se llama ciclo <strong>de</strong>memoria al conjunto <strong>de</strong> las dos fases <strong>de</strong> lectura y <strong>de</strong> escritura.La duración <strong>de</strong>l cico <strong>de</strong> memoria es ligeramente superior al doble <strong>de</strong>l tiempo <strong>de</strong> acceso, habida cuenta <strong>de</strong> lostiempos <strong>de</strong> carga <strong>de</strong> registros.La figura 7 esquematiza la organización general <strong>de</strong> una memoria organizada por palabras, sin incluir losamplificadores para generarlas corrientes I e I/2 y para amplificar los impulsos <strong>de</strong> lectura.El registro S contiene la dirección <strong>de</strong> memoria y, por intermedio <strong>de</strong> la matriz <strong>de</strong> <strong>de</strong>codificación, pue<strong>de</strong> sensibilizarlos hilos <strong>de</strong> palabra; el registro está conectado, tanto para entradas como para salidas, a los hilos <strong>de</strong> bits.Algunas memorias poseen un registro M doble, una parte para la lectura, otra para la escritura.Selección por corrientes coinci<strong>de</strong>ntes (3D).Parte <strong>de</strong> la <strong>de</strong>codificación la realiza la propia organización <strong>de</strong> la memoria.nEsta se divi<strong>de</strong> en m matrices <strong>de</strong> 2 núcleos, don<strong>de</strong> m es el número <strong>de</strong> bits <strong>de</strong> la palabra <strong>de</strong> memoria y n elnúmero <strong>de</strong> bits <strong>de</strong>l registro <strong>de</strong> selección.Cada núcleo <strong>de</strong> la i-sima matriz correspon<strong>de</strong> al bit <strong>de</strong> peso i <strong>de</strong> una <strong>de</strong> lasn2palabras <strong>de</strong> la memoria.Cada núcleo está atravesado por cuatro hilos, dos para la selección X e Y enhebrados en serie con las m matrices<strong>de</strong> núcleos y dos hilos funcionales para lectura e inhibición, una pareja por cada matriz.ETSII – Dpto. Tecnología Electrónica Página: 24 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASSe lee una palabra enviando dos impulsos (- I/2) por los hilos X e Y a<strong>de</strong>cuados.La coinci<strong>de</strong>ncia <strong>de</strong> estos dos impulsos pone a cero a los núcleos <strong>de</strong> la palabra que estaban posicionados en 1, yeste basculamiento induce corrientes por los hilos <strong>de</strong> lectura (fig. 9).Se escriben los bits 1 <strong>de</strong> una palabra, previamente puesta a cero, enviando corrientes I/2 por los hilos X e Y que laseleccionan.Escribir ceros consiste en evitar el basculamiento <strong>de</strong> los núcleos: se envía una corriente - I/2 por el hilo <strong>de</strong>inhibición, opuesta a las dos corrientes I/2 <strong>de</strong> los hilos X e Y, <strong>de</strong> tal forma que la resultante igual a I/2 esinsuficiente para provocar el basculamiento <strong>de</strong>l núcleo (fig. 10).Obsérvese que es posible utilizar el mismo hilo para lectura e inhibición, la figura muestra la conexión con 3 hilos.ETSII – Dpto. Tecnología Electrónica Página: 25 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASSelección 2 ½D.Es también una selección por corrientes coinci<strong>de</strong>ntes, con la única diferencia respecto a la selección 3D que lainhibición en escritura no se sitúa al nivel <strong>de</strong> los núcleos, sino al <strong>de</strong> las corrientes <strong>de</strong> selección (fig. 11)El direccionamiento era, generalmente, 2D1/<strong>2.</strong>Evi<strong>de</strong>ntemente, el cosido con menos hilos era más sencillo, pero complicaba los transductores.Comparación entre los distintos tipos <strong>de</strong> selección.El paso <strong>de</strong> la organización 2D a una <strong>de</strong> las organizaciones 3D ó 2 ½ D se caracteriza:1. por una ganancia en lo que concierne a los circuitos <strong>de</strong> <strong>de</strong>codificación: se va <strong>de</strong> una <strong>de</strong>codificación sobren bits a dos <strong>de</strong>codificaciones sobre n/2 bits.Ahora bien, la complejidad <strong>de</strong>l circuito <strong>de</strong> <strong>de</strong>codificación es proporcional al cuadrado <strong>de</strong>l número <strong>de</strong> bitspor <strong>de</strong>codificar. Basta, para bien hacerse cargo <strong>de</strong> este factor, hacer el cálculo <strong>de</strong> la ganancia en unapequeña memoria <strong>de</strong> 4 K palabras;<strong>2.</strong> por una pérdida, si se cuantifica el cableado <strong>de</strong> los núcleos: en efecto, es necesario enhebrar un hilosuplementario por cada núcleo.La importancia <strong>de</strong> este factor se apreciará mejor si se sabe, por un lado, que siendo la velocidad <strong>de</strong>basculamiento <strong>de</strong> un núcleo tanto mayor cuanto menor es su diámetro, se está obligado a usar núcleoscon diámetros <strong>de</strong>l or<strong>de</strong>n <strong>de</strong> una fracción <strong>de</strong> milímetro y, por otro lado, que las matrices <strong>de</strong> núcleos suelenenhebrarse a mano, <strong>de</strong>bido a la fragilidad <strong>de</strong> los núcleos <strong>de</strong> ferrita y a la dificultad <strong>de</strong> poner a puntodispositivos <strong>de</strong> enhebramiento automático.La solución escogida para el cableado <strong>de</strong> una memoria se situará evi<strong>de</strong>ntemente en una zona <strong>de</strong> equilibrio entreestos dos factores. De manera general, se optará por las memorias 2 D cuando la relación coste <strong>de</strong>l cableado <strong>de</strong>los núcleos a coste <strong>de</strong>l circuito <strong>de</strong> <strong>de</strong>codificación sea importante, como es el caso:- para pequeñas memorias muy rápidas, don<strong>de</strong> sería inaceptable una solución <strong>de</strong> 3 hilos por núcleo.- para las memorias auxiliares, don<strong>de</strong> la operación <strong>de</strong> selección afecta a palabras muy largas (<strong>de</strong> varioscientos <strong>de</strong> bits).Resumen <strong>de</strong> las propieda<strong>de</strong>s fundamentales <strong>de</strong> estas memorias son las siguientes:a) Memoria estática con direccionamiento cableado, tipo RAM.b) No volátil, pues, si se <strong>de</strong>ja <strong>de</strong> alimentar, las polarizaciones <strong>de</strong> las ferritas se mantienen invariables.c) De lectura <strong>de</strong>structiva. La escritura exige un borrado previo, pues solamente se pue<strong>de</strong> pasar <strong>de</strong>l "0" a “1”.d) Sólo se consi<strong>de</strong>ra el tiempo <strong>de</strong> ciclo (lectura + escritura) pues los accesos siempre requieren un ciclo.La velocidad <strong>de</strong> los primeros prototipos era <strong>de</strong> 20 us y se ha llegado a mo<strong>de</strong>los <strong>de</strong> 275 ns.e) La capacidad <strong>de</strong> estas memorias varía <strong>de</strong> unos pocos K a unos pocos Megas.Se construían con módulos <strong>de</strong> 4 K. Valores típicos <strong>de</strong> anchos <strong>de</strong> palabra han sido 8, 16, 32 y 36 bits.ETSII – Dpto. Tecnología Electrónica Página: 26 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASMEMORIAS DE PELICULA DELGADA Y DE HILO PLATEADOAmbos tipos <strong>de</strong> memorias fueron un intento, <strong>de</strong> poco éxito comercial, <strong>de</strong> sustituir las ferritas <strong>de</strong> dos hilos por unaestructura <strong>de</strong> fabricación más sencilla, <strong>de</strong> menor tamaño y, por tanto, <strong>de</strong> mayor velocidad.En los dispositivos <strong>de</strong> película <strong>de</strong>lgada se parte <strong>de</strong> una fina capa magnetizable sobre la que se establece unamatriz <strong>de</strong> hilos conectados a los transductores.La zona próxima al cruce <strong>de</strong> dos hilos realiza la misma función que un toro <strong>de</strong> ferrita <strong>de</strong> dos hilos.Dicha capa se <strong>de</strong>posita sobre un soporte y tiene un espesor <strong>de</strong> unos 1.000 A = 10 mm.En los dispositivos <strong>de</strong> hilo plateado el material magnético se <strong>de</strong>posita en una fina capa que recubre uno <strong>de</strong> los dosconductores.La zona <strong>de</strong> este <strong>de</strong>pósito, próxima al cruce <strong>de</strong> ambos hilos, forma el equivalente a la ferrita.−4ETSII – Dpto. Tecnología Electrónica Página: 27 / 54 MSA

Sistemas <strong>de</strong> MultiprocesamientoMEMORIASMEMORIAS DE SEMICONDUCTORESEste tipo <strong>de</strong> memoria se emplea actualmente, con carácter universal, como memoria principal <strong>de</strong> loscomputadores.En referencia a los aspectos operativos <strong>de</strong> estas memorias: utilizan el biestable electrónico como punto <strong>de</strong>memoria, se presentan una organización celular cada punto <strong>de</strong> memoria constituido por su biestable y loscircuitos asociados <strong>de</strong> lectura y <strong>de</strong> escritura.Este tipo <strong>de</strong> memoria emplea los mismos modos <strong>de</strong> selección que hemos <strong>de</strong>scrito en las memorias <strong>de</strong> núcleos.La figura (a) representa un punto <strong>de</strong> memoria en el caso <strong>de</strong> la selección lineal 2D.En escritura, la señal <strong>de</strong> escritura <strong>de</strong> palabra muestrea la información latente en el hilo <strong>de</strong> bit; en lectura, la señal<strong>de</strong> lectura <strong>de</strong> palabra permite analizar el contenido <strong>de</strong>l biestable.Este esquema da una lectura no <strong>de</strong>structiva y una escritura que no exige puesta a cero previa.La figura (b) presenta una posible realización <strong>de</strong>l punto <strong>de</strong> memoria bajo la hipótesis <strong>de</strong> selección por corrientescoinci<strong>de</strong>ntes <strong>de</strong>l tipo 3 D.Los dos hilos <strong>de</strong> selección X e Y permiten direccionar el punto <strong>de</strong> memoria, lo mismo en lectura que en escritura.Escribir 1 y escribir 0 exigen dos señales diferentes, si se quiere que la lectura no sea <strong>de</strong>structiva.Todas las memorias que se van a tratar en este apartado son <strong>de</strong> direccionamiento cableado, o sea, <strong>de</strong> accesoaleatorio o RAM. Sin embargo, <strong>de</strong>ntro <strong>de</strong> estas memorias se ha <strong>de</strong>sarrollado otra terminología que resulta un pococonfusa, pues repite términos empleados con otro sentido. Se pue<strong>de</strong> establecer la siguiente clasificación:a) De lectura y escritura (RAM)- Estáticas.- Dinámicas o con refresco.b) De sólo lectura- ROM (Read Only Memory).- PROM (Programmable Read Only Memory).- EPROM (Erasable Programmable Read Only Memory).- EEROM (Electricaly Erasable Read On1y Memory).Las memorias <strong>de</strong> semiconductores se presentan en pastillas integradas que contienen una matriz <strong>de</strong> memoria, un<strong>de</strong>codificador <strong>de</strong> direcciones, los transductores correspondientes y el tratamiento lógico <strong>de</strong> algunas señales <strong>de</strong>control.ETSII – Dpto. Tecnología Electrónica Página: 28 / 54 MSA