MIA-Unidad 3 (.pdf)

MIA-Unidad 3 (.pdf)

MIA-Unidad 3 (.pdf)

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

UNIDAD 3<br />

Interfaz de E/S Básica, Interrupciones y E/S Controlada por DMA<br />

Por muy poderosa que sea una unidad central de procesamiento (CPU), la utilidad<br />

de una computadora depende esencialmente de sus capacidades de entrada y<br />

salida. Es decir sin ellas, no habría por ejemplo entrada desde el teclado, ni salida<br />

desde la pantalla, ni salida impresa y ni siquiera almacenamiento y recuperación en<br />

disco. Para ello se requiere utilizar rutinas y medios especializados que permitan<br />

procesar la entrada y la salida.<br />

Motivado a esto, se presenta en esta unidad el estudio de los componentes de E/S<br />

y sus interfaces, específicamente con el microprocesador. Posteriormente se<br />

introducen dos técnicas avanzadas de E/S, las interrupciones y acceso directo a<br />

memoria, además de los componentes y las configuraciones que las hacen<br />

posibles.<br />

Objetivo de la <strong>Unidad</strong> 3: Resolver problemas de atención a los dispositivos de E/S,<br />

haciendo uso de interfases básicas programables y/o por interrupción y/o<br />

controladas por DMA.<br />

Contenido de la <strong>Unidad</strong> 3: El contenido de la unidad contempla el estudio de los<br />

siguientes temas:<br />

Interfaz básica de E/S.<br />

Interrupciones.<br />

Acceso directo a la memoria.<br />

E/S controlada por DMA.<br />

38

Actividades recomendadas para el estudio del contenido de la unidad 3.<br />

1.- Examine la tabla 3.1, en ella puede identificar las lecturas de los temas<br />

contentivos de la unidad 3:<br />

TÍTULO<br />

La interfaz de<br />

entrada/salida<br />

básica.<br />

Interrupciones.<br />

Acceso directo a<br />

memoria y E/S<br />

controlada por<br />

DMA.<br />

MATERIAL DE<br />

REFERENCIA<br />

El texto Los<br />

Microprocesadores<br />

Intel, B. B. Brey.<br />

El texto Los<br />

Microprocesadores<br />

Intel, B. B. Brey.<br />

El texto Los<br />

Microprocesadores<br />

CONTENIDO<br />

Introducción a la interfaz de<br />

E/S.<br />

Decodificación de dirección<br />

de un puerto de E/S.<br />

La interfaz periférica<br />

programable.<br />

La interfaz programable de<br />

teclado/pantalla tipo 8279.<br />

Procesamiento básico de<br />

interrupciones.<br />

Interrupciones por hardware.<br />

Expansión de la estructura de<br />

interrupciones..<br />

Controlador de interrupción<br />

programable 8259A .<br />

Ejemplos de interrupción.<br />

Operación básica del DMA y<br />

el controlador del DMA 8237.<br />

Intel, B. B. Brey. Operación del bus<br />

compartido.<br />

Tabla 3.1<br />

CAPITUL<br />

O<br />

11<br />

12<br />

13<br />

39

a) Ampliación de conocimientos: El contenido Interfaz programable de<br />

comunicaciones 16550, incluido en el capítulo 11 sección 11-6, del texto Los<br />

Microprocesadores Intel, no es objeto de evaluación del curso<br />

Microprocesadores, sin embargo, se recomienda su lectura, ya que ésta es<br />

utilizada para conectarse prácticamente a cualquier tipo de interfaz serial.<br />

Atención: Para el establecimiento de una interfaz se requieren ciertos<br />

conocimientos de electrónica, el texto del curso examina algunos hechos<br />

relacionados con ella, los cuales se recomienda leer, a objeto de obtener una<br />

mejor comprensión del contenido.<br />

2.- Lea los siguientes aspectos teóricos, a través de los cuales reforzará los<br />

conocimientos adquiridos.<br />

Buffer de tres estados (o buffer triestado).<br />

Un dispositivo lógico semiconductor que puede tener tres estados: (1) un estado<br />

lógico 0, (2) un estado lógico 1 y (3) un estado en el que la salida está,<br />

efectivamente, desconectada del resto del circuito y no tiene influencia sobre él.<br />

[Lameda,1984].<br />

Tecnología TTL<br />

Acrónimo en Inglés de Transistor-Transistor Logic o "Lógica Transistor a<br />

Transistor". Tecnología de construcción de circuitos electrónicos digitales, en los<br />

que los elementos de entrada de la red lógica son transistores, así como los<br />

elementos de salida del dispositivo.<br />

Las características de la tecnología utilizada, en la familia TTL, condiciona los<br />

parámetros que se describen en sus hojas de características según el fabricante:<br />

Su tensión de alimentación característica se halla comprendida entre los 4.75 V<br />

y los 5.25 V como se ve un rango muy estrecho debido a esto, los niveles<br />

lógicos vienen definidos por el rango de tensión comprendida entre 0.2 V y 0.8 V<br />

para el estado L (bajo) y los 2.4 V y Vcc para el estado H (alto).<br />

La velocidad de transmisión entre los estados lógicos es su mejor baza,<br />

ciertamente esta característica le hacer aumentar su consumo siendo su mayor<br />

enemigo. Motivo por el cual han aparecido diferentes versiones de TTL como<br />

FAST, LS, S, etc y últimamente los TTL: HC, HCT y HCTLS. En algunos casos<br />

puede alcanzar poco más de los 250 Mhz.<br />

[http://es.wikipedia.org/wiki/Tecnolog%C3%ADa_TTL].<br />

Nota: Vcc es el nivel de 5 V (voltios).<br />

40

LED (siglas en inglés de Diodo Emisor de Luz).<br />

Semiconductor especial que emite luz, cuando lo recorre una corriente eléctrica.<br />

[Sayers 1995].<br />

Interfaces con el microprocesador.<br />

La mayoría de los microprocesadores tiene poco valor funcional por si mismos.<br />

Muchos no contienen una memoria sustancial, y pocos tienen puertos de<br />

entrada y salida que los conecten directamente a dispositivos periféricos. Los<br />

microprocesadores operan como parte de un sistema. La interconexión, o<br />

enlace, de las partes en este sistema se denomina interfaz. [Tokheim, 1995].<br />

E/S asignada a memoria y E/S aislada.<br />

Cuando el procesador, la memoria principal y la E/S comparten un bus común,<br />

son posibles dos modos de direccionamiento: asignado en memoria (memorymapped)<br />

y aislado. Con las E/S asignadas a memoria, existe un único espacio<br />

de direcciones para las posiciones de memoria y los dispositivos de E/S. La CPU<br />

considera los registros de estado y de datos de los módulos de E/S como<br />

posiciones de memoria, y utiliza las mismas instrucciones máquina para acceder<br />

tanto a la memoria como a los dispositivos de E/S. Así por ejemplo, con 10<br />

líneas de dirección se puede acceder a un total de 1024 posiciones de memoria<br />

y direcciones de E/S, en cualquier combinación.<br />

Con la E/S asignadas en memoria, se necesita una sola línea de lectura y una<br />

sola línea de escritura en el bus. Alternativamente, el bus puede disponer de<br />

líneas de lectura y escritura en memoria junto con líneas para órdenes de<br />

entrada y salida. En este caso, las líneas de órdenes especifican si la dirección<br />

se refiere a una posición de memoria o a un dispositivo de E/S. El rango<br />

completo de direcciones está disponible para ambos. De nuevo, con 10 líneas<br />

de dirección, el sistema puede soportar ahora 1024 posiciones de memoria y<br />

1024 direcciones de E/S. Puesto que el espacio de direcciones de E/S está<br />

aislado del de memoria, éste se conoce con el nombre de E/S aislada. [Stallings,<br />

2000].<br />

Protocolo con respuesta (Handshaking)<br />

Un típico sistema de comunicación en paralelo puede ser de una dirección<br />

(unidireccional) o de dos direcciones (bidireccional). El más simple mecanismo<br />

utilizado en un puerto paralelo de una PC es de tipo unidireccional y es el que<br />

analizaremos en primer lugar. Distinguimos dos elementos: la parte transmisora<br />

y la parte receptora. La parte transmisora coloca la información en las líneas de<br />

datos e informa a la parte receptora que la información (los datos) están<br />

disponibles; entonces la parte receptora lee la información en las líneas de datos<br />

e informa a la parte transmisora que ha tomado la información (los datos).<br />

Observe que ambas partes sincronizan su respectivo acceso a las líneas de<br />

41

datos, la parte receptora no leerá las líneas de datos hasta que la parte<br />

transmisora se lo indique en tanto que la parte transmisora no colocará nueva<br />

información en las líneas de datos hasta que la parte receptora remueva la<br />

información y le indique a la parte transmisora que ya ha tomado los datos, a<br />

ésta coordinación de operaciones se le llama acuerdo ó entendimiento. Bien, en<br />

éstos ámbitos tecnológicos es recomendable utilizar ciertas palabras en inglés<br />

que nos permiten irónicamente un mejor entendimiento de los conceptos<br />

tratados. Repito: a la coordinación de operaciones entre la parte transmisora y la<br />

parte receptora se le llama handshaking, que en español es el acto con el cual<br />

dos partes manifiestan estar de acuerdo, es decir, se dan un apretón de manos.<br />

El handshaking<br />

Para implementar el handshaking se requieren dos líneas adicionales. La línea<br />

de estroboscopio (en inglés strobe) es la que utiliza la parte transmisora para<br />

indicarle a la parte receptora la disponibilidad de información. La línea de<br />

admisión (acknowledge) es la que utiliza la parte receptora para indicarle a la<br />

parte transmisora que ha tomado la información (los datos) y que está lista para<br />

recibir más datos. El puerto paralelo provee de una tercera línea de handshaking<br />

llamada en inglés busy (ocupado), ésta la puede utilizar la parte receptora para<br />

indicarle a la parte transmisora que está ocupada y por lo tanto la parte<br />

transmisora no debe intentar colocar nueva información en las líneas de datos.<br />

Una típica sesión de transmisión de datos se parece a lo siguiente:<br />

Parte transmisora:<br />

� La parte transmisora chequea la línea busy para ver si la parte receptora está<br />

ocupada. Si la línea busy está activa, la parte transmisora espera en un bucle<br />

hasta que la línea busy esté inactiva.<br />

� La parte transmisora coloca la información en las líneas de datos.<br />

� La parte transmisora activa la línea de strobe.<br />

� La parte transmisora espera en un bucle hasta que la línea acknowledge está<br />

activa.<br />

� La parte transmisora inactiva la línea de strobe.<br />

� La parte transmisora espera en un bucle hasta que la línea acknowledge esté<br />

inactiva.<br />

� La parte transmisora repite los pasos anteriores por cada byte a ser<br />

transmitido.<br />

Parte receptora:<br />

� La parte receptora inactiva la línea busy (asumiendo que está lista para<br />

recibir información).<br />

� La parte receptora espera en un bucle hasta que la línea strobe esté activa.<br />

� La parte receptora lee la información de las líneas de datos (y si es<br />

necesario, procesa los datos).<br />

� La parte receptora activa la línea acknowledge.<br />

o La parte receptora espera en un bucle hasta que esté inactiva la línea<br />

de strobe.<br />

� La parte receptora inactiva la línea acknowledge.<br />

� La parte receptora repite los pasos anteriores por cada byte que debe recibir.<br />

42

Se debe ser muy cuidadoso al seguir éstos pasos, tanto la parte transmisora<br />

como la receptora coordinan sus acciones de tal manera que la parte<br />

transmisora no intentará colocar varios bytes en las líneas de datos, en tanto<br />

que la parte receptora no debe leer más datos que los que le envíe la parte<br />

transmisora, un byte a la vez.<br />

[http://www.modelo.edu.mx/univ/virtech/circuito/paralelo.htm].<br />

CHIP<br />

Pequeña placa o pastilla de material semiconductor usado para producir un<br />

circuito integrado. [Lameda, 1984].<br />

Tipos de interfaces<br />

La interfaz entre el periférico y el módulo de E/S debe ajustarse a la naturaleza y<br />

la forma de funcionar del periférico. Una de las principales características de la<br />

interfaz es si es serie o paralela. En una interfaz paralela, hay varias líneas que<br />

conectan el módulo de E/S y el periférico, y se transfieren varios bits<br />

simultáneamente a través del bus de datos. En una interfaz serie, hay sólo una<br />

línea para transmitir los datos, y los bits deben transmitirse uno a uno . Las<br />

interfaces paralelas se utilizan usualmente para los dispositivos de alta<br />

velocidad, como una cinta o disco. Las interfaces serie son más propias de<br />

impresoras y terminales. [Stallings, 2000].<br />

Técnica de E/S mediante interrupciones.<br />

Es aquella en la que el programa genera una orden de E/S y después continúa<br />

ejecutándose hasta que el hardware de E/S interrumpe para indicar que la<br />

operación de E/S ha concluido. [Stallings, 2000].<br />

Líneas de interrupción del microprocesador Intel 80386.<br />

El microprocesador 80386 de Intel posee una línea de petición de interrupción<br />

(INTR, Interrup request) y una sola línea de reconocimiento de interrupción<br />

(INTA, Interrup Acknowledge). [Stallings, 2000].<br />

Funcionamiento del DMA.<br />

El DMA requiere un módulo adicional en el bus del sistema. El módulo DMA (ver<br />

figura 3.1) es capaz de imitar al procesador y, de hecho, es capaz de recibir el<br />

control del sistema cedido por el procesador. Necesita dicho control para<br />

transferir datos a, y desde, memoria a través del bus del sistema. Para hacerlo,<br />

el módulo DMA debe utilizar el bus sólo cuando el procesador no lo necesita, o<br />

debe forzar al procesador a que suspenda temporalmente su funcionamiento.<br />

Ésta última técnica es la más común y se denomina robo de ciclo (cycle<br />

stealing), puesto que, en efecto, el módulo DMA roba un ciclo de bus.<br />

43

Líneas de<br />

datos<br />

Líneas de<br />

direcciones<br />

DMA REQ<br />

DMA ACK<br />

INTR<br />

Read<br />

Write<br />

Contador de<br />

datos<br />

Registro de<br />

datos<br />

Registro de<br />

dirección<br />

Lógica de<br />

control<br />

Figura 3.1. Diagrama típico de un módulo de DMA.<br />

Cuando el procesador desea leer o escribir un bloque de datos, envía a una<br />

orden al módulo de DMA, incluyendo la siguiente información:<br />

� Si se solicita una lectura o una escritura, utilizando la línea de control de<br />

lectura o escritura entre el procesador y el módulo DMA.<br />

� La dirección del dispositivo de E/S en cuestión, indicada a través de la línea<br />

de datos.<br />

� La posición inicial de memoria a partir de donde se lee o se escribe,<br />

indicada a través de las líneas de datos y almacenada por un módulo de<br />

DMA en su registro de direcciones.<br />

El número de palabras a leer o escribir, también indicando a través de las líneas de<br />

datos y almacenado en el registro de cuenta datos. Después el procesador continúa<br />

con otro trabajo. Ha delegado la operación de E/S al módulo de DMA, que se<br />

encargará de ella El módulo de DMA, transfiere el bloque completo de datos palabra<br />

a palabra, directamente desde, o hacia, la memoria, sin que tenga que pasar a<br />

través del procesador. Cuando la transferencia se ha terminado, el módulo de DMA<br />

envía una señal de interrupción al procesador. Así pues, el procesador sólo<br />

interviene al comienzo y al final de la transferencia (ver figura 3.2). [Stallings, 2000].<br />

44

Mandar orden de<br />

lectura de bloque<br />

al módulo DMA<br />

Leer el estado del<br />

módulo DMA<br />

Figura 3.2. Acceso directo a memoria<br />

CPU DMA<br />

Hacer otra cosa<br />

DMA CPU<br />

3.- Estudie el ejemplo 3.1, en cual presenta la descripción y funcionamiento de la<br />

interfaz programable de periféricos (IPP) Intel 82C55A.<br />

Ejemplo 3.1: Descripción y funcionamiento de la interfaz de periférico<br />

programable 82C55A Intel.<br />

Este tipo de interfaz se utiliza para la E/S programada y para la E/S mediante<br />

interrupciones. El 82C55A es un módulo de E/S de propósito general integrado en<br />

un solo chip y diseñado para ser usado con el procesador Intel 8086.<br />

[Stallings,2000]. La figura 3.3 muestra el diagrama general de bloques de la IPP<br />

82C55A de Intel.<br />

45

Bus de 8 8 8<br />

datos A<br />

del 8086<br />

Fuente<br />

de<br />

alimentación CA<br />

A0 CB<br />

A1<br />

Read<br />

Write<br />

Reset<br />

Chip<br />

select<br />

Buffer de Bus interno<br />

datos de 8 bits<br />

Lógica<br />

de<br />

control<br />

+ 5 V (Vdd) 4<br />

Tierra (GND)<br />

Registro<br />

de<br />

control<br />

Buffer de<br />

datos<br />

Figura 3.3 Diagrama de bloques de la IPP 82C55A de Intel.<br />

Las 24 líneas de E/S son programables por el 8086 mediante un registro de control.<br />

El 8086 puede fijar el valor del registro de control para especificar los diversos<br />

modos de operación y configuraciones. Las 24 líneas se dividen en tres grupos de 8<br />

bits (A, B, C). Cada grupo puede funcionar como un puerto de E/S de 8 bits.<br />

Además, el grupo C se subdivide en grupos de 4 bits (CA y CB), que pueden usarse<br />

conjuntamente con los puertos de E/S de A y B.<br />

El diagrama de la figura 3.3 es la interfaz interna con el bus del 8086. Ésta incluye<br />

un bus de datos bidireccional de 8 bits (D0 a D7), usado para transferir datos a y<br />

desde, los puertos de E/S, y para transferir la información al registro de control. Las<br />

dos líneas de direcciones (A0 y A1) especifican uno de los dos puertos de E/S o el<br />

registro de control. Una transferencia se producirá cuando la línea de selección de<br />

4<br />

8<br />

B<br />

46

chip (CHIP SELECT) se activa junto con la línea de lectura (READ) o escritura<br />

(WRITE). La línea RESET se utiliza para iniciar el módulo.<br />

El procesador escribe en el registro de control para seleccionar el modo de<br />

operación y para definir las señales, en su caso. En el modo 0 de operación, los tres<br />

grupos de 8 líneas externan funcionan como tres puertos de E/S de 8 bits. Cada<br />

puerto puede ser designado como de entrada o de salida. En caso contrario, los<br />

grupos A y B funcionan como puertos de E/S, y las líneas del grupo C sirven de<br />

líneas de control para A y B. Las líneas de control tiene dos funciones principales: la<br />

sincronización mediante conformidad de señales (handshaking) y la petición de<br />

interrupciones. La conformidad de un mecanismo sencillo de temporización. El<br />

emisor utiliza una línea de control como línea de datos listos (DATA READY) para<br />

indicar que hay un dato en las líneas de datos de E/S. El receptor utiliza otra línea<br />

como reconocimiento (ACKNOLEDGE), para indicar que el dato se ha leído y que<br />

las líneas de datos se pueden liberar. Se puede seginar otra línea como línea de<br />

petición de interrupción (INTERRUPT REQUEST) en el bus del sistema.<br />

4.- En el ejemplo 3.2, se presenta una aplicación de la interfaz 82C55A, para<br />

controlar un terminal con teclado y pantalla.<br />

Ejemplo 3.2: Uso de la interfaz 82C55A para controlar la conexión de un<br />

teclado y una pantalla al microprocesador.<br />

En la figura 3.4, se ilustra el uso de la interfaz programable de periféricos Intel<br />

82C55A. El teclado proporciona 8 bits de entrada, dos de estos bits, SHIFT y<br />

CONTROL, tienen un significado especial para el programa de gestión de teclado<br />

que ejecuta el procesador. Sin embargo este significado es transparente para el<br />

82C55A, que simplemente acepta los 8 bits de datos y los pone en el bus de datos<br />

del sistema. Existen dos líneas para la sincronización del teclado mediante<br />

conformidad (handshaking).<br />

La pantalla también está conectada a un puerto de datos de 8 bits. De nuevo, dos<br />

de los bits tiene un significado específico que es transparente para el 82C55A.<br />

Junto a las dos líneas para la sincronización mediante conformidad, hay dos líneas<br />

más para funciones de control adicionales.<br />

47

Petición de<br />

interrupción<br />

C3 A0<br />

A0<br />

A1<br />

A2<br />

A3<br />

A4<br />

A5<br />

A6<br />

82C55A<br />

C4<br />

C5<br />

B0<br />

B1<br />

B2<br />

B3<br />

B4<br />

B5<br />

B6<br />

B7<br />

C1<br />

C2<br />

C6<br />

C0 C7<br />

R0<br />

R1<br />

R2<br />

R3<br />

R4<br />

R5<br />

Shift (deslazamiento)<br />

Control<br />

Dato preparado<br />

Reconocimiento<br />

S0<br />

S1<br />

S2<br />

S3<br />

S4<br />

S5<br />

Backspace<br />

Borrar<br />

Dato preparado<br />

Reconocmiento<br />

Blanking<br />

Borrar línea<br />

Petición de<br />

Interrupción<br />

Figura 3.4 Interfaz teclado/pantalla en el 82C55A<br />

5.- En el ejemplo 3.3 se muestra el uso de la E/S mediante interrupciones, para leer<br />

un bloque de datos desde un dispositivo periférico y almacenarlo en la memoria.<br />

Ejemplo 3.3: E/S con interrupciones para leer un bloque de datos.<br />

En la figura 3.5 se muestra el conjunto de acciones que deben desarrollarse para<br />

procesar una E/S haciendo uso de las interrupciones. El procesador tras enviar una<br />

orden de E/S a un módulo, continúa realizando algún trabajo útil. Después, el<br />

módulo de E/S interrumpirá al procesador para solicitar su servicio cuando esté<br />

preparado para intercambiar datos con él. El procesador ejecuta entonces la<br />

transferencia de datos, y después continúa con el procesamiento previo.<br />

48

No<br />

Mandar orden de<br />

lectura al módulo de<br />

E/S<br />

Leer el estado del<br />

módulo de E/S<br />

Comprobar<br />

el estado<br />

Preparado<br />

Leer una palabra del<br />

módulo de E/S<br />

Escribir una palabra<br />

en memoria<br />

Comprobar<br />

el estado<br />

Si<br />

Instrucción siguiente<br />

CPU I/O<br />

Hacer otra cosa<br />

Interrupción<br />

E/S CPU<br />

Condición de error<br />

E/S CPU<br />

CPU Memoria<br />

Figura 3.5. Entrada de un bloque de datos mediante interrupciones.<br />

6.- En el ejemplo 3.4, se presenta una aplicación del PIC (controlador de<br />

interrupciones programable) 82C59A para conectar varios módulos de E/S con<br />

el microprocesador Intel 80386.<br />

49

Ejemplo 3.4: Uso del PIC 82C59A para gestionar la interrupción de 64<br />

módulos de E/S.<br />

En la figura 3.6 se ilustra el uso del PIC 82C59A para conectar 64 módulos de E/S.<br />

Debido a que un 82C59A sólo puede manejar hasta 8 módulos, es necesario<br />

disponer de un sistema en cascada para controlar los 64 módulos de E/S.<br />

La única responsabilidad del 82C59A es la gestión de interrupciones. Acepta la<br />

solicitud de interrupción de los dispositivos conectados a él, determina qué<br />

interrupción tiene la prioridad más alta, y se lo indica entonces al procesador<br />

activando la señal INTR. El procesador reconoce la solicitud mediante la línea INTA.<br />

Esto hace que el 82C59 sitúe el vector apropiado en el bus de datos. Entonces, el<br />

procesador puede iniciar el procesamiento de la interrupción y comunicarse<br />

directamente con el módulo de E/S para leer o escribir datos.<br />

Si se precisa controlar más de 8 módulos, se puede disponer en cascada para<br />

manejar para conectar<br />

50

Dispositivo externo 00<br />

Dispositivo externo 01<br />

Dispositivo externo 07<br />

Dispositivo externo 08<br />

Dispositivo externo 09<br />

Dispositivo externo 15<br />

Dispositivo externo 56<br />

Dispositivo externo 57<br />

Dispositivo externo 63<br />

Controlador de<br />

interrupciones<br />

82C59A esclavo<br />

IR0<br />

IR1 INT<br />

IR2<br />

IR3<br />

IR4<br />

IR5<br />

IR6<br />

IR7<br />

Controlador de Concentrador de Procesador<br />

interrupciones interrupciones 80386<br />

82C59A esclavo 82C59A maestro<br />

IR0<br />

IR1 INT<br />

IR2<br />

IR3<br />

IR4<br />

IR5<br />

IR6<br />

IR7<br />

Controlador de<br />

interrupciones<br />

82C59A esclavo<br />

IR0<br />

IR1 INT<br />

IR2<br />

IR3<br />

IR4<br />

IR5<br />

IR6<br />

IR7<br />

IR0<br />

IR1<br />

IR2 INT<br />

IR3<br />

IR4<br />

IR5<br />

IR6<br />

IR7<br />

INTR<br />

Figura 3.6. Uso del controlador de interrupciones 82C59A.<br />

Entrada de un bloque de datos mediante interrupciones.<br />

51

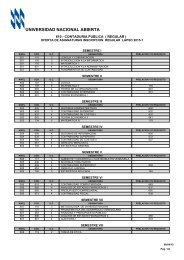

7.- En el ejemplo 3.5, se presenta una aplicación del funcionamiento de un módulo<br />

DMA, para escribir un bloque de 32 bytes de la dirección de memoria 100 en una<br />

terminal (un terminal de computadora consta de dos partes: un teclado y un<br />

monitor).<br />

Ejemplo 3.5: Transferencia de un bloque de 32 bytes desde memoria a un<br />

terminal de computadora, usando la técnica de E/S de DMA.<br />

La E/S controlada por interrupciones es un gran adelanto en comparación con la<br />

E/S programada [TANENBAUM, 2000]. El problema es que se requiere una<br />

interrupción por cada carácter transmitido. El procesamiento de interrupciones es<br />

costoso. Razón por la cual es necesario una forma de reducir la mayor parte de las<br />

interrupciones.<br />

La solución es regresar a la E/S programada, pero encargársela a otro dispositivo<br />

que no sea el CPU. La figura 3.7 muestra como se logra esto. Se ha añadido un<br />

nuevo chip al sistema, un controlador de acceso directo a la memoria (DMA), con<br />

acceso directo al bus.<br />

Dirección<br />

CPU DMA<br />

Memoria<br />

Cuenta<br />

Dispositivo<br />

100<br />

32<br />

4<br />

1<br />

Sentido<br />

Bus<br />

Figura 3.7. Sistema controlador DMA<br />

El chip DMA contiene al menos cuatro registros, todos los cuales pueden ser<br />

cargados por software que se ejecuta en la CPU. El primero contiene la dirección de<br />

memoria que se leerá o en la que se escribirá. El segundo contiene el número de<br />

bytes (o palabras) que se transferirán. El tercero específica el número de<br />

100<br />

Controlador<br />

RS232C<br />

52

dispositivo o espacio de direcciones de E/S que se usará, con lo que se especifica<br />

qué dispositivo de E/S se desea. El cuarto indica si los datos se escribirán en el<br />

dispositivo de E/S o se leerán de él.<br />

Para escribir un bloque de 32 bytes de la dirección 100 en una terminal (por<br />

ejemplo, el dispositivo 4), la CPU escribe los números 100, 32 y 4 en los primeros<br />

tres registros del DMA, y luego el código de escribir ( por ejemplo, 1) en el cuarto,<br />

como se muestra en la figura 3.7. Una vez inicializado con estos valores, el<br />

controlador DMA emite una solicitud de bus para leer el byte 100 de la memoria,<br />

del mismo modo como la CPU leería de la memoria. Una vez que obtiene el byte, el<br />

controlador de DMA emite una solicitud de E/S al dispositivo 4, para escribir el byte<br />

en él. Una vez completadas ambas operaciones, el controlador de DMA incrementa<br />

en 1 su registro de dirección y decrementa en 1 su registro de cuenta. Si el registro<br />

de cuenta sigue siendo mayor que 0, se lee otro byte de la memoria y se escribe en<br />

el dispositivo.<br />

Cuando la cuenta por fin llega a 0, el controlador de DMA deja de transferir data y<br />

habilita la línea de interrupción en el chip del CPU. Con DMA, la CPU solo tiene que<br />

inicializar unos cuantos registros. Una vez hecho eso, queda libre para hacer otras<br />

cosas hasta que se completa la transferencia,<br />

Ejercicios propuestos<br />

1.- Asuma que un procesador de 16 bits y dos de 8 bits deben conectarse a un bus<br />

del sistema. Considere los siguientes detalles:<br />

• Todos los microprocesadores tiene el hardware necesario para cualquier tipo<br />

de transferencia: E/S programada, E/S mediante interrupciones y DMA.<br />

• Todos los microprocesadores tienen un bus de direcciones de 16 bits.<br />

• Hay dos tarjetas de memoria, de 64 Kbytes cada una, conectada al bus. El<br />

diseñador desea que se comparta la mayor cantidad de memoria posible.<br />

• El bus del sistema permite un máximo de cuatro líneas de interrupción y una<br />

de DMA.<br />

Haga las suposiciones adicionales que necesite, y:<br />

a) Establezca las especificaciones del bus en términos del número de líneas.<br />

b) Explique cómo es la interfaz de los dispositivos indicados arriba para<br />

conectarse al bus.<br />

2.- Una impresora de caracteres simples podría usar razonablemente bien una<br />

entrada/salida programada, pues su velocidad es lenta. Comparada con la<br />

unidad central de procesamiento. Sin embargo, la mayoría de las impresoras<br />

modernas utiliza el acceso directo a la memoria. ¡Por qué?.<br />

3.- ¿Por qué el acceso directo a la memoria (DMA) sería inútil si la computadora<br />

careciera de la capacidad de interrupción?<br />

53

Consulta en otros libros<br />

[Stallings, 2000] Dedica un capítulo a los distintos aspectos de la organización de<br />

E/S, también describe la interfaz entre los módulos de E/S y los dispositivos<br />

externos.<br />

[Tokheim, 1995] Hace una presentación de las interfaces con el microprocesador.<br />

[Tanenbaum, 2000] Cubre algunos aspectos de los temas de esta unidad.<br />

[Lameda, 1984] Presenta un estudio de los métodos para introducir y extraer datos<br />

del computador, también incluye el estudio de las interfaces con dispositivos para<br />

entrada/salida.<br />

[Sayers 1995] Contiene aspectos orientados al estudio de problemas externos de<br />

interfaz de un microprocesador con el mundo real.<br />

Se sugiere consultar también los otros textos recomendados en la bibliografía.<br />

� Consulta en la Web<br />

http://www.modelo.edu.mx/univ/virtech/circuito/paralelo.htm: Contiene información<br />

sobre el puerto paralelo del PC.<br />

http://www.iuma.ulpgc.es/users/armas/asignaturas/fundamentos/tutorial/entradas_y_<br />

salidas/index.htm: Es un tutorial con información asociada a la E/S del<br />

sistema.<br />

Ejercicios de Autoevaluación<br />

1.- Un dispositivo periférico junto con su controlador de E/S se conectará a un<br />

computador mediante el uso de un controlador DMA. Todos los módulos que<br />

conforman el sistema comparten el mismo bus “master”. El periférico solicita una<br />

transferencia al controlador de DMA, el cual a su vez solicita el bus a la CPU. Si<br />

la CPU no está utilizando el bus ni está en estado LOCK, lo concede al<br />

54

controlador de DMA, el cual a su vez informa al periférico para que prepare los<br />

datos a transferir.<br />

En una transferencia de entrada, los datos se mueven desde el periférico (I/O) a<br />

la memoria por el bus de datos sin pasar por el controlador de DMA y sin<br />

intervención de la CPU. Las líneas de control para leer la I/O (IOR) y para<br />

escribir la memoria (MEMW) son manejadas por el controlador de DMA. De la<br />

misma forma, en una transferencia de salida los datos se mueven desde la<br />

memoria a la I/O y el controlador de DMA maneja las líneas de control para leer<br />

la memoria (MEMR) y para escribir en el periférico (IOW).<br />

Con base a lo anteriormente expuesto, solucione la manera en que debe<br />

configurarse el sistema para el control de la E/S mediante el uso de la técnica<br />

DMA y que cumpla con las especificaciones dadas.<br />

2.- La conexión a periféricos en un sistema de microcomputador puede hacerse<br />

mediante el uso de chips especializados de entradas y salidas. Estos chips<br />

tienen como característica común su programabilidad por software y su conexión<br />

directa a los buses del sistema sin lógica auxiliar.<br />

Parta de la información dada anteriormente y resuelva el problema de la<br />

conexión de la PPI (interfaz periférica programable) tipo 82C55, en un sistema<br />

de microprocesador directamente ligados a los buses.<br />

Respuesta a los Ejercicios de Autoevaluación<br />

1.- En la siguiente figura se presenta una solución que permite el control de la E/S,<br />

mediante el uso de un controlador DMA.<br />

55

Se observa que el sistema configurado, consta de un periférico con su controlador<br />

de E/S, un controlador de DMA y las señales de pedido y concesión del bus que<br />

permiten alternar el "bus master" entre la CPU y el controlador de DMA<br />

2.- La disposición de la PPI 82C55 en este tipo de sistema, se muestra a<br />

continuación:<br />

CS A0 A1<br />

8<br />

D0<br />

D7<br />

A1<br />

A0<br />

__<br />

CS<br />

82C55<br />

Puerto A<br />

Puerto C<br />

Puerto B<br />

__ __<br />

RD WR RESET<br />

I/OR I/OW RESET<br />

8<br />

8<br />

8<br />

Bus de datos (8 bits)<br />

Bus de direcciones<br />

(16 bits)s)<br />

Bus de control<br />

56