Les assembleurs - IIHE

Les assembleurs - IIHE

Les assembleurs - IIHE

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

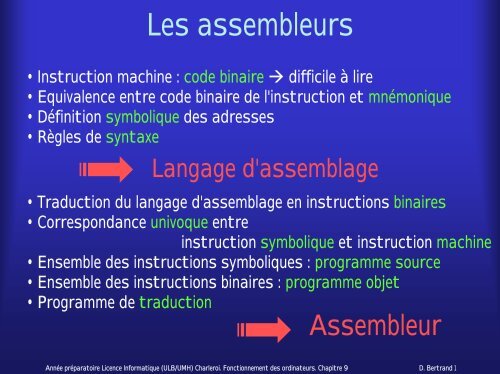

<strong>Les</strong> <strong>assembleurs</strong><br />

• Instruction machine : code binaire difficile à lire<br />

• Equivalence entre code binaire de l'instruction et mnémonique<br />

• Définition symbolique des adresses<br />

• Règles de syntaxe<br />

Langage d'assemblage<br />

• Traduction du langage d'assemblage en instructions binaires<br />

• Correspondance univoque entre<br />

instruction symbolique et instruction machine<br />

• Ensemble des instructions symboliques : programme source<br />

• Ensemble des instructions binaires : programme objet<br />

• Programme de traduction<br />

Assembleur<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 1

Syntaxe<br />

4 champs :<br />

délimiteurs (blancs)<br />

Label<br />

Opération<br />

Operands<br />

Commentaire<br />

symbole<br />

code fonctionnel<br />

adresses<br />

non traduit<br />

NB. le label est un symbole qui représente l'adresse de l'instruction<br />

Représentation des nombres :<br />

La base utilisée est représentée par un caractère spécial<br />

Exemple : Hexadécimal $ ($45)<br />

Décimal & (&69) Défaut : Hexadécimal<br />

Octal @ (@105)<br />

Binaire % (%1000101)<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 2

L'assembleur du PowerPC<br />

Unité de<br />

contrôle<br />

Unité<br />

arithm. réelle<br />

mémoire<br />

cache<br />

Unité<br />

arithm. entière<br />

R0<br />

R 1<br />

R31<br />

0 31<br />

<br />

CR<br />

XER<br />

Mémoire principale<br />

Registres<br />

0 31<br />

0 31<br />

FR0<br />

FR 1<br />

FR31<br />

0 63<br />

<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 3

Organisation mémoire<br />

• Mots de 32 bits<br />

• Convention ”Big-endian”<br />

0 8 16 24 32 40 48 56 63<br />

octet 0 octet 1 octet 7<br />

<br />

demi mot 0<br />

demi mot 2 demi mot 6<br />

mot 0 mot 4<br />

double mot 0<br />

• Processeur RISC<br />

• Instructions de longueur constante<br />

• Architecture ”Load and Store” (Charger/Déposer)<br />

• Opérations logiques et arithmétiques au départ des registres de<br />

travail<br />

• Adressage du type indexé (implicite indirect)<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 4

Catégories d'instruction<br />

• Instructions Charger/déposer (Load and Store)<br />

• Instructions d'arithmétique entière (registres R0-R31; pas d'accès<br />

direct à la mémoire)<br />

• Instructions de logique<br />

• Contrôle de séquence (branchement et branchement conditionnel)<br />

• Instructions d'arithmétique réelle (registres FR0-FR31)<br />

• Contrôle du processeur et des entrées/sorties<br />

Adressage<br />

• Mode indexé immédiat :<br />

Décalage ”n” (16 bits) par rapport à l'adresse contenue dans<br />

le registre R i n(R i ) A eff = n + [R i ]<br />

• Mode indexé registre :<br />

Somme du contenu de deux registres R i , R j A eff = [R i ] + [R j ]<br />

Si le symbole ”R j ” est remplacé par ”0” A eff = [R i ]<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 5

Charger & Déposer (Load & Store)<br />

Charger (L) : mémoire registre Déposer (ST) : registre mémoire<br />

y: B octet; y: H demi mot; y: W mot<br />

• Charger :<br />

LyZ<br />

LyZX<br />

R d ,n(R i )<br />

R d ,R i ,R j<br />

A eff =n+[R i ]; R d [A eff ]<br />

A eff =[R i ]+[R j ]; R d [A eff ]<br />

LyZU R d ,n(R i ) A eff =n+[R i ]; R d [A eff ]; R i A eff<br />

LyZUX R d ,R i ,R j<br />

A eff =[R i ]+[R j ]; R d [A eff ]; R j A eff<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

16 bits avec extension signe<br />

LHA, LHAX, LHAU, LHAUX : Load Half-word Algebraic<br />

Argument chargé avec extension de signe<br />

LFS, LFSX, LFSU, LFSUX : Load Floating-point registers (FR i )<br />

• Déposer :<br />

STy R s ,n(R i ) A eff =n+[R i ]; [R s ] A eff<br />

STyX R s ,R i ,R j A eff =[R i ]+[R j ]; [R s ] A eff<br />

STyU R s ,n(R i ) A eff =n+[R i ]; [R s ] A eff ; R i A eff<br />

STyUX R s ,R i ,R j A eff =[R i ]+[R j ]; [R s ] A eff ; R j A eff<br />

D. Bertrand 6

Transfert multiple<br />

LMW R d ,n(R i ) A eff =n+[R i ]; R d …R31 [A eff ] …[A eff +(31-d)x4]<br />

STMW R s ,n(R i ) A eff =n+[R i ]; R s …R31 [A eff ] …[A eff +(31-d)x4]<br />

R11<br />

R12<br />

R13<br />

00 00 4A A4 20<br />

00 00 00 84<br />

00 00 00 89<br />

Exemples<br />

adresse<br />

00004AA4<br />

00004AA8<br />

Mémoire<br />

5C BA 22 01<br />

12 8E 43 60<br />

R14<br />

00 00 43 60<br />

LHZ R14, 8A(R11)<br />

R15<br />

5C BA 22 01<br />

LWZX R15, R12, R11<br />

R16<br />

00 00 00 8E<br />

LBZX R16, R13, R11<br />

R17<br />

00 00 5C BA<br />

LHZUX R17, R12, R11<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 7

Instructions arithmétiques entières<br />

• Addition :<br />

ADD R d ,R i ,R j R d [R j ]+[R i ]<br />

ADDC R d ,R i ,R j R d [R j ]+[R i ]; CA report<br />

ADDE R d ,R i ,R j R d [R j ]+[R i ]+[CA]<br />

ADDI R d ,R i ,n R d [R i ]+n (16 bits; ext. signe)<br />

ADDIS R d ,R i ,n R d [R i ]+n (16 bits; 2 octets sup.)<br />

ADDIC R d ,R i ,n R d [R i ]+n (16 bits; ext. signe); CA report<br />

ADDME R d ,R i R d [R i ]-1+[CA]<br />

ADDZE R d ,R i R d [R i ]+[CA]<br />

• Soustraction : SUBF ⇔ ADD (SUBtract From)<br />

SUBF R d ,R i ,R j R d [R j ]-[R i ]<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 8

Remarques<br />

• <strong>Les</strong> instructions comportant un operand immédiat permettent<br />

de stocker des valeurs d'adresse dans les registres<br />

• Exemple :<br />

R21<br />

FF FF<br />

A8 F4<br />

ADDI R21, 0, $A8F4<br />

R21<br />

00 48 A8 F4 ADDIS R21, 0, $48<br />

• Registre de condition (CR : Condition Register)<br />

0 1 2 3<br />

LT<br />

GT<br />

EQ<br />

SO<br />

LT : bit = 1 si plus petit que zéro<br />

GT : bit = 1 si plus grand que zéro<br />

EQ : bit = 1 si égal à zéro<br />

SO : bit = 1 si dépassement de précision (remis à zéro par inst. spécifique)<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 9

• Registre d'exception (XER : eXcEption Register )<br />

0 1 2<br />

SO<br />

OV<br />

CA<br />

SO : bit = 1 si dépassement de précision (remis à zéro par inst. spécifique)<br />

OV : bit = 1 si dépassement de précision (bit = 0 dans autre cas)<br />

CA : bit = 1 report instruction arithmétique<br />

<strong>Les</strong> instructions arithmétiques peuvent modifier le contenu de CR et XER<br />

• Suffixe au code opératoire : "." pour CR<br />

"o" pour XER<br />

"o." pour CR et XER simultanément<br />

• Exemple<br />

R2<br />

00 00 00 65<br />

ADD. R1, R2, R3<br />

<br />

R1<br />

00 00 00 D8<br />

CR 0-3<br />

0100<br />

R3<br />

00 00 00 73<br />

SUBF. R5, R3, R2<br />

<br />

R5<br />

FF FF FF 02 1000<br />

R4<br />

00 00 00 73<br />

SUBF. R6, R4, R3<br />

<br />

R6<br />

00 00 00 00 0010<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 10

Arithmétique entière (suite)<br />

• Multiplication<br />

MULLW R d ,R i ,R j R d [R i ] x [R j ] (16 bits du bas [Low]; avec signe)<br />

MULHW R d ,R i ,R j R d [R i ] x [R j ] (16 bits du haut [High]; avec signe)<br />

MULHWU R d ,R i ,R j<br />

R d [R i ] x [R j ] (16 bits du haut; sans signe)<br />

MULLI R d ,R i ,n R d [R i ] x n (16 bits du bas; avec signe)<br />

• Division<br />

DIVW R d ,R i ,R j R d [R i ] / [R j ] (avec signe; reste non calculé)<br />

DIVWU R d ,R i ,R j R d [R i ] / [R j ] (sans signe ; reste non calculé)<br />

Calcul du reste : DIVW R d ,R i ,R j R d =quotient<br />

MULLW R r ,R d ,R j R r =quotient x diviseur<br />

• Négation<br />

SUBF R r ,R r ,R i R r =reste<br />

NEG R d ,R i R d -[R i ]<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 11

<strong>Les</strong> instructions de branchement<br />

Adressage<br />

• Branchement inconditionnel : 23 bits<br />

— Mode relatif : -2 24 ≤ adresse ≤ 2 24 -1<br />

s<br />

Déplacement<br />

0 7 8 30 31<br />

Ext. signe 0 0<br />

— Mode absolu : adresse ≤ 2 25 -1<br />

+<br />

PC<br />

0 6 7 30 31<br />

0 0 0 0 0 0 0 0<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 12

• Branchement conditionnel : 13 bits<br />

— Mode relatif : -2 14 ≤ adresse ≤ 2 14 -1<br />

s<br />

Déplacement<br />

0 17 18 30 31<br />

Extension signe 0 0<br />

+<br />

PC<br />

— Mode absolu : adresse ≤ 2 15 -1<br />

0 16 17 30 31<br />

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 13

<strong>Les</strong> registres de lien et de<br />

comptage<br />

LR : Link Register<br />

CTR : CounT Register<br />

Registres de 32 bits pas de restriction d'adressage<br />

• Chargement et référence :<br />

MTLR R s LR [R s ]<br />

MTCTR R s CTR [R s ]<br />

MFLR R d R d [LR]<br />

MFCTR R d R d [CTR]<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 14

Branchements<br />

Adresse cible définie dans l ’instruction : Bxxx Adr<br />

Condition bit CR<br />

Registre LR non modifié<br />

Registre LR mis à jour<br />

Relatif Absolu Relatif Absolu<br />

Néant - B BA BL BLA<br />

plus petit LT=1 BLT BLTA BLTL BLTLA<br />

plus petit ou<br />

égal<br />

GT=0 BLE BLEA BLEL BLELA<br />

égal à zéro EQ=1 BEQ BEQA BEQL BEQLA<br />

plus grand<br />

ou égal<br />

LT=0 BGE BGEA BGEL BGELA<br />

plus grand GT=1 BGT BGTA BGTL BGTLA<br />

différent de<br />

zéro<br />

EQ=0 BNE BNEA BNEL BNELA<br />

CTR=CTR-1;<br />

CTR=0<br />

CTR=CTR-1;<br />

CTR0<br />

- BDZ BDZA BDZL BDZLA<br />

- BDNZ BDNZA BDNZL BDNZLA<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 15

Branchements (suite)<br />

Adresse cible définie dans registre LR ou CTR : Bxxx<br />

Condition<br />

bit CR<br />

Registre LR non modifié<br />

Registre LR mis à jour<br />

Vers LR Vers CTR Vers LR Vers CTR<br />

Néant - BLR BCTR BLRL BCTRL<br />

plus petit LT=1 BLTLR BLTCTR BLTLRL BLTCTRL<br />

plus petit ou<br />

égal<br />

GT=0 BLELR BLECTR BLELRL BLECTRL<br />

égal à zéro EQ=1 BEQLR BEQCTR BEQLRL BEQCTRL<br />

plus grand<br />

ou égal<br />

LT=0 BGELR BGECTR BGELRL BGECTRL<br />

plus grand GT=1 BGTLR BGTCTR BGTLRL BGTCTRL<br />

différent de<br />

zéro<br />

EQ=0 BNELR BNECTR BNELRL BNECTRL<br />

CTR=CTR-1;<br />

CTR=0<br />

CTR=CTR-1;<br />

CTR0<br />

- BDZLR - BDZLRL -<br />

- BDNZLR - BDNZLRL -<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 16

Exemple<br />

• Nombre "n" en mémoire à l'adresse 456000 16 ;<br />

• Exposant "e" (>0) à l'adresse 456004 16 ;<br />

• Calculer n e et déposer le résultat à l'adresse 456008 16<br />

Utilisation d'un indice de boucle (R3)<br />

Utilisation du registre CTR<br />

ADDI R1,0,6000 adresse<br />

ADDIS R1,0,45 du nombre<br />

LWZX R2,0,R1 nombre<br />

LWZU R3,4(R1) exposant<br />

ADDI R4,0,1 init. res.<br />

ITER MULLW R4,R4,R2 multiplic.<br />

ADDI. R3,R3,-1 decr. exp.<br />

BGT ITER boucle<br />

STW R4,4(R1) stock. res.<br />

ADDI R1,0,6000 adresse<br />

ADDIS R1,0,45 du nombre<br />

LWZX R2,0,R1 nombre<br />

LWZU R3,4(R1) exposant<br />

ADDI R4,0,1 init. res.<br />

MTCTR R3 init. CTR<br />

ITER MULLW R4,R4,R2 multiplic.<br />

BDNZ ITER boucle<br />

STW R4,4(R1) stock. res.<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 17

Instructions de comparaison<br />

• Le registre de condition revisité :<br />

0<br />

4<br />

8<br />

12<br />

16<br />

20<br />

24<br />

28<br />

CR0<br />

CR1<br />

CR2<br />

CR3<br />

CR4<br />

CR5<br />

CR6<br />

CR7<br />

LT GT EQ SO<br />

• Définition des bits LT, GT ou EQ dans le champ CR k du registre CR<br />

suivant le résultat de la comparaison (cmp : ,=)<br />

CMPW CR k ,R i ,R j [R i ] cmp [R j ]<br />

CMPWI CR k ,R i ,n [R i ] cmp n (16 bits; extension signe)<br />

CMPL CR k ,R i ,R j |[R i ]| cmp |[R j ]|<br />

CMPLI CR k ,R i ,n |[R i ]| cmp n (16 bits; extension zéros)<br />

• Redéfinition des instructions de branchement<br />

Bxxxx CR k ,Adr branchement conditionnel vers Adresse selon état CR k<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 18

R9<br />

00 00 00 FF<br />

Exemple<br />

R10<br />

R11<br />

R12<br />

00 00 00 10<br />

00 00 00 00<br />

00 00 00 10<br />

CMPW CR1,R9,R10<br />

CMPW CR2,R11,R10<br />

CMPW CR6,R12,R10<br />

BGT CR2,CIBLE<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

CR 00 04 00 80 00 00<br />

20<br />

bit j de CR<br />

• Combinaison des champs du registre CR<br />

CRAND CRB d ,CRB i ,CRB j CRB d CRB i ∧ CRB j<br />

CRANDC CRB d ,CRB i ,CRB j CRB d CRB i ∧ ¬CRB j<br />

idem CRNANDy, CRNORy, CRORy, CRXORy<br />

Exemple : if ([R1]>[R2]) ∧ ([R3]

<strong>Les</strong> instructions logiques<br />

• <strong>Les</strong> ”portes”<br />

AND R d ,R i ,R j R d [R i ] ∧ [R j ]<br />

ANDC R d ,R i ,R j R d [R i ] ∧ ¬[R j ]<br />

ANDI R d ,R i ,n R d [R i ] ∧ n (16 bits; extension zéros)<br />

ANDIS R d ,R i ,n R d [R i ] ∧ n (16 bits; glissés à gauche)<br />

idem NANDy, NORy, ORy, XORy<br />

• Rotations (RL : Rotate Left)<br />

Masque M: mot de 32 bits où les bits M d<br />

à M f<br />

sont mis à 1.<br />

RLWNM R d ,R i ,R j ,M d ,M f R d M ∧ ([R i ] rotation gauche de [R j ] bits)<br />

RLWINM R d ,R i ,n,M d ,M f R d M ∧ ([R i ] rotation gauche de n bits)<br />

• Glissements (SL : Shift Left; SR : Shift Right)<br />

SLW R d ,R i ,R j R d [R i ] glissé à gauche de [R j ] bits (bits libérés mis à zéro)<br />

SRAW R d ,R i ,R j R d [R i ] glissé à droite de [R j ] bits (extension signe)<br />

SRAWI R d ,R i ,n R d [R i ] glissé à droite de n bits (extension signe)<br />

SRW R d ,R i ,R j R d [R i ] glissé à droite de [R j ] bits (extension zéros)<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 20

adresse<br />

<br />

<br />

Sous-modules, pile<br />

4400 BL MOD1 appel 1 er module<br />

8000 MOD1 ADDI R0,R0,-10 préparer pointeur pile<br />

STMW R29,4(R0) sauver R29-R31<br />

MFLR R29 sauver LR<br />

STW R29,0(R0) dans la pile<br />

<br />

9300 BL MOD2 appel 2 ème module<br />

<br />

9414 LWZ R29,0(R0) restaurer LR<br />

MTLR R29 de la pile<br />

LMW R29,4(R0) restaurer R29-R31<br />

A50<br />

ADDI R0,R0, 10 mise à jour pointeur pile<br />

BLR<br />

retour<br />

<br />

9800 MOD2 ADDI R0,R0,-8 préparer pointeur pile<br />

STMW R30,0(R0) sauver R30-R31<br />

<br />

9904 LMW R30,0(R0) restaurer R30-R31<br />

ADDI R0,R0, 8 mise à jour pointeur pile<br />

BLR<br />

retour<br />

PC<br />

00 00 98 93 99 44 94 80 04 08<br />

00 20<br />

0C<br />

24<br />

18 14 10 1C<br />

LR 00 00 00 93 44 04<br />

00<br />

R0 00 00 0A 60<br />

50 48<br />

A48<br />

A60<br />

[R30]<br />

[R31]<br />

00 00 44 04<br />

[R29]<br />

[R30]<br />

[R31]<br />

…<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 21

Pseudo-opérations<br />

Non exécutables : actions statiques mémoire, commandes à l'assembleur<br />

• Réservation d'espace mémoire<br />

o .long .long n 1 ,[n 2 ] stockage de nombres entiers (64 bits)<br />

o .word .word n 1 , [n 2 ] stockage de nombres entiers (32 bits)<br />

o .short .short n 1 ,[n 2 ] stockage de nombres entiers (16 bits)<br />

o .byte .byte n 1 ,[n 2 ] stockage d'octets (8 bits)<br />

o .double .double f stockage de réel (64 bits)<br />

o .float .float f stockage de réel (32 bits)<br />

o .space .space n remplissage de n octets avec zéros<br />

o .string .string s stockage d'une chaîne de caractères<br />

o .align .align n alignement sur le multiple suivant de n<br />

o .alon, .aloff<br />

alignement forcé (non-forcé) sur des mots<br />

• Définition de symboles<br />

o .set .set nom,expression association d'une expression<br />

au symbole<br />

• Modularité<br />

o .comm .comm nom,n o ,al bloc commun de n o octets aligné<br />

o .extern .extern nom spécification d'un symbole externe<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 22

• Contrôle du processus d'assemblage<br />

o .if,.else,.elseif,.endif<br />

assemblage conditionnel<br />

o .include .include fichier Inclusion d'instructions d'un<br />

fichier extérieur<br />

• Contrôle des informations imprimées<br />

o .page, .pagelen<br />

contrôle de pagination<br />

o .title<br />

définition d'un titre<br />

• Utilisation de macros<br />

o Bloc d'instructions et pseudo-instructions se répétant dans<br />

code source<br />

o Une macro peut faire appel à d'autres macros<br />

o Une macro peut recevoir des paramètres<br />

o Définition :<br />

.macro nom [,param]<br />

Code<br />

.mend<br />

o Chaque élément du code est reproduit dans la source<br />

o <strong>Les</strong> labels (suivis de ”!”) sont incrémentés<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 23

.macro sum,start,n,result<br />

LWZ R1,start(R0)<br />

ADDI R1,R1,-4<br />

LWZ R2,n(R0)<br />

MTCTR R2<br />

ADDI R3,0,0<br />

ITER! LWZU R4,4(R1)<br />

ADD R3,R3,R4<br />

BDNZ ITER!<br />

STW R3,result(R0)<br />

.mend<br />

Exemple<br />

Définition d'une somme de n nombres :<br />

1 ère expansion<br />

sum 0,-8,-4<br />

2 ème expansion<br />

sum 20,18, 1C<br />

LWZ R1,0(R0)<br />

ADDI R1,R1,-4<br />

LWZ R2,-8(R0)<br />

MTCTR R2<br />

ADDI R3,0,0<br />

ITER_1 LWZU R4,4(R1)<br />

ADD R3,R3,R4<br />

BDNZ ITER_1<br />

STW R3,-4(R0)<br />

LWZ<br />

ADDI<br />

LWZ<br />

MTCTR<br />

ADDI<br />

ITER_2 LWZU<br />

ADD<br />

BDNZ<br />

STW<br />

R1,20(R0)<br />

R1,R1,-4<br />

R2,18(R0)<br />

R2<br />

R3,0,0<br />

R4,4(R1)<br />

R3,R3,R4<br />

ITER_2<br />

R3,1C(R0)<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 24

Le processus d'assemblage<br />

• Correspondance univoque entre instruction source et code objet<br />

Exemple : ADDI R1,R8,-1 3829FFFF 16<br />

• Assignation d'une adresse à chaque instruction<br />

• Attribution de l'adresse instruction correspondante au label<br />

Adresses<br />

50400<br />

50404<br />

50408<br />

5040C<br />

50410<br />

50414<br />

50418<br />

<br />

ADDI R3,0,0<br />

CMPWI CR3,R2,0<br />

BEQ CR3,SUITE<br />

ITER LWZU R4,4(R1)<br />

ADD R3,R3,R4<br />

BDNZ ITER<br />

SUITE STW R3,16(R0)<br />

<br />

Adresses symboliques<br />

SUITE 50418<br />

ITER 5040C<br />

Constitution d'une<br />

table des symboles<br />

NB. SUITE :<br />

référence vers l'avant !<br />

• Vérification syntaxique (label, code opératoire, adresses, commentaire)<br />

Codes connus repris dans une table<br />

• Notification des erreurs et production d'une documentation<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 25

Init. compteur<br />

adresse<br />

lecture<br />

inst. suivante<br />

decodage<br />

code opératoire<br />

pseudo<br />

inst. ?<br />

non<br />

label ?<br />

oui<br />

label + adresse<br />

table symb.<br />

mise à jour<br />

compt. adresse<br />

long. programme<br />

=compt. adresse<br />

oui<br />

oui<br />

.end ?<br />

non<br />

Deux étapes<br />

2 ème étape<br />

non<br />

évaluation<br />

opérands<br />

Construction<br />

table symboles<br />

fin<br />

code objet +<br />

table reloc.<br />

fichier<br />

oui<br />

.end ?<br />

non<br />

évaluation<br />

opérands<br />

Détection des erreurs :<br />

• Syntaxe<br />

• Symboles indéfinis<br />

Création<br />

code objet et<br />

table relocation<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

oui<br />

Init. compteur<br />

adresse<br />

lecture<br />

inst. suivante<br />

decodage<br />

code opératoire<br />

pseudo<br />

inst. ?<br />

non<br />

évaluation<br />

code op +adres.<br />

assemblage<br />

code binaire<br />

mise à jour<br />

table relocation<br />

mise à jour<br />

compt. adresse<br />

D. Bertrand 26

Création et consultation de tables<br />

Usage fréquent par les logiciels système et de support<br />

• Techniques séquentielles<br />

o Information insérée en suivant le séquence temporelle<br />

o Recherche réalisée depuis le début de la table<br />

Recherche<br />

Exemple: Symbole Valeur Entrée<br />

1 ITER_1 5040C 1<br />

2 FIN 45700 2<br />

3 RET_2 7689A 3<br />

DEBUT 809D4 4<br />

RET_2 ? TEST DE8F0 5<br />

3 essais RAZ A678C 6<br />

entrée 0<br />

Insertion<br />

entrée <br />

entrée + 1<br />

info. insérée<br />

à entrée<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

entrée 1<br />

clef entrée<br />

OK?<br />

non<br />

entrée=<br />

long.tab.<br />

non<br />

entrée<br />

entrée + 1<br />

oui<br />

oui<br />

D. Bertrand 27<br />

succès<br />

erreur

Techniques binaires ou dichotomiques<br />

• Table triée selon l'ordre alphabétique des clefs<br />

• Début comparaison au milieu de la table<br />

• Symbole recherché = clef information retrouvée<br />

• Symbole recherché > clef poursuite au départ de la moitié supérieure<br />

• Symbole recherché < clef poursuite au départ de la moitié inférieure<br />

RET_2 ?<br />

2 essais<br />

Exemple: Symbole Valeur<br />

DEBUT 809D4<br />

FIN 45700<br />

1 ITER_1 5040C<br />

RAZ A678C<br />

2 RET_2 7689A<br />

TEST DE8F0<br />

Plus efficace :<br />

En moyenne : (log 2 n-1) essais<br />

Condition d'erreur : log 2 n essais<br />

! Mais opération de tri !<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 28

Techniques de hashing<br />

• Définition d'une fonction Φ prenant une valeur µ pour chaque clef :<br />

µ = Φ(clef)<br />

• Intervalle µ : [1, m] avec m ≥ n (longueur table)<br />

• La même valeur peut être attribuée à des clefs différentes<br />

• Collisions<br />

Exemple: Symbole Valeur Φ(clef)<br />

ITER_1 5040C 1<br />

FIN 45700 2<br />

RET_2 7689A 2<br />

DEBUT 809D4 8<br />

TEST DE8F0 4<br />

RAZ A678C 7<br />

En général m >> n !<br />

1<br />

2<br />

Pos. Symbol Value<br />

collision 1 ITER_1 5040C<br />

2 FIN 45700<br />

3 RET_2<br />

7689A<br />

4 TEST DE8F0<br />

5<br />

6<br />

7 RAZ A678C<br />

8 DEBUT 809D4<br />

RET_2 ?<br />

2 essais<br />

Année préparatoire Licence Informatique (ULB/UMH) Charleroi. Fonctionnement des ordinateurs. Chapitre 9<br />

D. Bertrand 29