générateur pwm svm triphasé pour moteur bldc schémas et ...

générateur pwm svm triphasé pour moteur bldc schémas et ...

générateur pwm svm triphasé pour moteur bldc schémas et ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

Applications maqu<strong>et</strong>te d'étude EP10K20<br />

GÉNÉRATEUR PWM SVM TRIPHASÉ POUR<br />

MOTEUR BLDC<br />

SCHÉMAS ET DESCRIPTIONS POUR EPLD<br />

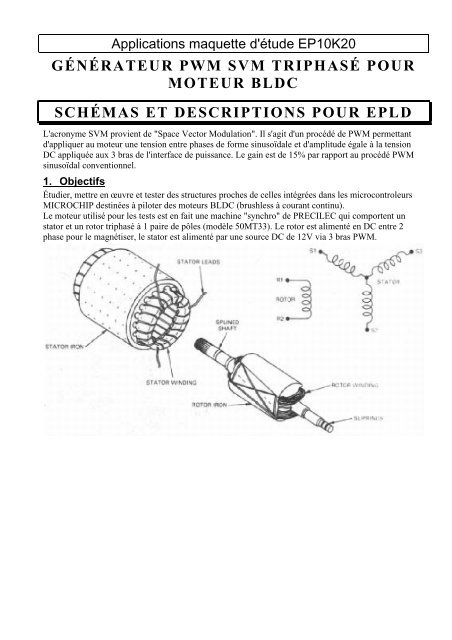

L'acronyme SVM provient de "Space Vector Modulation". Il s'agit d'un procédé de PWM perm<strong>et</strong>tant<br />

d'appliquer au <strong>moteur</strong> une tension entre phases de forme sinusoïdale <strong>et</strong> d'amplitude égale à la tension<br />

DC appliquée aux 3 bras de l'interface de puissance. Le gain est de 15% par rapport au procédé PWM<br />

sinusoïdal conventionnel.<br />

1. Objectifs<br />

Étudier, m<strong>et</strong>tre en œuvre <strong>et</strong> tester des structures proches de celles intégrées dans les microcontroleurs<br />

MICROCHIP destinées à piloter des <strong>moteur</strong>s BLDC (brushless à courant continu).<br />

Le <strong>moteur</strong> utilisé <strong>pour</strong> les tests est en fait une machine "synchro" de PRECILEC qui comportent un<br />

stator <strong>et</strong> un rotor <strong>triphasé</strong> à 1 paire de pôles (modèle 50MT33). Le rotor est alimenté en DC entre 2<br />

phase <strong>pour</strong> le magnétiser, le stator est alimenté par une source DC de 12V via 3 bras PWM.

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

2. Principe de la modulation SV<br />

On utilise la structure classique des 3 bras de commutateurs commandés par 3 comparateurs. Le signal<br />

de référence est de forme triangulaire <strong>et</strong> de fréquence F PWM très grande devant la fréquence des signaux<br />

ua, ub <strong>et</strong> uc (au moins 20x).<br />

CREMMEL Marcel Page 2/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

Dans ces conditions on peut écrire (commutateurs parfaits) :<br />

E<br />

E<br />

E<br />

Uan moy u a , Ubn moy u b <strong>et</strong> Ucn moy uc<br />

2<br />

2<br />

2<br />

Les valeurs instantanées de ua, ub <strong>et</strong> uc doivent rester à l'intérieur des valeurs crêtes de la<br />

porteuse ("carrier).<br />

En éliminant les composantes harmoniques (fréquences multiples de F PWM ), <strong>et</strong> si F PWM est très grande<br />

devant la fréquence des signaux ua, ub <strong>et</strong> uc, on peut confondre Uan moy <strong>et</strong> Uan.<br />

2.1 PWM sinusoïdal<br />

On produit 3 consignes sinusoïdales déphasées de 120° :<br />

2<br />

<br />

4<br />

<br />

u a m sinωt<br />

u b m sinωt<br />

u c m sinωt<br />

<br />

3 3 <br />

m : indice de modulation compris entre 0 <strong>et</strong> 1<br />

Il en résulte :<br />

E<br />

E 2<br />

E 4<br />

<br />

U aN m sinωt<br />

U bN m sinωt<br />

U cN m sinωt<br />

<br />

2<br />

2 3 2 3 <br />

CQFD<br />

Les tensions entre phases sont :<br />

E<br />

<br />

U ab 3 m sinωt<br />

<br />

2<br />

6 <br />

E<br />

5<br />

<br />

U bc 3 m sinωt<br />

<br />

2<br />

6 <br />

E<br />

3<br />

<br />

U ca 3 m sinωt<br />

<br />

2<br />

2 <br />

E<br />

L'amplitude maximum entre phases est donc de 3 , soit 86,6% de E <strong>pour</strong> m=1.<br />

2<br />

CREMMEL Marcel Page 3/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

2.2 Modulation Space Vector<br />

Les 6 commutateurs peuvent prendre 2 3<br />

états différents représentés dans la figure<br />

ci-contre.<br />

Ces 8 états sont codés de S0 à S7. La<br />

modulation "SV" consiste à piloter les<br />

commutateurs en PWM <strong>pour</strong> passer<br />

progressivement d'un état au suivant.<br />

Les 3 sorties a, b <strong>et</strong> c alimentent les 3<br />

phases du <strong>moteur</strong> qui créent des champs<br />

magnétiques déphasés de 120°.<br />

On peut alors représenter l'orientation du<br />

champ magnétique <strong>pour</strong> chacun des 8<br />

états. Ces états se transforment alors en<br />

vecteurs de tension ( U 0 à U <br />

7 sur la<br />

figure ci-contre).<br />

Les états S0 <strong>et</strong> S7 ne créent pas de champ<br />

magnétique, les vecteurs U 0 <strong>et</strong> U <br />

7 ont<br />

donc une longueur nulle.<br />

Les autres vecteurs ont une longueur de 1<br />

<strong>et</strong> respectent les relations suivantes :<br />

<br />

U 1 U 4<br />

U 2 U 5<br />

<br />

U 3 U 6<br />

<br />

U U 0<br />

U1 3 5 <br />

Objectif : créer un vecteur U de longueur<br />

constante qui suit, <strong>pour</strong> sa valeur maxi, le<br />

3<br />

cercle en pointillé de rayon .<br />

2<br />

Pour cela on module en conséquence les rapports cycliques de conduction des commutateurs dans<br />

chacun des 6 secteurs.<br />

En notant T 0 à T 7 la durée de chaque état S 0 à S 7 sur une période PWM, on obtient la relation vectorielle<br />

suivante (on suppose que la fréquence PWM est très grande devant la vitesse de rotation du vecteur U :<br />

T <br />

0 T <br />

1 T <br />

2 T <br />

3 T <br />

4 T <br />

5 T <br />

6 T <br />

7<br />

U U0<br />

U1<br />

U2<br />

U3<br />

U4<br />

U5<br />

U6<br />

U7<br />

TS<br />

TS<br />

TS<br />

TS<br />

TS<br />

TS<br />

TS<br />

TS<br />

Avec T S =T 0 +T 1 +T 2 +T 3 +T 4 +T 5 +T 6 +T 7 : période PWM<br />

Pour respecter c<strong>et</strong>te relation à la l<strong>et</strong>tre <strong>et</strong> donc atteindre l'objectif, il faut calculer les durées T 0 à T 7 <strong>pour</strong><br />

chaque position angulaire de U . On en déduit les consignes de tension ua, ub <strong>et</strong> uc nécessaires.<br />

Ce procédé n'est pas utilisé car il provoque de trop nombreux changements d'états (32 par période<br />

PWM) <strong>et</strong> les pertes par commutation deviennent excessives.<br />

Solution adoptée :<br />

Le diagramme vectoriel est divisé en 6 secteurs de 60°<br />

Dans chaque secteur, seuls 4 vecteurs U <br />

i sont utilisés <strong>pour</strong> produire U (les 2 vecteurs qui<br />

encadrent le secteur, ainsi que U 0 <strong>et</strong> U 7 ) :<br />

T <br />

0 T <br />

7<br />

secteur I :<br />

1 T <br />

2 T <br />

U U0<br />

U1<br />

U2<br />

U7<br />

Avec T S =T 0 +T 1 +T 2 +T 7 : période PWM<br />

T T T T<br />

S<br />

S<br />

S<br />

CREMMEL Marcel Page 4/25 TS électronique - 31/08/06<br />

S

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

secteur II<br />

T <br />

0 T <br />

3 7<br />

:<br />

2 T T <br />

U U0<br />

U2<br />

U3<br />

U7<br />

TS<br />

TS<br />

TS<br />

TS<br />

Avec T S =T 0 +T 2 +T 3 +T 7<br />

secteur III<br />

T <br />

0 T <br />

3 T <br />

7<br />

:<br />

4 T <br />

U U0<br />

U3<br />

U4<br />

U7<br />

TS<br />

TS<br />

TS<br />

TS<br />

Avec T S =T 0 +T 3 +T 4 +T 7<br />

secteur IV<br />

T <br />

0 T <br />

5 7<br />

:<br />

4 T T <br />

U U0<br />

U4<br />

U5<br />

U7<br />

Avec T S =T 0 +T 4 +T 5 +T 7<br />

TS<br />

TS<br />

TS<br />

TS<br />

secteur V<br />

T <br />

0 T <br />

5 T <br />

6 T <br />

7<br />

: U U0<br />

U5<br />

U6<br />

U7<br />

TS<br />

TS<br />

TS<br />

TS<br />

Avec T S =T 0 +T 5 +T 6 +T 7<br />

secteur VI<br />

T <br />

0 T <br />

6 T <br />

7<br />

:<br />

1 T <br />

U U0<br />

U6<br />

U1<br />

U7<br />

TS<br />

TS<br />

TS<br />

TS<br />

Avec T S =T 0 +T 6 +T 7 +T 7<br />

A un instant donné, l'angle magnétique du <strong>moteur</strong> se trouve dans un des 6 secteurs. On calcule alors<br />

les rapports cycliques nécessaires <strong>pour</strong> placer le vecteur U dans c<strong>et</strong>te position.<br />

C<strong>et</strong>te solution ne nécessite que 12 changements d'états par période PWM (pertes plus faibles) <strong>et</strong> réduit<br />

aussi le nombre de calculs nécessaires.<br />

Par exemple, dans le secteur I :<br />

T<br />

U <br />

T<br />

0<br />

S<br />

<br />

U<br />

0<br />

T<br />

<br />

T<br />

1<br />

S<br />

<br />

U<br />

1<br />

T<br />

<br />

T<br />

2<br />

S<br />

<br />

U<br />

2<br />

T<br />

<br />

T<br />

7<br />

S<br />

<br />

U<br />

7<br />

Avec T S =T 0 +T 1 +T 2 +T 7 : période PWM<br />

Quand le vecteur U se déplace de 0° à 60°, la durée T1 de S1 varie du max à 0 tandis que la<br />

durée T2 de S2 varie de 0 au max.<br />

On choisit généralement : T 0 = T 7 <strong>pour</strong> des raisons de symétrie <strong>et</strong> limiter les composantes<br />

harmoniques.<br />

Pour obtenir un vecteur U de longueur m (m est l'indice de modulation), on calcule T 0 , T 1 , T 2 <strong>et</strong><br />

T 7 à partir du diagramme vectoriel :<br />

T1<br />

2 π 2 π <br />

m sin<br />

<br />

m sin<br />

ω t <br />

TS<br />

3 3 3 3 <br />

T2<br />

2<br />

2<br />

m sin<br />

<br />

m sinω<br />

t<br />

TS<br />

3<br />

3<br />

T0 T7<br />

TS<br />

T<br />

1 T2<br />

<br />

<br />

T T 2<br />

S<br />

S<br />

CREMMEL Marcel Page 5/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

On en déduit :<br />

T0<br />

PWMa <br />

T<br />

S<br />

T1<br />

T<br />

PWMb <br />

T<br />

T<br />

PWMc <br />

0<br />

S<br />

T<br />

0<br />

T<br />

1<br />

S<br />

T<br />

2<br />

TS<br />

- T<br />

<br />

T<br />

S<br />

7<br />

Pour ne pas obtenir des durées T 0 <strong>et</strong> T 7 négatives (irréalisables !), le vecteur U doit rester à<br />

l'intérieur de l'hexagone. Le cas limite est obtenu à = 30°: on obtient T 1 =T 2 =T S /2 <strong>et</strong> T 0 =T 7 =0<br />

quand le vecteur U est sur le cercle en pointillé de rayon<br />

3 .<br />

2<br />

L'indice de modulation m doit donc rester inférieur à m max = 2<br />

3 = 0,866<br />

Pour c<strong>et</strong>te valeur m max , on obtient :<br />

E<br />

3<br />

amplitude de Ua , Ub <strong>et</strong> Uc = mmax<br />

E 0,433<br />

E<br />

2 4<br />

E<br />

amplitude de Uab, Ubc <strong>et</strong> Uca = 3 mmax E<br />

2<br />

<br />

Conclusion : les amplitudes sont augmentées de 15,5% par rapport au PWM sinusoïdal<br />

conventionnel.<br />

2.3 Durées des états des commutateurs dans chaque secteur<br />

Une simple transposition d'angle perm<strong>et</strong> de calculer les durées T 0 à T 7 des états S 0 à S 7 dans chacun des<br />

secteurs :<br />

Secteur I Secteur II Secteur III<br />

(0 /3) (/3 2/3) (2/3 )<br />

T1<br />

2 π T<br />

m.sin<br />

<br />

2 2 2.π T3<br />

2<br />

m.sin<br />

<br />

m.sin <br />

TS<br />

3 3 TS<br />

3 3 TS<br />

3<br />

T 2<br />

T<br />

m.sin<br />

<br />

3 2 T<br />

m.sin<br />

<br />

4 2 2<br />

<br />

m.sin<br />

<br />

TS<br />

3<br />

TS<br />

3 3 TS<br />

3 3 <br />

T0<br />

T7<br />

TS<br />

T<br />

1 T2<br />

T0<br />

T7<br />

TS<br />

T<br />

2 T3<br />

T0<br />

T7<br />

TS<br />

T<br />

3 T4<br />

<br />

<br />

<br />

<br />

T T 2.T<br />

T T 2.T<br />

T T 2.T<br />

S<br />

S<br />

S<br />

S<br />

S<br />

Secteur IV Secteur V Secteur VI<br />

( 4/3) (4/3 5/3) (5/3 2)<br />

T4<br />

2 4π T5 2 5π T6<br />

2<br />

m.sin<br />

m.sin<br />

<br />

m.sin2 <br />

TS<br />

3 3 TS<br />

3 3 TS<br />

3<br />

T5<br />

2<br />

T<br />

m.sin <br />

6 2 4<br />

T<br />

m.sin<br />

<br />

1 2 5<br />

<br />

m.sin<br />

<br />

TS<br />

3<br />

TS<br />

3 3 TS<br />

3 3 <br />

T0<br />

T7<br />

TS<br />

T<br />

4 T5<br />

T0<br />

T7<br />

TS<br />

T<br />

5 T6<br />

T0<br />

T7<br />

TS<br />

T<br />

6 T1<br />

<br />

<br />

<br />

T T 2.T T T 2.T<br />

T T 2.T<br />

S<br />

S<br />

S<br />

S<br />

S<br />

On constate que les calculs donnent des résultats identiques dans chaque secteur ce qui simplifie la<br />

réalisation du modulateur.<br />

S<br />

S<br />

S<br />

S<br />

S<br />

S<br />

S<br />

S<br />

<br />

CREMMEL Marcel Page 6/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

2.4 Succession des états des commutateurs dans chaque secteur<br />

Les solutions sont multiples, mais on s'impose le critère suivant : pas de changement d'état simultané<br />

de 2 bras. On obtient les résultats suivants :<br />

Secteur VI Secteur V Secteur IV Secteur III Secteur II Secteur I<br />

Etats S0 (000) S1 (100) S2 (110) S7 (111) S2 (110) S1 (100) S0 (000)<br />

Durées T0/2 T1/2 T2/2 T7 T2/2 T1/2 T0/2<br />

UaN<br />

UbN<br />

UcN<br />

Etats S0 (000) S3 (010) S2 (110) S7 (111) S2 (110) S3 (010) S0 (000)<br />

Durées T0/2 T3/2 T2/2 T7 T2/2 T3/2 T0/2<br />

UaN<br />

UbN<br />

UcN<br />

Etats S0 (000) S3 (010) S4 (011) S7 (111) S4 (011) S3 (010) S0 (000)<br />

Durées T0/2 T3/2 T4/2 T7 T4/2 T3/2 T0/2<br />

UaN<br />

UbN<br />

UcN<br />

Etats S0 (000) S5 (001) S4 (011) S7 (111) S4 (011) S5 (001) S0 (000)<br />

Durées T0/2 T5/2 T4/2 T7 T4/2 T5/2 T0/2<br />

UaN<br />

UbN<br />

UcN<br />

Etats S0 (000) S5 (001) S6 (101) S7 (111) S6 (101) S5 (001) S0 (000)<br />

Durées T0/2 T5/2 T6/2 T7 T6/2 T5/2 T0/2<br />

UaN<br />

UbN<br />

UcN<br />

Etats S0 (000) S1 (100) S6 (101) S7 (111) S6 (101) S1 (100) S0 (000)<br />

Durées T0/2 T1/2 T6/2 T7 T6/2 T1/2 T0/2<br />

UaN<br />

UbN<br />

UcN<br />

TS<br />

2.5 Calculs des rapports cycliques dans chaque secteur<br />

Ces calculs étant numériques, il est nécessaire de fixer la résolution de l'angle magnétique du <strong>moteur</strong>.<br />

Dans l'exemple qui suit la résolution choisie est de 360/(6x256)=0,234°.<br />

Il serait possible de calculer les 3 rapports cycliques de chaque bras <strong>pour</strong> les 6x256=1536 angles<br />

élémentaires <strong>et</strong> les ranger dans une table en mémoire morte. C<strong>et</strong>te solution est rej<strong>et</strong>ée car la taille de la<br />

table excède les possibilités de l'EPLD. Celle-ci n'intègre que 12288 bits alors que la table nécessite<br />

1536x3x8 bits (3 rapports cycliques codés sur 8 bits) = 36864 bits.<br />

CREMMEL Marcel Page 7/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

Les symétries dans le diagramme vectoriel perm<strong>et</strong>tent de réduire la taille de la table, mais au détriment<br />

de calculs supplémentaires que l'EPLD doit exécuter.<br />

Les 2 tables utilisées perm<strong>et</strong>tent de déterminer les rapports cycliques T A /T S <strong>et</strong> T B /T S dans un secteur :<br />

T<br />

Table T A :<br />

A 2 π <br />

m sin<br />

<br />

<br />

TS<br />

3 3 <br />

T<br />

Table T B :<br />

B 2<br />

<br />

m sin<br />

<strong>pour</strong> 0 <br />

TS<br />

3<br />

3<br />

La correspondance entre les temps Ti <strong>et</strong> T A ou T B est donnée dans le tableau ci-dessous :<br />

UaN UbN UcN<br />

Sect. Période PWM T A T B PWMa PWMb PWMc<br />

I T S = T 1 +T 2 +T 0 +T 7 T1 T2<br />

T0<br />

T0<br />

T1<br />

T0<br />

TA<br />

TS<br />

T7<br />

TS<br />

T<br />

<br />

<br />

T<br />

T T T T<br />

II T S = T 2 +T 3 +T 0 +T 7 T2 T3<br />

III T S = T 3 +T 4 +T 0 +T 7 T3 T4<br />

T<br />

T<br />

0<br />

S<br />

T<br />

T<br />

T<br />

S<br />

S<br />

3<br />

T<br />

7<br />

S<br />

T<br />

<br />

0<br />

T<br />

<br />

S<br />

T<br />

T<br />

T<br />

S<br />

T<br />

S<br />

B<br />

0<br />

S<br />

T<br />

T<br />

T<br />

T<br />

0<br />

S<br />

0<br />

S<br />

S<br />

T<br />

T<br />

S<br />

0<br />

T<br />

S<br />

T<br />

T<br />

S<br />

T<br />

S<br />

7<br />

3<br />

T<br />

<br />

T<br />

<br />

S<br />

0<br />

T<br />

S<br />

T<br />

T<br />

S<br />

T<br />

S<br />

0<br />

0<br />

A<br />

IV T S = T 4 +T 5 +T 0 +T 7 T4 T5<br />

T<br />

S<br />

T<br />

T<br />

S<br />

7<br />

T<br />

<br />

S<br />

T<br />

T<br />

S<br />

0<br />

T<br />

0<br />

T<br />

T<br />

S<br />

5<br />

T<br />

<br />

0<br />

T<br />

T<br />

S<br />

B<br />

T<br />

T<br />

0<br />

S<br />

T0<br />

T5<br />

T0<br />

T<br />

<br />

V T S = T 5 +T 6 +T 0 +T 7 T5 T6 TS<br />

TS<br />

A<br />

T<br />

S<br />

T<br />

T<br />

S<br />

7<br />

T<br />

<br />

S<br />

T<br />

T<br />

S<br />

0<br />

T<br />

T<br />

0<br />

S<br />

VI T S = T 6 +T 1 +T 0 +T 7 T6 T1<br />

T<br />

T<br />

0<br />

S<br />

T<br />

S<br />

T<br />

T<br />

S<br />

7<br />

T<br />

<br />

S<br />

T<br />

T<br />

S<br />

0<br />

T<br />

0<br />

T<br />

T<br />

S<br />

1<br />

T<br />

<br />

0<br />

T<br />

T<br />

S<br />

B<br />

Le rapport cyclique T 0 /T S est calculé comme suit :<br />

T0<br />

T7<br />

TS<br />

T<br />

A TB<br />

1 T<br />

<br />

<br />

<br />

A T<br />

1 <br />

TS<br />

TS<br />

2.TS<br />

2 TS<br />

T<br />

B<br />

S<br />

<br />

<br />

<br />

CREMMEL Marcel Page 8/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

2.6 Simulation Excel<br />

Le tableur Excel est utilisé <strong>pour</strong> valider les tables de valeurs des rapports cycliques. Le fichier<br />

"Table_TA_TB_T0.xls" comporte les tables <strong>et</strong> les formules de calcul décrites précédemment.<br />

On obtient les résultats suivants sur 360° magnétiques :<br />

Les 3 rapports cycliques<br />

1<br />

0,9<br />

0,8<br />

0,7<br />

0,6<br />

0,5<br />

0,4<br />

PWMb<br />

PWMa<br />

PWMc<br />

0,3<br />

0,2<br />

0,1<br />

0<br />

0 60 120 180 240 300 360<br />

Ua-Ub<br />

1<br />

0,8<br />

Uc-Ua<br />

Les 3 tensions inter-phases (relativement à E)<br />

Ua-Ub<br />

Ub-Uc<br />

0,6<br />

0,4<br />

0,2<br />

0<br />

-0,2<br />

-0,4<br />

-0,6<br />

-0,8<br />

-1<br />

0 60 120 180 240 300 360<br />

CREMMEL Marcel Page 9/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

3. Schéma principal<br />

OUTPUT<br />

GND<br />

LINE1 PIN_90<br />

CODA PIN_110<br />

CODB PIN_109<br />

LIMIT<br />

LIMIT[5..0]<br />

inst5<br />

COL1<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

NOT<br />

inst11<br />

PIN_103<br />

Simul_Hall<br />

EN_COD H1<br />

CODA<br />

H2<br />

CODB<br />

H3<br />

CLK_18M432<br />

EN_2K25<br />

inst3<br />

Reg_Niveau<br />

EN_COD NIV[7..0]<br />

CODA<br />

CODB<br />

CLK_18M432<br />

EN_2K25<br />

Gene_3_SVM<br />

H1<br />

SYNC<br />

H2<br />

POS[7..0]<br />

H3<br />

SECT[2..0]<br />

M[7..0]<br />

PWM1[7..0]<br />

LIM[5..0] PWM2[7..0]<br />

CLK_18M432 PWM3[7..0]<br />

EN_72K<br />

inst<br />

DELAY<br />

DELAY[5..0]<br />

Generateur_PWM<br />

PDC1[7..0]<br />

PDC2[7..0]<br />

PDC3[7..0]<br />

DELAY[5..0]<br />

CLK_18M432<br />

CLK_EN<br />

inst1<br />

PTMR[7..0]<br />

TEST<br />

PWM1D<br />

PWM1U<br />

PWM2D<br />

PWM2U<br />

PWM3D<br />

PWM3U<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

H1<br />

H2<br />

H3<br />

SYNC<br />

TEST<br />

PWM1D<br />

PWM1U<br />

PWM2D<br />

PWM2U<br />

PWM3D<br />

PWM3U<br />

TEST2<br />

TEST1<br />

PIN_62<br />

PIN_63<br />

PIN_64<br />

PIN_74<br />

MAGN_POS[7..0]<br />

SECT[2..0] PIN_71<br />

PIN_72<br />

PIN_73<br />

PIN_75<br />

PIN_48<br />

PIN_49<br />

PIN_50<br />

PIN_51<br />

PIN_53<br />

PIN_54<br />

PIN_78<br />

PIN_76<br />

PIN_166<br />

PIN_167<br />

PIN_168<br />

PIN_169<br />

PIN_171<br />

PIN_172<br />

PIN_173<br />

PIN_174<br />

inst10<br />

inst4<br />

OUTPUT<br />

CLK_CNAPIN_164<br />

PIN_91<br />

CLK_18M432<br />

INPUT<br />

VCC<br />

Gene_CLK<br />

CLK_18M432<br />

EN_2K25<br />

EN_72K<br />

EN_4M608<br />

Note : le <strong>moteur</strong> actuellement utilisé n'étant pas équipé de capteurs à eff<strong>et</strong> Hall, on utilise un simulateur<br />

("Simul_Hall") qui produit les 3 signaux H1, H2 <strong>et</strong> H3 déphasés de 60°. La fréquence est réglable avec<br />

le codeur incrémental <strong>et</strong> détermine la vitesse de rotation du <strong>moteur</strong>.<br />

Fonction : le codeur incrémental règle indépendamment la tension appliquée au <strong>moteur</strong> (quand LINE1<br />

est à "0") <strong>et</strong> la vitesse de rotation du <strong>moteur</strong> (quand LINE1 est à "1"). Les signaux PWM1D à PWM3U<br />

pilotent une interface de puissance (voir schéma plus loin) qui produit les 3 tensions inter-phases<br />

sinusoïdales d'alimentation des 3 stators du <strong>moteur</strong>.<br />

Avec le <strong>moteur</strong> utilisé (1 paire de pôles), la vitesse de rotation est réglable entre 0 <strong>et</strong> 1384tr/mn avec<br />

une résolution de 21,97tr/mn.<br />

La consigne de niveau (NV) a une résolution de 8 bits.<br />

Le signal d'horloge CLK_18M432 est produit par l'oscillateur à quartz OSC1 <strong>et</strong> vaut 18,432MHz.<br />

4. Gene_CLK<br />

CLK_18M432<br />

inst2<br />

INPUT<br />

VCC<br />

Div_32<br />

Div_256<br />

inst1<br />

CLK<br />

EN<br />

inst3<br />

CLK<br />

DIV_4<br />

CLK<br />

OUT<br />

OUT<br />

EN_CLK<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

EN_2K25<br />

EN_72K<br />

EN_4M608<br />

On cherche à rendre<br />

l'ensemble du schéma<br />

synchrone avec l'horloge<br />

18,432MHz.<br />

La fonction "Gene_CLK"<br />

produit des signaux de<br />

validation d'horloge (durée =<br />

1 période 18,432MHz) avec<br />

une fréquence déterminée en<br />

fonction des besoins :<br />

EN_2K25 : 2,25KHz<br />

EN_72K : 72kHz<br />

EN_4M608 : 4,608MHz<br />

inst<br />

CREMMEL Marcel Page 10/25 TS électronique - 31/08/06

4.1 DIV_4<br />

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

subdesign DIV_4<br />

(<br />

CLK : input;<br />

EN_CLK : output;<br />

)<br />

variable<br />

Q[1..0] : DFF;<br />

begin<br />

Q[].clk=CLK;<br />

Q[].d=Q[].q+1;<br />

EN_CLK=Q[].q==0;<br />

end;<br />

4.2 DIV_256<br />

SUBDESIGN Div_256<br />

(<br />

CLK : INPUT;<br />

OUT : OUTPUT;<br />

)<br />

VARIABLE Q[7..0] : DFF;<br />

BEGIN<br />

Q[].CLK=CLK;<br />

Q[].D=Q[].Q+1;<br />

OUT=Q[].Q==0;<br />

END;<br />

4.3 DIV_32<br />

SUBDESIGN Div_32<br />

(<br />

CLK : INPUT;<br />

EN : input;<br />

OUT : OUTPUT;<br />

)<br />

VARIABLE Q[4..0] : DFFE;<br />

BEGIN<br />

Q[].CLK=CLK;<br />

Q[].ena=EN;<br />

Q[].D=Q[].Q+1;<br />

OUT=(Q[].Q==0)&EN;<br />

END;<br />

5. Simul_Hall<br />

EN_COD<br />

INPUT<br />

VCC<br />

AND2<br />

CODA<br />

CODB<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

inst4<br />

NOT<br />

inst12<br />

NOT<br />

inst13<br />

Anti_rebonds<br />

IN OUT<br />

EN<br />

CLK<br />

inst3<br />

Anti_rebonds<br />

IN OUT<br />

EN<br />

CLK<br />

decod_a_b<br />

A DIR<br />

B CLK<br />

inst15<br />

CPT_UD<br />

UD<br />

CLK<br />

inst5<br />

POS[6..0]<br />

SENS<br />

NCO_H<br />

FREQ[6..0]<br />

CLK<br />

inst<br />

H1<br />

H2<br />

H3<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

H1<br />

H2<br />

H3<br />

inst2<br />

CLK_18M432<br />

EN_2K25<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

Les signaux CODA <strong>et</strong> CODB produits par le codeur incrémental passent par des fonctions anti-rebonds<br />

indispensables compte-tenu de la fréquence d'horloge.<br />

Le sens de chaque cran est détecté par la fonction "decod_a_b" :<br />

DIR indique le sens au moment du sur CLK : "1" : CW <strong>et</strong> "0" : CCW<br />

CREMMEL Marcel Page 11/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

Les sur CLK sont comptés ou décomptés par la fonction CPT_UD :<br />

POS[6..0] : nombre de crans. Initialisé à 0 au moment de la configuration de l'EPLD.<br />

SENS : indique le sens du nombre de crans ("0" : CW, "1" : CCW)<br />

La fonction CPT_UD pilote un oscillateur numérique commandé (NCO) qui produit en interne un<br />

signal carré de fréquence proportionnelle à POS[]=FREQ[] :<br />

FCLK_18M432<br />

FH<br />

FREQ[] . Soit une résolution de 2,19Hz <strong>et</strong> une fréquence max de 138,4Hz<br />

23<br />

2<br />

C<strong>et</strong>te fréquence est appliquée à un compteur 3 bits modulo 6 dont les sorties sont décodées <strong>pour</strong><br />

produire les 3 signaux H1, H2 <strong>et</strong> H3 déphasés de 60°.<br />

La fréquence de ces signaux est donc réglable de 0Hz à 23,07Hz avec une résolution de 0,366Hz.<br />

5.1 Anti_rebonds<br />

IN<br />

EN<br />

CLK<br />

Les 2 premières bascules D perm<strong>et</strong>tent d'éliminer les eff<strong>et</strong>s des rebonds plus courts que 2 périodes<br />

d'horloge validées : soit 2/2,25kHz = 889µS<br />

5.2 Decod_a_b<br />

SUBDESIGN decod_a_b<br />

(<br />

A, B : INPUT;<br />

DIR, CLK : OUTPUT;<br />

)<br />

VARIABLE<br />

DIR_FF : DFF;<br />

BEGIN<br />

DIR_FF.CLK = B;<br />

DIR_FF.D = A;<br />

DIR = DIR_FF.Q;<br />

CLK = A & B;<br />

END;<br />

L'information de direction est échantillonnée sur A au de B.<br />

Le signal CLK est produit par une fonction ET entre A <strong>et</strong> B.<br />

5.3 CPT_UD<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

DFFE<br />

PRN<br />

D Q<br />

ENA<br />

CLRN<br />

inst<br />

DFFE<br />

PRN<br />

D Q<br />

ENA<br />

CLRN<br />

inst2<br />

inst4<br />

AND2<br />

subdesign CPT_UD<br />

(<br />

UD, CLK : input;<br />

POS[6..0] : output;<br />

SENS : output;<br />

)<br />

variable Q[7..0] : dff;<br />

begin<br />

Q[].clk=CLK;<br />

if UD then Q[].d=Q[].q+1;<br />

else Q[].d=Q[].q-1;<br />

end if;<br />

if Q7.q then POS[6..0]=!Q[6..0];<br />

else POS[6..0]= Q[6..0];<br />

end if;<br />

SENS=Q7.q;<br />

end;<br />

Les sur CLK sont comptés ou décomptés par la fonction CPT_UD :<br />

OR2<br />

inst3<br />

AND2<br />

inst5<br />

AND2<br />

inst6<br />

OR2<br />

inst7<br />

DFFE<br />

PRN<br />

D Q<br />

ENA<br />

CLRN<br />

inst8<br />

NOT<br />

inst9<br />

OUTPUT<br />

OUT<br />

CREMMEL Marcel Page 12/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

POS[6..0] : nombre de crans. Initialisé à 0 au moment de la configuration de l'EPLD.<br />

SENS : indique le sens du nombre de crans ("0" : CW, "1" : CCW)<br />

5.4 NCO_H<br />

subdesign NCO_H<br />

( FREQ[6..0] : input;<br />

CLK<br />

: input;<br />

H1,H2,H3 : output;<br />

)<br />

variable<br />

REG[22..0] : dff;<br />

FREQW[22..0] : node;<br />

QH[2..0] : dff;<br />

begin<br />

FREQW[22..7]=gnd; FREQW[6..0]=FREQ[6..0];<br />

REG[].d = REG[].q + FREQW[];<br />

REG[].clk = CLK;<br />

QH[].clk = REG22.q;<br />

if QH[].q==5 then QH[].d=0;<br />

else QH[].d=QH[].q+1;<br />

end if;<br />

H1=(QH[].q==0) or (QH[].q==1) or (QH[].q==2);<br />

H2=(QH[].q==1) or (QH[].q==2) or (QH[].q==3);<br />

H3=(QH[].q==2) or (QH[].q==3) or (QH[].q==4);<br />

end;<br />

La structure est classique. Le registre <strong>et</strong> l'additionneur ont une taille de 23 bits <strong>pour</strong> obtenir la résolution<br />

de réglage voulue.<br />

La sortie REG22.q est utilisée comme signal d'horloge d'un compteur 3 bits modulo 6. Les 3 sorties sont<br />

décodées <strong>pour</strong> produire les 3 signaux H1, H2 <strong>et</strong> H3 déphasés de 60°.<br />

6. Reg_Niveau<br />

EN_COD<br />

INPUT<br />

VCC<br />

AND2<br />

CODA<br />

CODB<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

inst4<br />

NOT<br />

inst12<br />

NOT<br />

inst13<br />

Anti_rebonds<br />

IN<br />

EN<br />

inst3<br />

CLK<br />

Anti_rebonds<br />

IN<br />

EN<br />

CLK<br />

OUT<br />

OUT<br />

decod_a_b<br />

A DIR<br />

B CLK<br />

inst15<br />

inst1<br />

Cpt_UD_Niv<br />

updow n<br />

clock<br />

up/down<br />

q[7..0]<br />

OUTPUT<br />

NIV[7..0]<br />

inst2<br />

CLK_18M432<br />

EN_2K25<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

La structure est similaire à la fonction "Simul_Hall", mais elle ne comporte pas de fonction NCO.<br />

La fonction de comptage des crans diffère aussi; elle ne nécessite pas de commentaires supplémentaires.<br />

CREMMEL Marcel Page 13/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

7. Gene_3SVM<br />

Capteur_Hall<br />

OUTPUT<br />

OUTPUT<br />

SYNC<br />

POS[7..0]<br />

H1<br />

H2<br />

H3<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

H1<br />

H2<br />

H3<br />

CLK_18M432<br />

EN_72K<br />

inst<br />

SECT[2..0]<br />

PULSE_H<br />

M_POS[7..0]<br />

ROM_TA<br />

address[7..0] q[7..0]<br />

inst7<br />

ROM_TB<br />

address[7..0] q[7..0]<br />

inst8<br />

OUTPUT<br />

Modulation<br />

TA[7..0]<br />

TB[7..0]<br />

M[7..0]<br />

SECT[2..0]<br />

TAM[7..0]<br />

TBM[7..0]<br />

M[7..0]<br />

INPUT<br />

VCC<br />

inst1<br />

CALC_SVM<br />

LIMIT_3PWM<br />

SECT[2..0]<br />

TA[7..0]<br />

TB[7..0]<br />

PWM_R[7..0]<br />

PWM_Y[7..0]<br />

PWM_B[7..0]<br />

IN1[7..0]<br />

IN2[7..0]<br />

IN3[7..0]<br />

OUT1[7..0]<br />

OUT2[7..0]<br />

OUT3[7..0]<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

PWM1[7..0]<br />

PWM2[7..0]<br />

PWM3[7..0]<br />

LIM[5..0]<br />

CLK_18M432<br />

EN_72K<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

inst9<br />

LIM[5..0]<br />

CLK<br />

EN<br />

inst4<br />

La fonction produit 3 signaux numériques SVM codés en Bd sur 8 bits <strong>et</strong> déphasés de 120°. Ils sont<br />

synchronisés sur les signaux des capteurs à eff<strong>et</strong> Hall : H1, H2 <strong>et</strong> H3. Leurs niveaux sont réglables avec<br />

les entrées NIV1, NIV2 <strong>et</strong> NIV3 codées en C2 (-128 à +127).<br />

La structure utilise 2 ROM (taille = 256 oct<strong>et</strong>s) contenant les tables TA <strong>et</strong> TB (voir §2).<br />

Les ROM sont adressées par M_POS[7..0] qui représente la position angulaire du <strong>moteur</strong> dans un des 6<br />

secteurs. Le codage sur 8 bits donne une résolution de 60/256=0,235° magnétique.<br />

Le secteur actuel est donné par SECT[2..0] qui évolue entre 0 <strong>et</strong> 5. C<strong>et</strong>te information est utilisée par la<br />

fonction "CAL_SVM" qui calcule les rapports cycliques perm<strong>et</strong>tant de produire la tension<br />

d'alimentation adéquate du <strong>moteur</strong>.<br />

La fonction "Modulation" multiplie les valeurs TA[] <strong>et</strong> TB[] (en BN) avec l'indice de modulation M[] <strong>et</strong><br />

réalise donc le réglage de niveau. On ne garde que l'oct<strong>et</strong> de poids fort du résultat.<br />

La fonction "LIMIT_PWM" évite d'obtenir les rapports cycliques extrêmes de 0% <strong>et</strong> 100% <strong>et</strong> bloquer le<br />

hachage des courants dans le <strong>moteur</strong>.<br />

CREMMEL Marcel Page 14/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

7.1 Capteur_Hall<br />

Anti_rebonds<br />

Cpt_Sect_SVM<br />

up counter<br />

sclr<br />

modulus 6<br />

H1<br />

H2<br />

H3<br />

CLK_18M432<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

inst<br />

IN<br />

EN<br />

CLK<br />

IN<br />

EN<br />

CLK<br />

OUT<br />

Anti_rebonds<br />

inst4<br />

IN<br />

EN<br />

CLK<br />

OUT<br />

Anti_rebonds<br />

OUT<br />

Pulse_Hall<br />

H1<br />

H2<br />

H3<br />

CLK<br />

inst6<br />

PULSE_0<br />

PULSE_H<br />

clock<br />

clk_en<br />

inst13<br />

Cpt_Magn_pos<br />

up counter<br />

sclr<br />

clock<br />

clk_en<br />

cnt_en<br />

inst10<br />

NOT<br />

inst11<br />

q[2..0]<br />

q[7..0]<br />

cout<br />

OR2<br />

OUTPUT<br />

OUTPUT<br />

OUTPUT<br />

SECT[2..0]<br />

PULSE_H<br />

M_POS[7..0]<br />

EN_72K<br />

INPUT<br />

VCC<br />

inst5<br />

Cpt_Mesure_TH<br />

up counter<br />

sclr<br />

inst7<br />

clock<br />

cnt_en<br />

q[15..0]<br />

Periode_H<br />

DFF<br />

data[15..0]<br />

clock<br />

q[15..0]<br />

enable<br />

inst8<br />

inst12<br />

Div_prog_16b<br />

down counter<br />

sload<br />

data[15..0]<br />

clock<br />

q[15..0]<br />

cout<br />

inst9<br />

7.1.1 Anti_rebonds<br />

Fonctions déjà décrites (§5.1)<br />

7.1.2 Pulse_Hall<br />

DFF<br />

XOR<br />

H1<br />

INPUT<br />

VCC<br />

D PRN Q<br />

inst1<br />

NOT<br />

AND2<br />

OUTPUT<br />

PULSE_0<br />

CLRN<br />

inst<br />

inst8<br />

inst7<br />

H2<br />

INPUT<br />

VCC<br />

DFF<br />

D PRN Q<br />

XOR<br />

inst4<br />

OR3<br />

inst2<br />

OUTPUT<br />

PULSE_H<br />

CLRN<br />

inst3<br />

DFF<br />

XOR<br />

H3<br />

CLK<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

D PRN Q<br />

inst6<br />

CLRN<br />

inst5<br />

C<strong>et</strong>te fonction détecte les changements d'états de H1, H2 <strong>et</strong> H3 <strong>pour</strong> produire :<br />

sur PULSE_0 : une impulsion de largeur 1/F CLK au de H1<br />

sur PULSE_H : une impulsion de largeur 1/F CLK au ou de H1, H2 ou H3<br />

Le signal PULSE_0 m<strong>et</strong> à zéro de façon synchrone le compteur de secteurs <strong>et</strong> réalise donc la<br />

synchronisation 360°" de l'alimentation du <strong>moteur</strong>.<br />

Le signal PULSE_0 m<strong>et</strong> à zéro de façon synchrone le compteur de position dans un secteur <strong>pour</strong><br />

l'initialiser à chaque détection de secteur.<br />

IMPORTANT : on peut améliorer la fonction de synchronisation en codant les signaux H1, H2 <strong>et</strong> H3<br />

<strong>et</strong> en affecter le compteur de secteurs à chaque transition. Le plus simple serait de remplacer le<br />

compteur par une machine d'états qui produit 3 signaux similaires à H1, H2 <strong>et</strong> H3.<br />

CREMMEL Marcel Page 15/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

7.1.3 Cpt_Sect_SVM<br />

Il est incrémenté au début de chaque secteur grâce au signal PULSE_H.<br />

7.1.4 Cpt_Magn_pos<br />

Compteur 8 bits synchrone à raz synchrone.<br />

La sortie COUT perm<strong>et</strong> de bloquer le compteur quand il atteint 255.<br />

Il est incrémenté à un rythme tel que son état évolue entre 0 <strong>et</strong> une valeur aussi proche que possible de<br />

255 dans un secteur. Le rythme est calculé à la fin de chaque secteur par les fonctions<br />

"Cpt_Mesure_TH", "Periode_H" <strong>et</strong> "Div_prog_16b".<br />

7.1.5 Cpt_Mesure_TH<br />

Ce compteur est incrémenté au rythme de 72kHz grâce au signal EN_72K.<br />

Il est mis à 0 de façon synchrone avec PULSE_H, donc au début de chaque secteur. Son état juste avant<br />

c<strong>et</strong>te raz est donc proportionnel à la durée T SECT du dernier secteur :<br />

Etat final Cpt_Mesure_TH = 72000.T SECT<br />

Exemples : Vitesse de rotation magnétique T SECT Etat final Cpt_Mesure_TH<br />

66,7 tours/mn 150mS 10800<br />

3333 tours/mn 3mS 216<br />

La vitesse de rotation magnétique doit être comprise entre 11 tr/mn <strong>et</strong> 7200 tr/mn <strong>pour</strong> éviter le<br />

dépassement du compteur <strong>et</strong> obtenir un résultat supérieur à 100 (précision meilleure que 1%).<br />

7.1.6 Periode_H<br />

Sa fonction est simplement de mémoriser le résultat 72000.T SECT au moment adéquat.<br />

7.1.7 Div_prog_16b<br />

Il s'agit d'un décompteur synchrone 16 bits à prépositionnement synchrone. L'horloge est le signal<br />

CLK_18M432 de fréquence 18,432MHz.<br />

La sortie COUT passe à "1" quand le compteur est à 0. Sa fréquence est donc de :<br />

FCLK_18M432<br />

18432000 256<br />

FCOUT<br />

<br />

<br />

<br />

72000<br />

TSECT<br />

1<br />

72000 TSECT<br />

TSECT<br />

C<strong>et</strong>te fréquence incrémente le compteur "Cpt_Magn_pos" qui est mis à zéro au début de chaque secteur,<br />

donc avec une périodicité de T SECT .<br />

Ainsi, quand le <strong>moteur</strong> tourne à vitesse constante, le compteur atteint tout juste la valeur 255 à la fin de<br />

chaque secteur, quelle que soit c<strong>et</strong>te vitesse : CQFD.<br />

7.2 ROM_TA<br />

C<strong>et</strong>te ROM de 256 oct<strong>et</strong>s contient la table TA vue au §2.5. Elle est mise à l'échelle :<br />

T <br />

A<br />

π M_POS7..0<br />

π <br />

Table T A :<br />

<br />

256 sin<br />

<br />

<br />

TS<br />

<br />

3 256 3<br />

ROM<br />

<br />

<strong>pour</strong> 0 M_POS[] 255<br />

Extrait du fichier "Table_TA.mif" (adresse à gauche, donnée à droite) :<br />

WIDTH = 8;<br />

DEPTH = 256;<br />

ADDRESS_RADIX = DEC;<br />

DATA_RADIX = DEC;<br />

CONTENT<br />

BEGIN<br />

0 : 222 ;<br />

1 : 221 ;<br />

2 : 221 ;<br />

3 : 220 ;<br />

…<br />

252 : 4 ;<br />

253 : 3 ;<br />

254 : 2 ;<br />

255 : 1 ;<br />

END;<br />

CREMMEL Marcel Page 16/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

7.3 ROM_TB<br />

C<strong>et</strong>te ROM de 256 oct<strong>et</strong>s contient la table TB vue au §2.5. Elle est mise à l'échelle :<br />

T <br />

B M_POS7..0<br />

π <br />

Table T B :<br />

<br />

256<br />

sin<br />

<br />

TS<br />

<br />

256 3<br />

ROM<br />

<br />

<strong>pour</strong> 0 M_POS[] 255<br />

Extrait du fichier "Table_TB.mif" (adresse à gauche, donnée à droite) :<br />

WIDTH = 8;<br />

DEPTH = 256;<br />

ADDRESS_RADIX = DEC;<br />

DATA_RADIX = DEC;<br />

CONTENT<br />

BEGIN<br />

0 : 0 ;<br />

1 : 1 ;<br />

2 : 2 ;<br />

3 : 3 ;<br />

4 : 4 ;<br />

…<br />

250 : 218 ;<br />

251 : 219 ;<br />

252 : 220 ;<br />

253 : 220 ;<br />

254 : 221 ;<br />

255 : 221 ;<br />

END;<br />

7.4 Calc_SVM<br />

C<strong>et</strong>te fonction effectue les calculs décrits dans le tableau du §2.5 <strong>pour</strong> obtenir les 3 rapports cycliques<br />

PWMa, PWMb <strong>et</strong> PWMc. Les calculs dépendent du secteur dans lequel se trouve l'axe magnétique du<br />

<strong>moteur</strong>; c<strong>et</strong>te information est fournie par SECT[2..0].<br />

Dans le tableau du §2.5, les valeurs des rapports cycliques PWMa, PWMb <strong>et</strong> PWMc sont comprises<br />

entre 0 <strong>et</strong> 1. Dans la solution proposée, les rapports cycliques correspondants PWM_R, PWM_Y <strong>et</strong><br />

PWM_B sont des entiers positifs codés sur 8 bits, donc de valeurs comprises entre 0 <strong>et</strong> 255.<br />

subdesign CALC_SVM<br />

(<br />

SECT[2..0]:input;<br />

TA[7..0]:input;<br />

TB[7..0]:input;<br />

PWM_R[7..0]:output;<br />

PWM_Y[7..0]:output;<br />

PWM_B[7..0]:output;<br />

)<br />

variable<br />

T0_x2[7..0]:node;<br />

T0[7..0] :node;<br />

begin<br />

T0_x2[]=255-TA[]-TB[]+1; -- +1 <strong>pour</strong> éviter les dépassements<br />

T0[6..0]=T0_x2[7..1]; T0[7]=GND;<br />

case SECT[] is<br />

when 0 => PWM_R[]=T0[];<br />

PWM_Y[]=T0[]+TA[];<br />

PWM_B[]=255-T0[];<br />

when 1 => PWM_R[]=T0[]+TB[];<br />

PWM_Y[]=T0[];<br />

PWM_B[]=255-T0[];<br />

when 2 => PWM_R[]=255-T0[];<br />

PWM_Y[]=T0[];<br />

PWM_B[]=T0[]+TA[];<br />

when 3 => PWM_R[]=255-T0[];<br />

PWM_Y[]=T0[]+TB[];<br />

PWM_B[]=T0[];<br />

when 4 => PWM_R[]=T0[]+TA[];<br />

CREMMEL Marcel Page 17/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

PWM_Y[]=255-T0[];<br />

PWM_B[]=T0[];<br />

when 5 => PWM_R[]=T0[];<br />

PWM_Y[]=255-T0[];<br />

PWM_B[]=T0[]+TB[];<br />

end case;<br />

end;<br />

7.5 Modulation<br />

La fonction "Modulation" multiplie les valeurs TA[] <strong>et</strong> TB[] (en BN) avec l'indice de modulation M[] <strong>et</strong><br />

réalise donc le réglage de niveau. On ne garde que l'oct<strong>et</strong> de poids fort du résultat.<br />

Multiply_8x8<br />

TA[7..0]<br />

INPUT<br />

VCC<br />

dataa[7..0]<br />

datab[7..0]<br />

inst<br />

result[7..0]<br />

Unsigned<br />

multiplication<br />

OUTPUT<br />

TAM[7..0]<br />

Multiply_8x8<br />

TB[7..0]<br />

M[7..0]<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

dataa[7..0]<br />

datab[7..0]<br />

inst3<br />

result[7..0]<br />

Unsigned<br />

multiplication<br />

OUTPUT<br />

TBM[7..0]<br />

7.6 Limit_3PWM<br />

C<strong>et</strong>te fonction évite d'obtenir les rapports cycliques extrêmes de 0% <strong>et</strong> 100% <strong>et</strong> bloquer le hachage des<br />

courants dans le <strong>moteur</strong>.<br />

subdesign LIMIT_3PWM<br />

(<br />

IN1[7..0]:input;<br />

IN2[7..0]:input;<br />

IN3[7..0]:input;<br />

LIM[5..0]:input;<br />

CLK:input;<br />

EN :input;<br />

OUT1[7..0]:output;<br />

OUT2[7..0]:output;<br />

OUT3[7..0]:output;<br />

)<br />

variable<br />

LIM8[7..0]:node;<br />

OUT1[7..0]:dffe;<br />

OUT2[7..0]:dffe;<br />

OUT3[7..0]:dffe;<br />

begin<br />

LIM8[7..6]=GND; LIM8[5..0]=LIM[5..0];<br />

OUT1[].clk=CLK; OUT1[].ena=EN;<br />

OUT2[].clk=CLK; OUT2[].ena=EN;<br />

OUT3[].clk=CLK; OUT3[].ena=EN;<br />

if IN1[]>255-LIM8[] then OUT1[]=255-LIM8[];<br />

else if IN1[]>=LIM8[] then OUT1[]=IN1[];<br />

else OUT1[]=LIM8[];<br />

end if;<br />

end if;<br />

if IN2[]>255-LIM8[] then OUT2[]=255-LIM8[];<br />

else if IN2[]>=LIM8[] then OUT2[]=IN2[];<br />

else OUT2[]=LIM8[];<br />

end if;<br />

end if;<br />

if IN3[]>255-LIM8[] then OUT3[]=255-LIM8[];<br />

else if IN3[]>=LIM8[] then OUT3[]=IN3[];<br />

CREMMEL Marcel Page 18/25 TS électronique - 31/08/06

end if;<br />

end;<br />

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

end if;<br />

else OUT3[]=LIM8[];<br />

La fonction opère une sorte d'écrêtage sur les 3 entrées :<br />

Si l'entrée est inférieure à LIM[] alors la sortie vaut LIM[]<br />

Si l'entrée est supérieure à 255-LIM[] alors la sortie vaut 255-LIM[]<br />

Dans les autres cas : sortie = entrée<br />

Les sorties sont synchronisées sur l'horloge CLK_18M432 <strong>pour</strong> éviter l'apparition d'états parasites.<br />

8. Generateur_PWM<br />

UD_Counter<br />

CLK_PWM<br />

CLK_EN<br />

PTMR[7..0]<br />

OUTPUT<br />

PTMR[7..0]<br />

inst<br />

Comp_PWM<br />

unsigned compare<br />

Dead_Time<br />

OUTPUT<br />

TEST<br />

PDC1[7..0]<br />

INPUT<br />

VCC<br />

dataa[7..0]<br />

datab[7..0]<br />

inst8<br />

agb<br />

COMP1<br />

CLK_PWM<br />

CLK_EN<br />

DELAY[5..0]<br />

PWM1D<br />

PWM1U<br />

OUTPUT<br />

OUTPUT<br />

PWM1D<br />

PWM1U<br />

Comp_PWM<br />

unsigned compare<br />

inst4<br />

Dead_Time<br />

PDC2[7..0]<br />

INPUT<br />

VCC<br />

dataa[7..0]<br />

datab[7..0]<br />

inst11<br />

agb<br />

COMP1<br />

CLK_PWM<br />

CLK_EN<br />

DELAY[5..0]<br />

PWM1D<br />

PWM1U<br />

OUTPUT<br />

OUTPUT<br />

PWM2D<br />

PWM2U<br />

PDC3[7..0]<br />

DELAY[5..0]<br />

CLK_18M432<br />

CLK_EN<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

Comp_PWM<br />

unsigned compare<br />

dataa[7..0]<br />

datab[7..0]<br />

inst12<br />

agb<br />

C<strong>et</strong>te fonction produit les 6 signaux PWM destinés à commander les 6 transistors des 3 bras de<br />

commutateurs de l'interface de puissance. Les rapports cycliques de ces signaux sont déterminés par les<br />

niveaux des signaux numériques PCD1[] à PCD3[].<br />

Le cœur de la structure est le compteur-décompteur "UD_Counter" qui détermine la période des signaux<br />

PWM <strong>et</strong> la résolution de réglage des rapports cycliques. Elle produit le signal numérique PTMR[] de<br />

forme triangulaire.<br />

Ce signal est comparé aux 3 entrées PCD1[] à PCD3[] par 3 fonctions "Comp_PWM". Les sorties<br />

respectives passent à "1" quand le signal PTMR[] est supérieur à PCDx[].<br />

Ces sorties <strong>pour</strong>raient piloter directement les commutateurs des 3 bras s'ils étaient parfaits.<br />

Malheureusement les transistors qui les constituent ne commutent pas instantanément <strong>et</strong> il faut insérer<br />

des temps morts à chaque transition pendant lesquelles les 2 commutateurs du pont sont simultanément<br />

ouverts. On améliore ainsi considérablement le rendement du bras.<br />

inst2<br />

Dead_Time<br />

inst3<br />

COMP1<br />

CLK_PWM<br />

CLK_EN<br />

DELAY[5..0]<br />

PWM1D<br />

PWM1U<br />

OUTPUT<br />

OUTPUT<br />

PWM3D<br />

PWM3U<br />

CREMMEL Marcel Page 19/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

8.1 UD_Counter<br />

NOT<br />

CLK_PWM<br />

CLK_EN<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

inst<br />

Up_Down_Cpt<br />

updow n<br />

clock<br />

clk_en<br />

up/down<br />

q[7..0]<br />

inst1<br />

Comp_Up<br />

compare<br />

OUTPUT<br />

PTMR[7..0]<br />

dataa[7..0]<br />

datab[]=254<br />

inst12<br />

aeb<br />

SRFF<br />

PRN<br />

S<br />

Q<br />

Comp_Down<br />

compare<br />

R<br />

CLRN<br />

inst14<br />

dataa[7..0]<br />

datab[]=1<br />

aeb<br />

On utilise un compteur-décompteur synchrone dont le mode de fonctionnement est déterminé par l'état<br />

de la bascule RS synchrone :<br />

état "0" : Up_Down_Cpt compte. La bascule est mise à "1" de façon synchrone quand l'état du<br />

compteur est 254. Celui-ci passe alors à 255 avant de décompter.<br />

état "1" : Up_Down_Cpt décompte. La bascule est mise à "0" de façon synchrone quand l'état du<br />

compteur est 1. Celui-ci passe alors à 0 avant de compter.<br />

Conclusion : évolution du compteur : 253-254-255-254-253-252- … 3-2-1-0-1-2-3-…254-255-254-…<br />

Note : le signal CLK_EN ne passe à "1" qu'une période sur 4 de CLK_PWM à cause de la fonction<br />

"Div_4" (voir page §4). La fréquence de comptage-décomptage de Up_Down_Cpt est donc de<br />

18,432MHz/4 = 4,608MHz.<br />

La fréquence du signal numérique PTMP[] est donc de 4,608MHz/(254*2)=9071Hz. Les signaux PWM<br />

ont la même fréquence : valeur satisfaisante.<br />

8.2 Comparaisons : relevés expérimentaux<br />

inst13<br />

PDC1[] proche de 128<br />

Sortie du 1° comparateur<br />

PTMP[] converti par le CNA de la<br />

carte d'étude<br />

CREMMEL Marcel Page 20/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

PDC1[] proche de 255<br />

Sortie du 1° comparateur<br />

PTMP[] converti par le CNA de la<br />

carte d'étude<br />

PDC1[] proche de 0<br />

Sortie du 1° comparateur<br />

PTMP[] converti par le CNA de la<br />

carte d'étude<br />

8.3 Dead_Time<br />

Schéma original<br />

NOT<br />

inst6<br />

AND2<br />

DFFE<br />

PRN<br />

D Q<br />

OUTPUT<br />

PWM1D<br />

COMP1<br />

CLK_PWM<br />

CLK_EN<br />

DELAY[5..0]<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

DFFE<br />

PRN<br />

D Q<br />

ENA<br />

CLRN<br />

inst11<br />

XOR<br />

inst1<br />

Dead_Time_Cpt<br />

sload<br />

data[5..0]<br />

down counter<br />

inst7<br />

AND2<br />

inst3<br />

ENA<br />

CLRN<br />

inst9<br />

DFFE<br />

PRN<br />

D Q<br />

ENA<br />

CLRN<br />

inst10<br />

OUTPUT<br />

PWM1U<br />

clock<br />

clk_en<br />

cnt_en<br />

q[5..0]<br />

cout<br />

inst2<br />

NOT<br />

inst5<br />

CREMMEL Marcel Page 21/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

Schéma de test<br />

OUTPUT<br />

SLOAD<br />

OUTPUT<br />

COMP1R<br />

OUTPUT<br />

D1<br />

NOT<br />

inst6<br />

AND2<br />

DFFE<br />

PRN<br />

D Q<br />

OUTPUT<br />

PWM1D<br />

COMP1<br />

CLK_PWM<br />

CLK_EN<br />

DELAY[5..0]<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

INPUT<br />

VCC<br />

DFFE<br />

PRN<br />

D Q<br />

ENA<br />

CLRN<br />

inst11<br />

XOR<br />

inst1<br />

Dead_Time_Cpt<br />

sload<br />

data[5..0]<br />

down counter<br />

inst7<br />

AND2<br />

inst3<br />

ENA<br />

CLRN<br />

inst9<br />

DFFE<br />

PRN<br />

D Q<br />

ENA<br />

CLRN<br />

inst10<br />

OUTPUT<br />

OUTPUT<br />

PWM1U<br />

D2<br />

clock<br />

clk_en<br />

cnt_en<br />

q[5..0]<br />

cout<br />

OUTPUT<br />

OUTPUT<br />

Q[5..0]<br />

COUT<br />

inst2<br />

NOT<br />

inst5<br />

Résultats de simulation :<br />

Pour simplifier, on a utilisé une horloge CLK_PWM de 4MHz avec CLK_EN constamment à "1".<br />

Le décompteur "Dead_Time_Cpt" est monté en monostable à déclenchement synchrone. Le<br />

déclenchement est provoqué à chaque transition du signal COMP1 par le signal SLOAD produit par la<br />

1° bascule D <strong>et</strong> la porte XOR associée.<br />

Le décompteur est prépositionné à la valeur DELAY[] au déclenchement du monostable. La sortie<br />

COUT passe alors à "0" jusqu'à ce que le compteur atteigne l'état 0 : la durée à l'état bas de COUT est<br />

de DELAY[]xPériode_CLKPWM.<br />

Le signal COUT est combiné avec COMP1R <strong>pour</strong> produire les signaux D1 <strong>et</strong> D2 conformes au résultat<br />

attendu : temps mort entre les transitions (qd D1 <strong>et</strong> D2 sont à "0").<br />

Les signaux D1 <strong>et</strong> D2 sont synchronisés avec l'horloge <strong>pour</strong> supprimer les "glitchs".<br />

Le temps mort dure DELAY[] périodes d'horloge.<br />

Note : le r<strong>et</strong>ard entre COMP1 <strong>et</strong> les signaux PWM est sans eff<strong>et</strong> car tous les 6 signaux PWM sont<br />

r<strong>et</strong>ardés de façon identique.<br />

Attention : la structure ne fonctionne plus si la durée du signal COMP1 est plus courte que le temps<br />

mort désiré.<br />

CREMMEL Marcel Page 22/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

Relevés expérimentaux (DELAY[]=2) :<br />

COMP1<br />

PWM1D<br />

PWM1U<br />

On mesure un temps mort de 435nS, conforme avec la valeur DELAY[] : 2/4,608MHz<br />

Le r<strong>et</strong>ard de PWM1D est dû aux bascules D de synchronisation.<br />

COMP1<br />

PWM1D<br />

PWM1U<br />

Résultats conformes.<br />

CREMMEL Marcel Page 23/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

Une période complète (dans les mêmes conditions) :<br />

PWM1D<br />

PWM1U<br />

PTMR[] converti par le CNA de la<br />

carte d'étude<br />

9. Résultat final (avant interface de puissance)<br />

Les 3 sorties PWM1D à PWM3D de l'EPLD sont appliquées à 3 filtres passe-bas du 1° ordre (R=10K,<br />

C=100nF) de fréquence de coupure Fc=159Hz. On observe ainsi les valeurs moyennes de ces 3 signaux.<br />

Conditions :<br />

LIMIT[]=4<br />

DELAY[]=2<br />

Synchro externe sur de la sortie<br />

H1<br />

Bleu = PWM3<br />

Rouge = PWM2<br />

Noir = PWM1<br />

La fréquence des 3 phases est<br />

suffisamment basse (1,092Hz) <strong>pour</strong><br />

passer le filtre passe-bas sans<br />

atténuation.<br />

Le résultat est conforme !<br />

CREMMEL Marcel Page 24/25 TS électronique - 31/08/06

Application maqu<strong>et</strong>te d'étude EP10K20 – Générateur SVM <strong>triphasé</strong> <strong>pour</strong> <strong>moteur</strong> BLDC<br />

Relevés des tensions différentielles:<br />

PWM1-PWM2<br />

PMW3-PWM2<br />

PWM1-PWM3<br />

Sensibilité : 1 V/div<br />

CREMMEL Marcel Page 25/25 TS électronique - 31/08/06