Programmeerbare logica vvkso - Docweb

Programmeerbare logica vvkso - Docweb

Programmeerbare logica vvkso - Docweb

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

J<br />

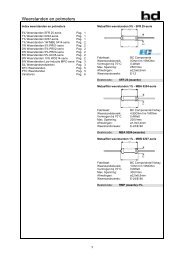

In bovenstaande ‘flowchart’ is de conventionele werkgang weergegeven voor het ontwikkelen van digitale<br />

logische schakelingen. De beschreven werkwijze beperkt zich tot het ontwerpen van niet tijdgebonden,<br />

combinatorische schakelingen. Dit volstaat om de vergelijking met de vernieuwde aanpak bij het ontwerpen<br />

met programmeerbare logische bouwstenen (zie 3.2) te begrijpen.Indien combinatorische schakelingen<br />

worden uitgebreid met geheugenelementen en andere bouwstenen waarvan de toestand, synchroon of<br />

asynchroon, verandert onder besturing van een kloksignaal spreekt men van sequentiële schakelingen of<br />

toestandsmachines.<br />

Deze methode maakt deel uit van de leerstof van de tweede graad (vak ‘Elektronica en lab’, module<br />

digitale technieken) en van de derde graad (vak ‘Digitale technieken en lab’).Daarom is er geen uitgewerkt<br />

voorbeeld opgenomen in deze tekst.<br />

De gewenste functie wordt beschreven en in een waarheidstabel samengevat. Uit de tabel worden<br />

logische vergelijkingen afgeleid. Er wordt getracht deze vergelijkingen te vereenvoudigen. Dit kan<br />

gebeuren :<br />

- door middel van de wetten van de schakelalgebra van Boole: basiswetten, commutatieve-,<br />

associatieve-, distributieve wetten, wetten van De Morgan ;<br />

- door middel van een grafische methode: Karnaugh-kaarten.<br />

De eenvoudigste oplossing – bijvoorbeeld een som van producttermen (SOP) - wordt nu getekend met<br />

standaardcomponenten (discrete <strong>logica</strong>) en moet het eenvoudigste schema opleveren. In dit schema tracht<br />

men te minimaliseren en dus zo weinig mogelijk componenten te gebruiken. Meestal werkend van uitgang<br />

naar ingang kan men oplossingen zoeken met uitsluitend fundamentele poorten (EN, OF, NIET,<br />

EXOF), uitsluitend NOF-poorten of uitsluitend NEN-poorten. Nadien wordt de schakeling – indien mogelijk<br />

– gesimuleerd en /of wordt er een prototype gebouwd en getest. Wanneer de werking niet correct<br />

wordt bevonden dient men de werkgang geheel of gedeeltelijk opnieuw te doorlopen tot het gewenste resultaat<br />

is bereikt.<br />

3.2 Automatische synthese van programmeerbare <strong>logica</strong><br />

Het beschrijven van de functionaliteit van een schakeling en de wijze van ontwerpen wijkt bij programmeerbare<br />

<strong>logica</strong> af van het conventioneel (‘traditioneel’) ontwerpen. Een grondige basiskennis van de<br />

‘klassieke’ digitale technieken blijft voor PLD-ontwerp echter noodzakelijk. <strong>Programmeerbare</strong> <strong>logica</strong><br />

vraagt het veranderen van een ‘ontwerpcultuur’en dat is niet altijd eenvoudig. De PC-ontwikkelingssoftware<br />

voor PLD’s blijft het werken met elektronische schema's, waarheidstabellen en logische vergelijkingen<br />

ondersteunen. Het beschrijven van de functies van een schakeling kan echter ook veel compacter,<br />

leesbaarder en documenteerbaarder met taalconstructies zoals men die ook vindt in hogere programmeertalen<br />

zoals Pascal en C. Bedenk echter dat een dergelijke taal in dit geval niet dient om softwarematig<br />

een schakel- of stuurprobleem op te lossen: dat doen de programma’s voor microcontrollers,<br />

microprocessoren en PLC’s . Om de schakeling zelf te laten werken is het betreffende programma niet<br />

meer nodig. Een programma om een PLD te configureren beschrijft via taalelementen hoe een hardwareschakeling<br />

in een chip moet werken. Daarom noemt men een dergelijke taal een ‘Hardware Description<br />

Language’ of HDL. Ook al hebben we een beschrijving via schema of taal, uiteindelijk moeten we toch<br />

logische vergelijkingen hebben (SOP) om die te implementeren in een PLD-architectuur zoals die reeds<br />

eerder werd beschreven. De speciaal hiervoor ontwikkelde EDA-software (CAD) is in staat de vertaling<br />

van de beschrijving naar vergelijkingen uit te voeren, waarbij bovendien <strong>logica</strong>-optimalisering zal<br />

plaatsvinden: minimaliseren van het aantal vergelijkingen en het aantal poorten, wat leidt tot een ‘zuinig’<br />

gebruik van de cellen van een PLD. Men noemt dit automatisch genereren van een schakeling vanuit de<br />

beschrijving: automatische <strong>logica</strong>synthese. Automatische <strong>logica</strong>synthese raakt een aantal aspecten van het<br />

ontwerpen. Het is niet een simpele ‘druk op de knop’ die het ontwerp oplevert. Gebruik maken van deze<br />

moderne programmatuur vraagt daarentegen wel enig inzicht in de toegepaste principes.<br />

Het ontwerpen van PLD's via automatische <strong>logica</strong>synthese, verloopt via de werkgang uit de volgende<br />

‘flowchart’:<br />

10