Programmeerbare logica vvkso - Docweb

Programmeerbare logica vvkso - Docweb

Programmeerbare logica vvkso - Docweb

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

PROGRAMMEERBARE LOGICA<br />

1 ASIC’s, PLD’s<br />

1.1 Begrippen<br />

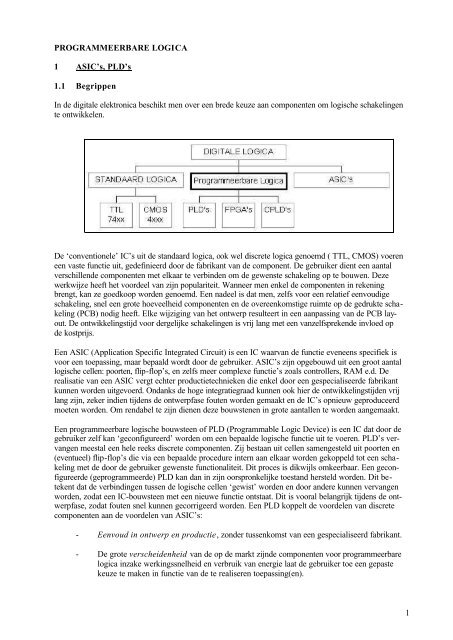

In de digitale elektronica beschikt men over een brede keuze aan componenten om logische schakelingen<br />

te ontwikkelen.<br />

De ‘conventionele’ IC’s uit de standaard <strong>logica</strong>, ook wel discrete <strong>logica</strong> genoemd ( TTL, CMOS) voeren<br />

een vaste functie uit, gedefinieerd door de fabrikant van de component. De gebruiker dient een aantal<br />

verschillende componenten met elkaar te verbinden om de gewenste schakeling op te bouwen. Deze<br />

werkwijze heeft het voordeel van zijn populariteit. Wanneer men enkel de componenten in rekening<br />

brengt, kan ze goedkoop worden genoemd. Een nadeel is dat men, zelfs voor een relatief eenvoudige<br />

schakeling, snel een grote hoeveelheid componenten en de overeenkomstige ruimte op de gedrukte schakeling<br />

(PCB) nodig heeft. Elke wijziging van het ontwerp resulteert in een aanpassing van de PCB layout.<br />

De ontwikkelingstijd voor dergelijke schakelingen is vrij lang met een vanzelfsprekende invloed op<br />

de kostprijs.<br />

Een ASIC (Application Specific Integrated Circuit) is een IC waarvan de functie eveneens specifiek is<br />

voor een toepassing, maar bepaald wordt door de gebruiker. ASIC’s zijn opgebouwd uit een groot aantal<br />

logische cellen: poorten, flip-flop’s, en zelfs meer complexe functie’s zoals controllers, RAM e.d. De<br />

realisatie van een ASIC vergt echter productietechnieken die enkel door een gespecialiseerde fabrikant<br />

kunnen worden uitgevoerd. Ondanks de hoge integratiegraad kunnen ook hier de ontwikkelingstijden vrij<br />

lang zijn, zeker indien tijdens de ontwerpfase fouten worden gemaakt en de IC’s opnieuw geproduceerd<br />

moeten worden. Om rendabel te zijn dienen deze bouwstenen in grote aantallen te worden aangemaakt.<br />

Een programmeerbare logische bouwsteen of PLD (Programmable Logic Device) is een IC dat door de<br />

gebruiker zelf kan ‘geconfigureerd’ worden om een bepaalde logische functie uit te voeren. PLD’s vervangen<br />

meestal een hele reeks discrete componenten. Zij bestaan uit cellen samengesteld uit poorten en<br />

(eventueel) flip-flop’s die via een bepaalde procedure intern aan elkaar worden gekoppeld tot een schakeling<br />

met de door de gebruiker gewenste functionaliteit. Dit proces is dikwijls omkeerbaar. Een geconfigureerde<br />

(geprogrammeerde) PLD kan dan in zijn oorspronkelijke toestand hersteld worden. Dit betekent<br />

dat de verbindingen tussen de logische cellen ‘gewist’ worden en door andere kunnen vervangen<br />

worden, zodat een IC-bouwsteen met een nieuwe functie ontstaat. Dit is vooral belangrijk tijdens de ontwerpfase,<br />

zodat fouten snel kunnen gecorrigeerd worden. Een PLD koppelt de voordelen van discrete<br />

componenten aan de voordelen van ASIC’s:<br />

- Eenvoud in ontwerp en productie, zonder tussenkomst van een gespecialiseerd fabrikant.<br />

- De grote verscheidenheid van de op de markt zijnde componenten voor programmeerbare<br />

<strong>logica</strong> inzake werkingssnelheid en verbruik van energie laat de gebruiker toe een gepaste<br />

keuze te maken in functie van de te realiseren toepassing(en).<br />

1

- Eenvoudige gedrukte schakeling. De PCB is sterk vereenvoudigd omdat het aantal<br />

bouwstenen vermindert. Bovendien bieden PLD’s een vrij grote flexibiliteit in het plaatsen<br />

van in- en uit-gangspinnen. Daar de meeste functies van de schakeling intern worden<br />

gerealiseerd, kan men beginnen met het ontwikkelen van de PCB lay-out op het ogenblik dat<br />

de in- en uitgangen gekend zijn. De werkelijke details van het inwendige van een PLD<br />

kunnen dan onafhankelijk van het eind-ontwerp worden uitgewerkt. Noodzakelijke<br />

aanpassingen kunnen uitgevoerd worden binnen de PLD en hebben geen invloed meer op de<br />

PCB lay-out.<br />

- Snelheid is één van de hoofdredenen waarom ontwerpers PLD-bouwstenen gebruiken. De<br />

PLD-elementen kunnen dikwijls betere prestaties leveren dan de snelste discrete <strong>logica</strong>. De<br />

looptijd van de signalen is kort vanwege de zeer korte verbindingen binnen de bouwsteen.<br />

- Daar PLD’s worden gebruikt om meerdere discrete schakelingen te vervangen, zal het<br />

energie-verbruik van een ontwerp zeker lager zijn dan dat van de gecombineerde discrete<br />

componenten samen.<br />

- De betrouwbaarheid is een gebied waar meer en meer zorg aan besteed wordt. De ontwerpen<br />

worden steeds groter en complexer en dit heeft meerdere chips voor gevolg. Meerdere chips<br />

be-tekenen een kleinere betrouwbaarheid van het ontwerp, er zijn "meer dingen die verkeerd<br />

kunnen gaan". Een oplossing om het aantal chips in een systeem te reduceren zal bijdragen<br />

tot een grotere betrouwbaarheid. Een benadering met programmeerbare <strong>logica</strong> kan een<br />

betrouwbaarder oplossing bieden, daar het ontwerp een kleiner aantal elementen vereist.<br />

Door een vermindering van het aantal chips kan men kleinere PCB's gebruiken. Dit<br />

vermindert overspraak en andere potentiële stoorbronnen waardoor het hele ontwerp mooier<br />

en betrouwbaarder wordt.<br />

- Voor ieder praktisch ontwerp moeten de kosten binnen de perken blijven. De kost is bijna<br />

altijd een factor bij het overwegen van een nieuw ontwerp of bij een ontwerpverandering.<br />

Maar, een be-rekening van de totale ontwerpkost kan misleidend zijn als men niet alle<br />

aspecten ervan beschouwt. Veel van de kosten zijn moeilijk in te schatten. Het is<br />

bijvoorbeeld moeilijk het marktverlies van het produkt, te wijten aan een te late introductie,<br />

te beoordelen. De grootste voordelen tegenover een discreet ontwerp bekomt men door het<br />

feit dat een enkele PLD verschillende discrete chips kan vervangen. De ingenomen ruimte<br />

op een gedrukte schakeling wordt gemiddeld met 25% vermin-derd als men met PLD's<br />

werkt.<br />

- De manier van ontwerpen wordt sterk vereenvoudigd door de ontwerpmiddelen die nu op de<br />

markt zijn. Ontwerpsoftware en programmeerbare componenten laten toe ontwerpen te<br />

implementeren met een minimum aan tijdverlies. Simulatie laat ons toe het ontwerp<br />

functioneel te testen vooraleer het element geprogrammeerd wordt.<br />

Om al deze redenen zal de programmeerbare <strong>logica</strong> meer en meer de voorkeur krijgen boven de klassieke<br />

oplossingen met discrete componenten.<br />

Wat de verdere indeling van de programmeerbare logische bouwstenen in PLD’s, FPGA’s (Field Programmable<br />

Gate Arrays) en CPLD’s (Complex Programmable Logic Devic es ) betreft onthouden we<br />

enkel dat dit te maken heeft met de interne structuur, de oplopende inwendige complexiteit en het steeds<br />

groter wordende aantal logische cellen per IC in de vermelde volgorde van PLD, over FPGA tot CPLD.<br />

Deze indeling kan nog meer worden verfijnd en verschilt soms per fabrikant.<br />

1.2 PLD-familie’s<br />

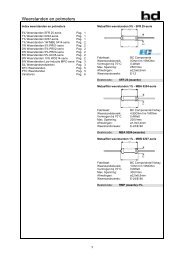

Men kan de programmeerbare logische bouwstenen volgens allerlei criteria indelen. We beperken ons<br />

hier tot een indeling volgens de technologie waarmee de interne logische cellen met elkaar worden verbonden<br />

tot een schakeling. Bij PLD's worden de logische functies gerealiseerd door het "op elektrische<br />

wijze" doorverbinden (al dan niet omkeerbaar) van de cellen die in de chip aanwezig zijn. Dit kan echter<br />

2

ook gebeuren door het verbreken van bestaande, niet gewenste verbindingen. Men onderscheidt daarbij<br />

een aantal verschillende verbindingsvormen.<br />

- Bipolaire fuse-based verbindingen<br />

Bij deze techniek worden de functies geprogrammeerd door alle niet gewenste verbindingen op<br />

elektrische wijze "door te smelten" zoals een zekering. De eventueel te verbreken verbindingen<br />

zijn gerealiseerd als weerstandselement of als PN-overgang (diode, transistor). Dit onomkeerbare<br />

principe vindt men onder andere terug bij PROM’s (zie ‘geheugens’) en PAL's (Programmable<br />

Array Logic).<br />

- Floating gate verbindingen<br />

In dit geval gebruikt men erasable (wisbare) cellen (zoals bij bepaalde geheugen-IC’s) om de interne<br />

verbindingen te realiseren. Correctie van fouten of het maken van een nieuwe toepassing met<br />

dezelfde chip is hier eenvoudig. Bij de EPLD’s (Erasable Programmable Logic Device) wordt de<br />

oorspronkelijke toestand hersteld door belichting met UV-licht ( zoals bij EPROM geheugens). Bij<br />

de EEPLD’s ( Electrically Erasable PLD’s) gebeurt dit langs elektrische weg (zoals bij EEPROM<br />

geheugens) en kan het (her)configureren of (her)programmeren eventueel zelfs gebeuren terwijl het<br />

IC in de (niet actieve) schakeling is opgenomen (in-circuit programming).<br />

3

- Static-RAM verbindingen<br />

Bij sommige PLD's worden de verbindingen gerealiseerd door de toestanden (0 of 1) van statische<br />

RAM-geheugencellen. Dit geeft geheel nieuwe mogelijkheden. Door dergelijke PLD's samen met<br />

een microcontroller of microprocessor in een schakeling op te nemen, is het mogelijk deze schakeling<br />

dynamisch aan te passen aan de toepassing. De <strong>logica</strong> kan zeer snel van aard veranderen, zonder<br />

dat er ook maar één enkele wijziging aan de bedrading gebeurt. De <strong>logica</strong>schakeling wordt geladen<br />

vanuit een (eventueel extern) processorgeheugen en zal onmiddellijk de nieuwe functie<br />

realiseren.<br />

A B C<br />

2 EENVOUDIGE PLD-ARCHITECTUREN<br />

2.1 Combinatorisch<br />

4

Oefening<br />

- PAL-architectuur<br />

Bij nadere studie van het grote aanbod PLD's, die vaak slechts op enkele details verschillen, blijkt<br />

dat het in feite gaat om een beperkt aantal concepten en varianten daarvan. De databoeken van<br />

PLD-leveranciers tonen de interne opbouw van de componenten in de vorm van een principeschema.<br />

De kunst bestaat er in om, in deze steeds complexere schema's, een basisconcept en de<br />

daarop aangebrachte extra voorzieningen te herkennen. We beperken ons tot het veel gebruikte<br />

PAL-concept. In bovenstaande figuur lijken de EN-poorten slechts één ingangslijn te hebben.<br />

Deze lijn refereert echter naar de productlijn. De lijnen die loodrecht op de productlijnen van de<br />

EN-poorten staan vormen de mogelijke ingangen. Deze figuur toont een PAL-cel met acht mogelijke<br />

producttermen met elk tweeëndertig mogelijke ingangen, afkomstig van zestien al dan niet geïnverteerde<br />

signalen. Er wordt hier, symbolisch, slechts één ingang van de cel voorgesteld. Een PLD bevat<br />

steeds meerdere van dergelijke cellen, ook wel macrocellen genoemd, met gemeenschappelijke ingangslijnen.<br />

De PAL-architectuur wordt veel toegepast, onder andere in EPLD’s en EEPLD’s. Bij<br />

deze architectuur is de EN -matrix (AND-array) programmeerbaar. Op elke EN-poort worden alle ingangsvariabelen<br />

aangeboden. Met behulp van de te maken of te verbreken verbindingen kan, door<br />

programmering, worden bepaald welke signalen door een EN-poort gebruikt worden. De uitgang van<br />

elke EN-poort komt op een OF-poort terecht (som van producttermen = sum of products = SOP). De<br />

producttermen zijn dus gegroepeerd als vaste ingangen van een OF-poort. Het aantal ingangen van de<br />

OF-poort beperkt het maximaal aantal te sommeren producttermen. In een PLD met PAL-architectuur<br />

worden dus door de programmering de gewenste producttermen vastgelegd. Alle producttermen die<br />

dan aanwezig zijn worden naar buiten gevoerd.<br />

Een grondstofsilo wordt gevoed via drie transportbanden. Een van deze transportbanden levert twee<br />

kubieke meter per minuut, de andere twee leveren slechts één kubieke meter per minuut. Wanneer de silo<br />

gevoed wordt met meer dan twee kubieke meter grondstof per minuut, moet een digitale schakeling een<br />

alarmsignaal geven. Op elke transportband staat een sensor die een actief hoog signaal afgeeft wanneer<br />

de betreffende band in werking is. Om het alarm te activeren is eveneens een actief hoog signaal noodzakelijk.<br />

Duidt op de bovenstaande PAL-configuratie (met slechts één cel) de vereiste in- en uitgangen<br />

aan en de verbindingen die moeten geprogrammeerd worden om met dit IC het gestelde probleem op te<br />

lossen (teken nog de nodige ingangen extra).<br />

Ingang I 0 : signaal van de sensor van transportband 1 (twee kubieke meter per minuut)<br />

Ingang I 1 : signaal van de sensor van transportband 2 (één kubieke meter per minuut)<br />

Ingang I 2 : signaal van de sensor van transportband 3 (één kubieke meter per minuut)<br />

Uitgang O : alarmsignaal<br />

INGANGEN UITGANG<br />

I 0 I 1 I 2 O<br />

0 0 0 0<br />

0 0 1 0<br />

0 1 0 0<br />

0 1 1 0<br />

1 0 0 0<br />

1 0 1 1<br />

1 1 0 1<br />

1 1 1 1<br />

5

SOP : O = (I 0 EN I 1 ) OF (I 0 EN I 2 ) OF (I 0 EN I 1 EN I 2)<br />

- Enkele voorbeelden van extra voorzieningen<br />

In deze macrocel kan een productterm onmiddellijk de uitgang controleren. De productterm wordt<br />

gebruikt om een 3-state buffer te sturen, die op zijn beurt de sommatieterm doorschakelt naar de<br />

betreffende uitgangspin. De uitgang is eveneens teruggekoppeld naar de EN-matrix. De I/O pin<br />

wordt dus gestuurd wanneer de 3-state poort geselecteerd is. De I/O pin is zelf een ingang van de<br />

EN-matrix wanneer de 3-state poort in de hoog-impedantie-toestand verkeert. Deze eigenschap kan<br />

gebruikt worden om I/O functies op beschikbare I/O-pinnen te zetten of om bidirectionele uitgangspinnen<br />

te realiseren. Dit noemt men een cel met programmeerbare I/O.<br />

In bovenstaande figuur vormen de uitgangen van de OF-poorten van het IC, de ingangen van NORpoorten,<br />

die als tweede ingang een programeerbare logische 0 of logische 1 hebben. Op deze<br />

manier kan men de polariteit van de uitgangen controleren.<br />

6

2.2 Sequentieel<br />

Wanneer aan de uitgang van elke PLD-cel met PAL-architectuur een intern geheugenelement (flipflop<br />

of register met klok-ingang) is verbonden wordt het mogelijk om tijdgebonden, sequentiële<br />

toepassingen te ontwikkelen. In bovenstaande figuur is – als voorbeeld – de macrocel van een<br />

CPLD-component van het productterm-type voorgesteld. De cel behoort tot een EEPLD uit de<br />

familie ‘MAX 7000S’ van de fabrikant ‘Altera’. Deze CPLD-familie bevat, naargelang het type, 32<br />

tot 256 van dergelijke macrocellen, het equivalent van 600 tot 20000 poorten. Elke macrocel bevat<br />

vijf programmeerbare EN-poorten (producttermen) per OF-poort. De OF-poort heeft een, via de<br />

ingangsarray programmeerbare polariteit (NOR-poort). De combinatorische uitgang wordt gevolgd<br />

door een programmeerbare flip-flop. Deze flip-flop kan echter, door een programmeerbare<br />

‘bypass’ overbrugd worden. De betreffende cel is dan enkel voor combinatorische toepassingen<br />

geschikt. De celuitgang (combinatorisch of sequentieel) is via een ‘I/O-control block’ met programmeerbare<br />

TRI-state buffer teruggekoppeld naar de ingangsarray, zoals in het voorbeeld van<br />

pagina 6 (programmeerbare I/O).<br />

Elke macrocel kan een aantal extra producttermen (indien vijf niet volstaan) ‘lenen’ van andere<br />

macrocellen in de chip:<br />

- via ‘parallel logic expanders’ van cellen uit hetzelfde LAB (‘Logic Array Block’);<br />

- via ‘shared logic expanders’ van cellen uit andere LAB’s, langs de PIA (‘Programmable<br />

Interconnect Array’).<br />

Voorbeeld<br />

De flip-flop bevat clock-, enable-, preset- en clear-functies en kan geprogrammeerd worden als<br />

D-flip-flop, T-flip-flop, JK-flip-flop of SR-latch. De clock- en clear-ingangen kunnen zowel synchroon<br />

(Global Clock en Global Clear) als asynchroon, via de producttermen geprogrammeerd<br />

worden.<br />

De macrocellen van deze EPLD’s worden – zoals in onderstaande figuur - gecombineerd in<br />

groepen van zestien, in de reeds vermelde ‘Logic Array Blocks’ of LAB’s. De eveneens reeds<br />

7

vermelde ‘Programmable Inter-connect Array’ of PIA, zorgt voor de interne verdeling van de<br />

signalen tussen de LAB’s en de koppeling met de in- en uitgangspinnen via de ‘I/O control blocks’.<br />

De beschreven architectuur van de programmeerbare logische bouwsteen EPM7128S van Altera is<br />

enkel geldig als voorbeeld. De architecturen van andere PLD-families van verschillende fabrikanten<br />

zijn verschillend maar gelijkend.<br />

Oefening<br />

Ontwerp een quizschakeling voor twee kandidaten.<br />

Ingangen: drukknoppen C1en C2 voor de kandidaten en QM voor ‘reset’ door de quizmaster<br />

(actief hoog)<br />

Uitgangen: lampen L1 voor kandidaat 1 en L2 voor kandidaat 2 (actief hoog)<br />

Wanneer beide kandidaten gelijktijdig drukken mag geen van beide lampen oplichten. Wanneer één<br />

van beide lampen oplicht, mag geen enkele drukknop van een kandidaat nog effect hebben, tenzij<br />

de quizmaster een ‘reset’ heeft gegeven. Bij dergelijke ‘reset’ doven beide lampen. Gebruik het<br />

8

schema van twee PLD-macrocellen van het beschreven PAL-type met D-flip-flop’s en duidt de door<br />

programmatie van het IC te maken verbindingen daarop aan.<br />

3 ONTWERPMETHODES<br />

3.1 Conventioneel<br />

VEREENVOUDIGEN<br />

MINIMALISEREN<br />

N<br />

N<br />

N<br />

BEGIN<br />

FUNCTIEBESCHRIJVING<br />

WAARHEIDSTABEL<br />

LOGISCHE VERGELIJKINGEN<br />

EENVOUDIGSTE<br />

OPLOSSING :<br />

SOP<br />

SCHEMA MET<br />

DISCRETE LOGICA<br />

KLEINSTE<br />

AANTAL<br />

COMPONENTEN<br />

SIMULATIE / PROTOTYPE<br />

J<br />

J<br />

CORRECTE<br />

WERKING<br />

EINDE<br />

9

J<br />

In bovenstaande ‘flowchart’ is de conventionele werkgang weergegeven voor het ontwikkelen van digitale<br />

logische schakelingen. De beschreven werkwijze beperkt zich tot het ontwerpen van niet tijdgebonden,<br />

combinatorische schakelingen. Dit volstaat om de vergelijking met de vernieuwde aanpak bij het ontwerpen<br />

met programmeerbare logische bouwstenen (zie 3.2) te begrijpen.Indien combinatorische schakelingen<br />

worden uitgebreid met geheugenelementen en andere bouwstenen waarvan de toestand, synchroon of<br />

asynchroon, verandert onder besturing van een kloksignaal spreekt men van sequentiële schakelingen of<br />

toestandsmachines.<br />

Deze methode maakt deel uit van de leerstof van de tweede graad (vak ‘Elektronica en lab’, module<br />

digitale technieken) en van de derde graad (vak ‘Digitale technieken en lab’).Daarom is er geen uitgewerkt<br />

voorbeeld opgenomen in deze tekst.<br />

De gewenste functie wordt beschreven en in een waarheidstabel samengevat. Uit de tabel worden<br />

logische vergelijkingen afgeleid. Er wordt getracht deze vergelijkingen te vereenvoudigen. Dit kan<br />

gebeuren :<br />

- door middel van de wetten van de schakelalgebra van Boole: basiswetten, commutatieve-,<br />

associatieve-, distributieve wetten, wetten van De Morgan ;<br />

- door middel van een grafische methode: Karnaugh-kaarten.<br />

De eenvoudigste oplossing – bijvoorbeeld een som van producttermen (SOP) - wordt nu getekend met<br />

standaardcomponenten (discrete <strong>logica</strong>) en moet het eenvoudigste schema opleveren. In dit schema tracht<br />

men te minimaliseren en dus zo weinig mogelijk componenten te gebruiken. Meestal werkend van uitgang<br />

naar ingang kan men oplossingen zoeken met uitsluitend fundamentele poorten (EN, OF, NIET,<br />

EXOF), uitsluitend NOF-poorten of uitsluitend NEN-poorten. Nadien wordt de schakeling – indien mogelijk<br />

– gesimuleerd en /of wordt er een prototype gebouwd en getest. Wanneer de werking niet correct<br />

wordt bevonden dient men de werkgang geheel of gedeeltelijk opnieuw te doorlopen tot het gewenste resultaat<br />

is bereikt.<br />

3.2 Automatische synthese van programmeerbare <strong>logica</strong><br />

Het beschrijven van de functionaliteit van een schakeling en de wijze van ontwerpen wijkt bij programmeerbare<br />

<strong>logica</strong> af van het conventioneel (‘traditioneel’) ontwerpen. Een grondige basiskennis van de<br />

‘klassieke’ digitale technieken blijft voor PLD-ontwerp echter noodzakelijk. <strong>Programmeerbare</strong> <strong>logica</strong><br />

vraagt het veranderen van een ‘ontwerpcultuur’en dat is niet altijd eenvoudig. De PC-ontwikkelingssoftware<br />

voor PLD’s blijft het werken met elektronische schema's, waarheidstabellen en logische vergelijkingen<br />

ondersteunen. Het beschrijven van de functies van een schakeling kan echter ook veel compacter,<br />

leesbaarder en documenteerbaarder met taalconstructies zoals men die ook vindt in hogere programmeertalen<br />

zoals Pascal en C. Bedenk echter dat een dergelijke taal in dit geval niet dient om softwarematig<br />

een schakel- of stuurprobleem op te lossen: dat doen de programma’s voor microcontrollers,<br />

microprocessoren en PLC’s . Om de schakeling zelf te laten werken is het betreffende programma niet<br />

meer nodig. Een programma om een PLD te configureren beschrijft via taalelementen hoe een hardwareschakeling<br />

in een chip moet werken. Daarom noemt men een dergelijke taal een ‘Hardware Description<br />

Language’ of HDL. Ook al hebben we een beschrijving via schema of taal, uiteindelijk moeten we toch<br />

logische vergelijkingen hebben (SOP) om die te implementeren in een PLD-architectuur zoals die reeds<br />

eerder werd beschreven. De speciaal hiervoor ontwikkelde EDA-software (CAD) is in staat de vertaling<br />

van de beschrijving naar vergelijkingen uit te voeren, waarbij bovendien <strong>logica</strong>-optimalisering zal<br />

plaatsvinden: minimaliseren van het aantal vergelijkingen en het aantal poorten, wat leidt tot een ‘zuinig’<br />

gebruik van de cellen van een PLD. Men noemt dit automatisch genereren van een schakeling vanuit de<br />

beschrijving: automatische <strong>logica</strong>synthese. Automatische <strong>logica</strong>synthese raakt een aantal aspecten van het<br />

ontwerpen. Het is niet een simpele ‘druk op de knop’ die het ontwerp oplevert. Gebruik maken van deze<br />

moderne programmatuur vraagt daarentegen wel enig inzicht in de toegepaste principes.<br />

Het ontwerpen van PLD's via automatische <strong>logica</strong>synthese, verloopt via de werkgang uit de volgende<br />

‘flowchart’:<br />

10

- Invoer van de ontwerpbeschrijving<br />

N<br />

BEGIN<br />

INVOER ONTWERP<br />

AUTOMATISCHE<br />

LOGICASYNTHESE<br />

SIMULATIE<br />

CORRECTE<br />

WERKING<br />

PLD PROGRAMMEREN<br />

Hoe ‘intelligenter’ de gebruikte software is, hoe meer vrijheid men heeft bij de invoer van het ontwerp.<br />

De meeste softwarepakketten voor programmeerbare <strong>logica</strong> laten toe ontwerpbeschrijvingen<br />

in te voeren:<br />

- Via een schema (Schematic Capture): een softwarepakket voor PLD’s heeft daarvoor een<br />

grafische editor ingebouwd of kan schema’s van sommige ‘gewone’ EDA-pakketten inlezen;<br />

- Via een tekstuele beschrijving met behulp van één of meer HDL-talen (Hardware Description<br />

Language);<br />

Enkele geavanceerde programma’s laten invoer via golfvormen (Waveform Input) en zelfs gemengde<br />

invoer toe.<br />

De invoer via een schema is eerder ‘klassiek’ te noemen en is slechts geschikt voor kleinere ontwerpen<br />

of delen van een groter ontwerp. Het leren werken met de tekenmodule van een PLDpakket<br />

neemt nogal wat tijd in beslag.<br />

De ontwerper gebruikt in dit geval de componentenbibliotheken van de software om het schema te<br />

tekenen. In feite is deze benadering dezelfde als deze van de reeds vermelde conventionele ont-<br />

J<br />

EINDE<br />

11

.<br />

werpmethode. HDL-invoer laat de ontwerper toe de probleemoplossing volledig tekstueel te beschrijven.<br />

Voor de eigenlijke invoer volstaat een elementair tekstverwerkingsprogramma (editor), dat een<br />

ASCII-bestand kan afleveren. Hedendaagse softwarepakketten voor PLD-ontwerp hebben een<br />

specifieke tekstverwerker voor HDL ingebouwd.<br />

- Automatische <strong>logica</strong>synthese<br />

Deze fase verloopt volledig onder controle van de gespecialiseerde software en omvat een aantal<br />

opeenvolgende bewerkingen op het invoerbestand. Deze bewerkingen zijn nagenoeg voor alle<br />

softwarepakketten voor PLD-ontwerp dezelfde. De bedoeling ervan is een bestand te bekomen dat<br />

kan dienst doen om de chip uiteindelijk te programmeren. De software voert de volgende taken uit:<br />

- vertalen van het invoerbestand naar logische vergelijkingen;<br />

- vereenvoudigen van deze vergelijkingen tot een aantal SOP-termen;<br />

- een ‘netlist’ genereren (dit is een tekstuele weergave van de <strong>logica</strong>);<br />

- inpassen, volgens de netlist, van het ontwerp in de geselecteerde PLD-bouwsteen;<br />

- genereren van een uitvoerbestand om de PLD te programmeren.<br />

- Simuleren van het ontwerp<br />

Men kan de schakeling functioneel nakijken met behulp van de simulatiemodule van de PLD-software,<br />

vooraleer de chip geprogrammeerd wordt. Vooraf dienen er ‘stimuli’ (testsignalen) te worden<br />

gedefinieerd. Indien er tijdens die simulatie fouten ontdekt worden, dient men het ontwerp te<br />

wijzigen en de voorafgaande fasen van de werkgang opnieuw te doorlopen.<br />

- Programmeren van de PLD<br />

De wijze van programmeren hangt af van wat er op de markt aan mogelijkheden beschikbaar is.<br />

Het uitvoerbestand kan bijvoorbeeld in een PLD-programmeerapparaat geladen worden, dat in<br />

staat is de gewenste schakeling in de PLD te configureren (PLD, EPLD, EEPLD …) Deze apparatuur<br />

bestaat meestal uit een kaart, die in een vrij ‘slot’ van een PC moet geplaatst worden en<br />

een console verbonden met deze kaart, uitgerust met de juiste voet voor het betreffende IC. Een<br />

PLD heeft steeds een aantal programmeerpinnen langs waar het configureren kan plaats vinden. Er<br />

is uiteraard ook programmeersoftware nodig om het configuratieproces te besturen (dit kan een<br />

module van de ontwerpsoftware zijn of een afzonderlijk programma, geleverd bij het programmeertoestel).<br />

Bij een aantal PLD-types is het zelfs mogelijk het IC te (her)programmeren terwijl dit<br />

zich in de toepassing op de PCB bevindt (meestal EEPLD’s).<br />

Een geprogrammeerde PLD dient uiteraard te functioneren in het geheel van de schakeling waarvan de<br />

betreffende component deel uitmaakt, wat eveneens – eventueel via een prototype – wordt getest. Deze<br />

laatste fase werd niet in de bovenstaande werkgang opgenomen, omdat ze niet essentieel is voor het<br />

produceren van de PLD-bouwsteen.<br />

12