Processador nanoPCS-1 - PCS - USP

Processador nanoPCS-1 - PCS - USP

Processador nanoPCS-1 - PCS - USP

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

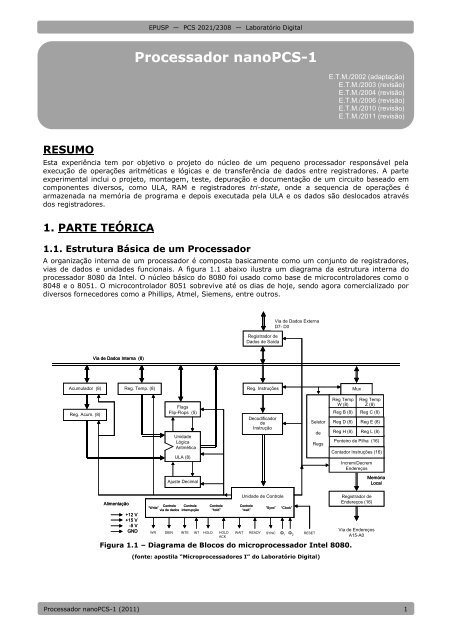

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1E.T.M./2002 (adaptação)E.T.M./2003 (revisão)E.T.M./2004 (revisão)E.T.M./2006 (revisão)E.T.M./2010 (revisão)E.T.M./2011 (revisão)RESUMOEsta experiência tem por objetivo o projeto do núcleo de um pequeno processador responsável pelaexecução de operações aritméticas e lógicas e de transferência de dados entre registradores. A parteexperimental inclui o projeto, montagem, teste, depuração e documentação de um circuito baseado emcomponentes diversos, como ULA, RAM e registradores tri-state, onde a sequencia de operações éarmazenada na memória de programa e depois executada pela ULA e os dados são deslocados atravésdos registradores.1. PARTE TEÓRICA1.1. Estrutura Básica de um <strong>Processador</strong>A organização interna de um processador é composta basicamente como um conjunto de registradores,vias de dados e unidades funcionais. A figura 1.1 abaixo ilustra um diagrama da estrutura interna doprocessador 8080 da Intel. O núcleo básico do 8080 foi usado como base de microcontroladores como o8048 e o 8051. O microcontrolador 8051 sobrevive até os dias de hoje, sendo agora comercializado pordiversos fornecedores como a Phillips, Atmel, Siemens, entre outros.Via de Dados ExternaD7- D0Registrador deDados de SaídaVia de Dados Interna (8)Acumulador (8)Reg. Temp. (8)Reg. InstruçõesMuxReg. Acum. (8)FlagsFlip-Flops (5)UnidadeLógica.....AritméticaULA (8)DecodificadordeInstruçãoSeletordeRegsReg TempReg TempW (8)Z (8)Reg B (8)Reg C (8)Reg D (8)Reg H (8)Reg E (8)Reg L (8)Ponteiro de Pilha (16)Contador Instruções (16)Increm/DecremEndereçosAjuste DecimalMemóriaLocalAlimentação+12 V+15 V-5 VGNDUnidade de ControleControleControleControleControle“Write”“Sync”via de dadosinterrupção“hold”“wait”“Clock”WRDBININTE INT HOLD HOLDWAIT READY SYNC Φ 1 Φ 2 RESETACKFigura 1.1 – Diagrama de Blocos do microprocessador Intel 8080.(fonte: apostila “Microprocessadores I” do Laboratório Digital)Registrador deEndereços (16)Via de EndereçosA15-A0<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1 (2011) 1

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório DigitalA memória local do microprocessador 8080 é constituída de um conjunto de registradores temporários,de uso geral, ponteiro de pilha (SP) e contador de instrução (PC). Os registradores de uso geral (B, C, D,E, H e L) são endereçáveis diretamente por instruções de programa e podem ser utilizados aos pares(registradores de 16 bits) ou isoladamente (registradores de 8 bits). Os registradores temporários sãoutilizados pela unidade de controle e não são acessíveis pelo programador. O ponteiro de pilha define, nocomeço do programa, o início da pilha. O contador de instrução é automaticamente incrementado,através do acionamento do circuito de incremento/decremento, durante cada fase de busca de instrução,e indica o endereço da próxima instrução a ser executada.A comunicação entre a memória local e a via interna de dados é feita através do multiplexador, emblocos de 8 bits. A via externa de dados é acessada através do registrador de dados de saída. Oregistrador possui excitadores que operam em três modos: desligado (a via externa fica isolada dainterna); saída (os dados existentes na via interna são colocados na externa); e entrada (os dados da viaexterna são colocados na via interna, de acordo com a operação que está sendo executada).As operações lógicas e aritméticas são realizadas pela ULA, que tem como entradas os registradores Reg.Temp., Reg. Acum. e o Flag (vai-um). As instruções aritméticas são realizadas com o Acumulador. Oregistrador Flags, constituído dos bits ―zero‖, ―vai-um―, ―sinal‖, ―paridade‖ e ―vai-um auxiliar‖, éatualizado por instruções aritméticas e lógicas, conforme o resultado da operação.A Unidade de Controle, em função do código da operação e tendo como referência sinais de relógio,fornece os sinais de controle do fluxo de dados (interno), além de gerar os sinais para controle externo.Desde a década de 70, quando os microprocessadores foram introduzidos ao mercado pela Intel com olançamento do 4004, os microprocessadores tem evoluído muito. <strong>Processador</strong>es mais modernosapresentam uma organização interna mais sofisticada, porém a estrutura básica é praticamente amesma. A figura 1.2 mostra o diagrama de blocos do processador Athlon da AMD. Novos elementos estãopresentes, que foram sendo embutidos, como por exemplo, memórias cache, unidades de pontoflutuante, pipeline para execução de instruções, TLB, entre outros.Figura 1.2 – Diagrama de blocos do microprocessador AMD Athlon. fonte: (AMD, 2000)Novos processadores são introduzidos regularmente no mercado e incluem novas características visandoaumentar o desempenho de processamento e reduzir o consumo de energia. Por exemplo, o processadorCore i7 990x da Intel disponibiliza 6 núcleos no mesmo encapsulamento, permitindo a execução paralelade vários programas ou tarefas. Outras inovações na microarquitetura destes novos processadoresincluem, entre outros aspectos, a execução de várias linhas de processamento por núcleo(multithreading) e a possibilidade de gerenciar o consumo de energia de partes dos núcleos de execuçãodo processador e desligar a alimentação das partes ociosas (Intel, 2006).<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1 (2011) 2

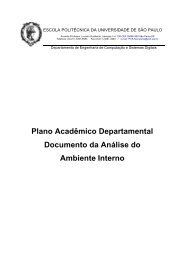

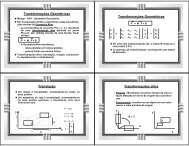

REG.VAIEP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital2. PARTE EXPERIMENTALO projeto desta experiência será o desenvolvimento do núcleo de um processador, chamado <strong>nano<strong>PCS</strong></strong>-1,que permite a execução de pequenos programas, e é composto por uma ULA, alguns registradores, umavia de dados interna e uma memória de programa.A escolha do método de projeto fica a cargo do grupo. Contudo a documentação deve incluir umadescrição completa do funcionamento do fluxo de dados e da unidade de controle, simulações das váriaspartes do circuito e do circuito completo.2.1. Especificação do Núcleo do <strong>Processador</strong>O núcleo do processador <strong>nano<strong>PCS</strong></strong>-1 é apresentado na figura 2.1 abaixo. Ele é composto por uma ULA de4 bits, uma memória de programa de 16 palavras de 8 bits, cinco registradores (REM, REG.ULA,REG.VAI, REG.R0 e REG.R1) e uma via de dados interna.INCRDADO EXTERNO(CHAVES)LIMPAREM4DISPLAY D044DADO (CHAVES)7MEMÓRIALEDs L8-L146OPER_ULABULAAVAI-UMCOPIA.ULADISPLAY D1LED L0GRAVACOPIA.ULACOLOCA.ULA4REG.ULACOPIA.R0DISPLAY D3REG.R0VIA TRI-STATECOPIA.R1COLOCA.R1REG.R1DISPLAY D2Figura 2.1. Fluxo de Dados do processador <strong>nano<strong>PCS</strong></strong>-1.A memória de programa armazena um conjunto de bytes de dados contendo códigos de instruçõespara serem executados pelo processador. O formato das instruções será detalhado mais a seguir. Amemória é endereçada pelo registrador REM (registrador de endereço de memória), que indica qualinstrução está sendo executado em um dado momento. A primeira instrução de um programa deve estarno endereço 0 (ZERO) da memória de programa.A instrução é enviada para a unidade de controle, que gera sinais de controle para a ULA e para osregistradores.A ULA executa a operação codificada pelo sinal de controle OPER_ULA de 6 bits e tem como entradas odado externo proveniente das chaves e o registrador REG.R0. O resultado deve ser armazenado peloregistrador REG.ULA e pelo flip-flop REG.VAI (registrador de vai-um).O conteúdo dos registradores REG.ULA e REG.R1 podem ser movimentados através da via de dadosinterna do processador. Quando um dado for selecionado para processamento, este deve ser copiadopara o registrador REG.R0 antes da execução da operação pela ULA.<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1 (2011) 3

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital2.1.1. Detalhamento dos Sinais de ControleA figura 2.1 mostra, além dos principais componentes do fluxo de dados, alguns sinais de controle. Estessinais devem ser gerados pela unidade de controle. A tabela 2.1 abaixo apresenta uma breve descriçãodestes sinais.Tabela 2.1 – Principais sinais de controle do processador <strong>nano<strong>PCS</strong></strong>-1.componente sinal de controle descriçãoREMINCRLIMPAIncrementa valor do registrador.Zera valor do registrador.MEMORIA GRAVA Seleciona operação de gravação dos dados de entrada.REG.VAI COPIA.ULA Aciona armazenamento do bit de vai-um.REG.ULACOPIA.ULACOLOCA.ULAAciona armazenamento da saída da ULA.REG.R0 COPIA.R0 Copia dado da via tri-state.REG.R1COPIA.R1COLOCA.R1Habilita saída do registrador para colocar dado na via tri-state.Copia dado da via tri-state.ULA OPER_ULA Código de operação da ULA.Habilita saída do registrador para colocar dado na via tri-state.2.1.2. Modos de Operação do <strong>Processador</strong>O núcleo do processador tem dois modos de operação, descritos a seguir:i) Modo ―Programação‖: este modo de operação permite a carga de um "programa" na memória deprograma, que comandará a seqüência de operações que se quer executar. Deve-se utilizar:7 chaves (CH0 a CH6) para a entrada do conteúdo da memória (observar que o bit 6 da palavra dememória não é usada na codificação das instruções);1 botão (B1) para gerar o sinal INCR, que tem como função incrementar o Registrador deEndereços da Memória (REM);1 botão (B2) para gerar o sinal GRAVA, que força o armazenamento do conteúdo das chaves namemória.ii) Modo "Execução": neste modo de operação, o processador deve executar a seqüência de operaçõesdada pelo conteúdo da memória de programas. Deve-se utilizar:4 chaves (CH0 a CH3) para a entrada de dados externa;1 botão (B1) para comandar a execução de uma "instrução", gerando os sinais adequados ao FDdo processador e também o sinal INCR (para incrementar o registrador REM);1 botão (B2) para gerar o sinal LIMPA, que tem como função zerar o REM. Este botão só deveráser utilizado em caso de erro ou reinício de execução de programa.O Modo de Operação deve ser determinado por meio da chave CH7 (0=Programação e 1=Execução).Assim, para se executar um "programa", deve-se seguir o seguinte procedimento:a) Colocar o circuito em modo "Programação" e armazenar o "programa" na memória de programa;b) Acertar a chave CH7 para colocar o circuito em modo "Execução" e limpar o REM, acionando obotão B2;c) Executar, passo a passo, as "instruções", colocando nas chaves o dado de entrada a sermanipulado e apertando o botão de execução (B1). Os resultados intermediários deverão seracompanhados através dos leds e displays (conforme especificado na figura 2.1).<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1 (2011) 4

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital2.1.2. Formato das InstruçõesCada instrução do processador <strong>nano<strong>PCS</strong></strong>-1 tem 8 bits de largura e estão contidas na memória deprograma do circuito. O conjunto de instruções pode ser dividido em dois grupos:i) Instruções aritméticas e lógicas: cada instrução deste grupo tem o bit 6 igual a 0 e os 6 bits menossignificativos determinam a operação a ser executada pela ULA (através dos pinos S0, S1, S2, S3, M eCn). O formato destas instruções é o seguinte:7 6 5 4 3 2 1 0 0 M C n S 3 S 2 S 1 S 0Os bits 0 a 5 são usados conforme o funcionamento da ULA selecionada para o projeto. O sinal significaque o bit 7 não é usado e não deve ser considerado (em inglês, ―don´t care‖). A tabela 2.2 abaixoespecifica algumas instruções a serem projetadas.Tabela 2.2. Instruções aritméticas e lógicas do processador <strong>nano<strong>PCS</strong></strong>-1.InstruçãoSOMASUBTRAIDescriçãoresultado = A + Bresultado = A - BZERA resultado = 0ENTRA_DADOE_LOGOU_LOGNAO_LOGOU_EXCLresultado = Bresultado = A AND Bresultado = A OR Bresultado = resultado = A XOR Bii) Instruções de transferência de dados entre registradores: cada instrução deste grupo tem o bit 6 iguala 1. Os registradores de origem e de destino para a transferência dos dados são especificados pelosquatro bits menos significativos, seguindo o formato abaixo.7 6 5 4 3 2 1 0 1 Reg.origemReg.destinoOs bits 2 e 3 identificam o registrador origem da transferência, ou seja, aquele que colocará os dados navia tri-state para ser copiado pelo destino. Os bits 0 e 1 identificam o registrador que receberá os dados.Os registradores são identificados pela seguinte codificação (tabela 2.3).Tabela 2.3 – Codificação dos registradores.IdentificaçãoReg.origemReg.destino00 Reg. ULA --01 -- Reg. R010 Reg. R1 Reg. R111 -- --A instrução de transferência de dados entre registradores tem a sintaxe MOVE origem,destino em umprograma em linguagem de montagem.A lógica de controle do circuito deverá receber a palavra de memória de forma a decodificar a instrução aser executada e gerar os sinais de controle adequados para a ULA, os registradores, e demaiscomponentes do fluxo de dados.Para implementar a via de dados tri-state deverão ser utilizados componentes com saída tri-state. Paratal, pode-se fazer uso do registrador 74173 (já estudado na experiência ―Via de Dados‖).<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1 (2011) 5

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório DigitalConvém mencionar que para a correta transferência dos dados entre os registradores, o registrador deorigem deve colocar seu dado na via de dados antes do registrador de destino ser ativado e devetambém manter este dado ativo durante toda a transferência. 12.2. Dicas para a Simulação do Projeto no Quartus IIPara a simulação do componente 74189, use o arquivo memoria.gdf disponível na página web do curso,que contém um circuito equivalente. Para a simulação do projeto completo usando este arquivo,deve-se usar no Quartus II um dispositivo de uma das famílias Cyclone ao invés da família MAX7000S(porque um componente da família MAX7000S não tem capacidade de comportar o circuito completo).2.3. Montagem Experimental e Depuração do ProjetoA montagem do circuito do núcleo do processador será dividida em duas etapas principais:PARTE I: sistema de memória de programa, composto pelos componentes REM e MEMÓRIA ecircuitos relacionados;PARTE II: sistema de execução das instruções, composto pelos componentes ULA, RV, REG.ULA, REG. R0 e REG. R1, e outros circuitos (lógica de controle, etc.).A figura 2.3 apresenta um detalhamento do circuito da parte I. A unidade de controle que gera os sinaispara os elementos do sistema de memória de programa deve ser projetada em conjunto com oscomponentes principais deste módulo.INCRLIMPAREM4DISPLAYLEDsDADO (CHAVES)7MEMÓRIA7<strong>nano<strong>PCS</strong></strong>-1(Parte II).GRAVAUnidade deControle daParte IB1 B2 CH7Figura 2.3 – Detalhamento do circuito da parte I.1 Para mais informações consulte a apostila da experiência ―Via de Dados‖ da disciplina Laboratório Digital I (<strong>PCS</strong> 2011/2305).<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1 (2011) 6

REG.VAIEP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório DigitalA figura 2.4 a seguir apresenta a parte II, incluindo também a respectiva unidade de controle.INCRDADO EXTERNO(CHAVES)LIMPAREM4DISPLAY D044DADO (CHAVES)7MEMÓRIALEDs L8-L146OPER_ULABULAAVAI-UMCOPIA.ULADISPLAY D1LED L0GRAVACOPIA.ULACOLOCA.ULA4REG.ULACOPIA.R0DISPLAY D3REG.R0VIA TRI-STATECOPIA.R1COLOCA.R1REG.R1DISPLAY D2Figura 2.4 – Detalhamento do circuito da parte II.A montagem, teste de depuração do projeto será executada em três etapas:1. montagem da parte I;2. montagem e integração da parte II;3. avaliação do funcionamento do circuito completo.DICA: Para os testes, sugere-se que sinais extras de teste e depuração sejam monitorados em leds nopainel de montagens experimentais. Estes sinais devem monitorar partes do fluxo de dados e também oestado da máquina de estados da unidade de controle.PERGUNTAS:1. Elabore uma tabela contendo o código binário a ser programado na memória de programa para cadauma das instruções do processador <strong>nano<strong>PCS</strong></strong>-1.2. Como a característica da memória 74189 de inverter o dado na saída é aproveitada no projeto dogrupo?3. Quais testes estão programados para avaliar o correto funcionamento de cada PARTE do circuito doprocessador <strong>nano<strong>PCS</strong></strong>-1? Explique o objetivo de cada um destes.4. Como a montagem da parte I será efetuada? Descreva os passos planejados.5. Como o grupo planejou a montagem da parte II? Descreva os passos.6. Como o ―estado atual‖ da unidade de controle pode ser monitorado durante a montagem do circuito?Especifique sinais adicionais a serem acrescentados no projeto para facilitar a depuração.7. Que cuidados serão necessários para a integração das partes I e II?8. Como o grupo gerenciou a complexidade do circuito projetado com relação à montagem?<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1 (2011) 7

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital2.4. Teste do Funcionamento do Circuitoa) Verifique o funcionamento do circuito para várias sequencias de operações simples, variando tambémos dados de entrada. Explique os testes programados.b) Execute o seguinte ―programa‖, acionando adequadamente os botões B1 e B2, a chave CH7 e aentrada de dados externa (CH0-CH3).ENTRA_DADO 5MOVE; 5 na entrada de dados; (reg.ULA contém 5)reg.ULA,reg.R0 ; coloca 5 em R0SOMA 1 ; 5+1=6MOVEreg.ULA,reg.R1 ; guarda 6 em R1MOVE reg.R1,reg.R0 ; copia 6 em R0E_LOG 3 ; 6and3=2MOVE reg.ULA,reg.R0 ; display de R0 deve mostrar “2”MOVE reg.R1,reg.R0 ; display de R0 deve mostrar “6”c) Escreva programas para a avaliação das seguintes expressões:i. Y = A – B + Cii. Y = ((A AND B) OR NOT(C)) XOR DVerifique os resultados obtidos executando os "programas", para diferentes valores de A, B, C e D.ATENÇÃO: Poderá ser solicitada uma modificação no circuito implementado por parte do professor, aofinal da apresentação do funcionamento do circuito do processador <strong>nano<strong>PCS</strong></strong>-1.d) OPCIONAL. Implemente uma modificação especificado pelo professor no circuito implementado doprocessador <strong>nano<strong>PCS</strong></strong>-1.2.5. Sobre o Planejamento e o RelatórioO planejamento deve conter OBRIGATORIAMENTE os seguintes itens:Diagrama de blocos do circuito;Descrição detalhada do funcionamento de cada um dos módulos;Relação de sinais extras de teste e depuração a serem monitorados em leds;Diagrama lógico completo do circuito projetado;Simulações com o Quartus II para cada uma dos modos de operação do circuito(apresentar as diversas cartas de tempo resultantes); Tabela de códigos binários das instruções do <strong>nano<strong>PCS</strong></strong>-1 descritas na tabela 2.2. Programação dos testes solicitados no item 2.4, com a explicação de cada instrução.O relatório deverá conter:Os principais eventos (fatos, erros, imprevistos) acontecidos na montagem e depuraçãode cada parte do circuito e na sua integração;Apresentação dos resultados obtidos na parte experimental;Discussão da realização da experiência;Conclusões.<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1 (2011) 8

EP<strong>USP</strong> — <strong>PCS</strong> 2021/2308 — Laboratório Digital3. BIBLIOGRAFIA AMD. AMD Athlon Processor x86 Code Optimization Guide. 2000. Fairchild Semiconductor. TTL Data Book. Mountain View, California, 1978.FREGNI, Edson e SARAIVA, Antonio M. Engenharia do Projeto Lógico Digital: Conceitos ePrática. Editora Edgard Blücher Ltda, 1995.INTEL. Inside Intel Core Microarchitecture: setting new standards for energy-efficientperformance. White Paper. 2006.<strong>PCS</strong>/EP<strong>USP</strong>. Unidade Lógica e Aritmética. Apostila de Laboratório Digital. Departamento deEngenharia de Computação e Sistemas Digitais, Escola Politécnica da <strong>USP</strong>. 2004.<strong>PCS</strong>/EP<strong>USP</strong>. Via de Dados. Apostila de Laboratório Digital. Departamento de Engenharia deComputação e Sistemas Digitais, Escola Politécnica da <strong>USP</strong>. 2004.<strong>PCS</strong>/EP<strong>USP</strong>. Microprocessadores I. Apostila de Laboratório Digital. Departamento de Engenharia deComputação e Sistemas Digitais, Escola Politécnica da <strong>USP</strong>. 2002. WAKERLY, John F. Digital Design Principles & Practices. 3 rd edition, Prentice Hall, 2000.4. MATERIAL DISPONÍVELCircuito Integrado TTL:Portas lógicas (7400, 7404, 7408, 7410, 7432, 7486)7474, 74139, 74161, 74163, 74173, 74175, 74181, 74189.Se precisar usar outro componente, verifique previamente sua disponibilidade no Laboratório Digital.5. EQUIPAMENTOS NECESSÁRIOS1 painel de montagens experimentais. 1 fonte de alimentação fixa, 5V 5%, 4A.1 osciloscópio digital.1 multímetro digital.1 gerador de pulsos.1 computador compatível com IBM-PC.Programa Quartus II da Altera.<strong>Processador</strong> <strong>nano<strong>PCS</strong></strong>-1 (2011) 9