Verificador de Senhas - PCS - USP

Verificador de Senhas - PCS - USP

Verificador de Senhas - PCS - USP

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital<strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong>Versão 2012RESUMOEsta experiência consiste no projeto e na implementação <strong>de</strong> um circuito <strong>de</strong> controle digital paraverificação <strong>de</strong> códigos <strong>de</strong> segurança. O procedimento <strong>de</strong> operação <strong>de</strong>ste circuito é bem semelhante aofuncionamento padrão <strong>de</strong> um cofre ou <strong>de</strong> um ca<strong>de</strong>ado eletrônico com um mecanismo <strong>de</strong> senhas. Aliberação da trava do circuito está condicionada à introdução <strong>de</strong> uma combinação igual a um códigopreviamente cadastrado. Tentativas <strong>de</strong> burlar este procedimento <strong>de</strong>vem ser previstas e bloqueadas.1. ESPECIFICAÇÃO FUNCIONALO circuito do verificador <strong>de</strong> senhas a ser projetado nesta experiência é um circuito simplificado <strong>de</strong> umsistema completo para uso em segurança <strong>de</strong> bens ou valores. Po<strong>de</strong> ser usado para controlar o acesso a<strong>de</strong>pósitos <strong>de</strong> valores ou documentos sigilosos. O mecanismo <strong>de</strong> acesso é baseado na verificação <strong>de</strong> umacombinação <strong>de</strong> dígitos <strong>de</strong> segurança.O circuito <strong>de</strong>ve possuir dois modos <strong>de</strong> operação: o Modo <strong>de</strong> Configuração e o Modo <strong>de</strong> Segurança.Estes modos são selecionados através <strong>de</strong> uma chave no painel <strong>de</strong> controle. As outras chaves do painelsomente ficam ativas enquanto o sistema não estiver bloqueado.No Modo <strong>de</strong> Configuração é feita a programação da combinação <strong>de</strong> abertura do circuito que consta <strong>de</strong>4 dígitos. Cada dígito é selecionado a partir <strong>de</strong> um total <strong>de</strong> 4 chaves <strong>de</strong> entrada. Esta combinação<strong>de</strong>ve ficar armazenada na memória do sistema.No Modo <strong>de</strong> Segurança é inserido um código, também constituído <strong>de</strong> 4 dígitos. Após a entrada <strong>de</strong>stecódigo, caso haja coincidência com a senha <strong>de</strong> abertura programada anteriormente, um sinal <strong>de</strong>veser enviado ao controle da trava para este ser aberto. Este sinal será representado através <strong>de</strong> umLED que <strong>de</strong>ve permanecer aceso enquanto a trava não for aberta.A entrada das teclas que compõem a combinação <strong>de</strong>ve ser feita sequencialmente. O pressionamento<strong>de</strong> uma tecla é simulado através da ativação <strong>de</strong> uma chave (esta ativação se dará com a mudança dachave para o nível baixo). A chave <strong>de</strong>ve ser <strong>de</strong>sativada para que outra tecla seja posteriormente ativada(mesmo que seja o mesmo código).Após a mudança do modo <strong>de</strong> operação do circuito, <strong>de</strong>ve-se prever uma reinicialização do sistema(RESET). Isto permite que, no modo <strong>de</strong> configuração, caso seja efetuado o cadastramento <strong>de</strong> uma senhainválida, seja possível o recadastramento da senha com o acionamento do sinal <strong>de</strong> RESET.Por outro lado, no caso <strong>de</strong> acionamento <strong>de</strong> um dígito inválido no modo <strong>de</strong> segurança, o usuário po<strong>de</strong>corrigir a entrada da senha correta, acionando-se o RESET. Isto só será possível durante a entrada dostrês primeiros dígitos da senha, pois o circuito <strong>de</strong>ve bloquear seu funcionamento após a entrada doúltimo dígito e se a senha não for correta. Ou seja, caso o usuário não fornecer a senha correta, ocircuito <strong>de</strong>ve bloquear seu funcionamento e não respon<strong>de</strong>r a nenhum acionamento <strong>de</strong> qualquer tecla oubotão (p.ex. RESET, etc). Neste caso é necessário o acionamento do sinal DESBLOQUEAR para que elesaia <strong>de</strong>ste estado <strong>de</strong> bloqueio.<strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong> (2012) 1

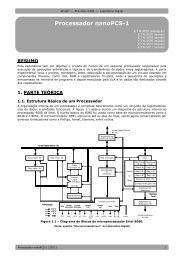

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital2. DETALHAMENTO DO VERIFICADOR DE SENHAS2.1. Diagrama <strong>de</strong> BlocosO projeto básico do circuito do verificador <strong>de</strong> senhas <strong>de</strong>ve seguir o Diagrama <strong>de</strong> Blocos apresentado nafigura 1. Os blocos envolvidos são os seguintes:CODIFICADOR: codifica cada chave <strong>de</strong> entrada selecionada em um código binário <strong>de</strong> 2 bits,que indica a chave selecionada;MEMÓRIA: armazena a senha cadastrada no Modo <strong>de</strong> Configuração;CONTADOR: fornece o en<strong>de</strong>reço no qual o código da tecla <strong>de</strong>verá ser armazenado ou lido damemória;COMPARADOR: compara cada um dos códigos inseridos no Modo <strong>de</strong> Segurança com o códigocorrespon<strong>de</strong>nte previamente armazenado na memória;UNIDADE DE CONTROLE: controla o funcionamento do circuito do verificador <strong>de</strong> senhas nosModos <strong>de</strong> Configuração e <strong>de</strong> Segurança.FLUXO DE DADOSTECLAS(CHAVES)0123CODIFICADORCÓDIGO(D0)2CONTADOREND(D2)SAÍDAENTRADAMEMÓRIAENDEREÇOSINAISDECONTROLEDAMEMÓRIACÓDIGO_MEM(D1)COMPARADOR=COMPARAÇÃOZERATECLA ACIONADACLOCKCONTAUNIDADEDECONTROLEBLOQUEADO (L2)ABRE (L1)MODO (L0)(B1)(B2)(CH7)RESETDESBLOQUEARCONFIGURAÇÃO / SEGURANÇAFigura 1. Diagrama <strong>de</strong> Blocos do <strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong>.<strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong> (2012) 2

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital2.2. Sinais do Circuito do <strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong>Os sinais do circuito são os apresentados abaixo, classificados como sinais <strong>de</strong> entrada, sinais <strong>de</strong> saída esinal <strong>de</strong> controle interno.NÃO SERÁ PERMITIDA A MUDANÇA DE QUALQUER UM DESTES SINAIS E NEM DO SEU NÍVEL LÓGICO.QUALQUER MUDANÇA IMPLICARÁ EM UMA PENALIZAÇÃO.a) Sinais <strong>de</strong> Entrada: TECLAS (CH0 a CH3) chaves que correspon<strong>de</strong>m às teclas <strong>de</strong> senha; ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅/SEGURANÇA (CH7) seleciona o modo <strong>de</strong> operação do circuito(0 = modo <strong>de</strong> configuração e 1 = modo <strong>de</strong> segurança); RESET (B1) inicialização do sistema em cada um dos modos <strong>de</strong> operação (pulso em nível alto);DESBLOQUEAR (B2) – permite <strong>de</strong>sbloquear o circuito em caso <strong>de</strong> senha errada;CLOCK sinal do gerador externo para sincronismo do controle.b) Sinais <strong>de</strong> Saída: MODO (LED 0) indica o modo <strong>de</strong> operação do circuito(0 = modo <strong>de</strong> segurança e 1 = modo <strong>de</strong> configuração); ̅̅̅̅̅̅̅ (LED 1) quando em nível “zero” indica a abertura do circuito;TRAVADO (LED 2) indica que o circuito está travado/bloqueado.c) Sinais <strong>de</strong> Controle Internos: TECLA ACIONADA sinal auxiliar que indica a seleção <strong>de</strong> uma chave <strong>de</strong> entrada;CONTA sinal <strong>de</strong> controle do contador para varredura (incremento) dos en<strong>de</strong>reços da memória;ZERA sinal para zerar o valor do contador para varredura dos en<strong>de</strong>reços da memória;COMPARAÇÃO saída do comparador indicando igualda<strong>de</strong> ou não entre o código cadastradoe o código inserido;SINAIS DE CONTROLE DA MEMÓRIA utilizados para controle <strong>de</strong> operações <strong>de</strong> leitura egravação <strong>de</strong> dados na memória.d) Sinais Internos: CÓDIGO (display D0) código binário <strong>de</strong> 2 bits da chave selecionada;CÓDIGO_MEM (display D1) código armazenado na memória;END (display D2) en<strong>de</strong>reço para acesso à memória;ATENÇÃO:Note que, exceto o sinal ̅̅̅̅̅̅̅, todos os outros são <strong>de</strong> lógica positiva, ou seja, ativos quando em nível 1.<strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong> (2012) 3

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital3. PARTE EXPERIMENTALA parte experimental <strong>de</strong>sta experiência diz respeito à implementação do circuito verificador <strong>de</strong> senhas,incluindo a montagem e os testes no painel <strong>de</strong> montagens experimentais.3.1. Montagem em LaboratórioA sequencia <strong>de</strong> montagem, teste e <strong>de</strong>puração do circuito <strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong> <strong>de</strong>verá seguir as etapasabaixo:1. Modo <strong>de</strong> ConfiguraçãoNesta etapa, <strong>de</strong>verão ser montados e testados os módulos codificador, contador, memória eparte da lógica <strong>de</strong> controle, referentes ao funcionamento do Modo <strong>de</strong> Configuração. A equipe<strong>de</strong>ve planejar os passos necessários para esta etapa, mostrando os testes que <strong>de</strong>vem serefetuados para apresentar um circuito funcionalmente correto.2. Modo <strong>de</strong> SegurançaAqui, <strong>de</strong>vem ser montados e testados o módulo comparador e parte da lógica <strong>de</strong> controle,referente ao funcionamento do Modo <strong>de</strong> Segurança. A equipe <strong>de</strong>ve planejar os procedimentosa<strong>de</strong>quados para a <strong>de</strong>monstração do funcionamento correto do circuito.3. Integração e Teste do circuito completoNesta etapa, o circuito completo do <strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong> <strong>de</strong>verá ser avaliado para se verificar oseu pleno funcionamento.DICAS: Para auxiliar a <strong>de</strong>puração do circuito, especifique sinais extras <strong>de</strong> teste e <strong>de</strong>puração (por exemplo,estado atual da unida<strong>de</strong> <strong>de</strong> controle). O acionamento das chaves do painel <strong>de</strong> montagens experimentais gera a ocorrência da trepidação(“bounce”) do sinal elétrico. Isto <strong>de</strong>ve ser consi<strong>de</strong>rado durante o projeto do circuito.3.2. Operação do CircuitoNesta etapa, o circuito completo <strong>de</strong>verá ser avaliado. A sequência normal <strong>de</strong> utilização <strong>de</strong>verá ser testadapela equipe: inicialmente, uma senha <strong>de</strong>verá ser cadastrada, e <strong>de</strong>pois, ao menos dois casos, serãoanalisados (senha válida e senha inválida). O uso dos sinais RESET e DESBLOQUEAR também <strong>de</strong>verãoser levados em conta.A seguir, o funcionamento do circuito montado <strong>de</strong>verá ser <strong>de</strong>monstrado ao professor, <strong>de</strong> acordocom o Manual do Usuário escrito pela equipe.3.3. Modificação do Projeto BaseUma pequena modificação ou adaptação do projeto base será solicitada ao aluno. Esta modificação<strong>de</strong>verá ser implementada no circuito projetado pelo grupo. A <strong>de</strong>scrição e a documentação <strong>de</strong>stamodificação <strong>de</strong>vem ser incluídas no relatório.PERGUNTAS:1. O que ocorre no circuito projetado, caso o usuário tente inserir mais <strong>de</strong> 16 dígitos quando estivercadastrando uma senha?2. O circuito integrado 74189 tem as saídas invertidas, ou seja, na operação <strong>de</strong> leitura, os dados <strong>de</strong>saída são invertidos em relação aos dados gravados. Como isto é tratado no projeto do circuito?3. Como a ocorrência <strong>de</strong> “bounce” das chaves foi levada em consi<strong>de</strong>ração no projeto do circuito?4. O que ocorre na operação do circuito se o botão B1 (sinal RESET) for substituído por uma chave?5. Como a lógica <strong>de</strong> bloqueio do circuito em caso <strong>de</strong> senha errada é implementada no circuito?6. Como po<strong>de</strong>ria ser implementada a característica <strong>de</strong> se permitir que o usuário tenha mais umatentativa para “entrar” a senha correta?7. Descreva que modificações seriam necessárias no projeto caso se <strong>de</strong>sejasse a implementação <strong>de</strong> uma“senha padrão <strong>de</strong> fábrica”. (Uma senha padrão <strong>de</strong> fábrica seria uma segunda senha que permitiria aabertura da trava. Esta senha viria pré-programada no circuito.)<strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong> (2012) 4

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital4. PLANEJAMENTOO planejamento <strong>de</strong>ve conter OBRIGATORIAMENTE os seguintes itens:Descrição <strong>de</strong>talhada da lógica <strong>de</strong> funcionamento do projeto digital do circuito;Diagrama Lógico do projeto do módulo fluxo <strong>de</strong> dados e do módulo unida<strong>de</strong> <strong>de</strong> controle;Cartas <strong>de</strong> tempo, com as simulações da operação dos blocos e do circuito completo;Estratégia <strong>de</strong> montagem e <strong>de</strong>puração, <strong>de</strong>stacando os blocos funcionais;Casos <strong>de</strong> teste para as várias situações possíveis;Manual <strong>de</strong> Usuário do Circuito <strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong>: texto à parte, <strong>de</strong>screvendo os procedimentos<strong>de</strong> configuração e <strong>de</strong> operação do circuito.5. AVALIAÇÃOA avaliação do projeto do <strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong> será realizada consi<strong>de</strong>rando o funcionamento correto <strong>de</strong>cada subsistema e a sua apresentação <strong>de</strong> maneira convincente pelos alunos ao professor.6. BIBLIOGRAFIA1. FREGNI, E. & SARAIVA, A. M. Engenharia do Projeto Lógico Digital: Conceitos e Prática.Editora Edgard Blücher Ltda, 1995.2. <strong>PCS</strong>-EP<strong>USP</strong>. Ca<strong>de</strong>ado Eletrônico. Apostila <strong>de</strong> <strong>PCS</strong>2308. Departamento <strong>de</strong> Engenharia <strong>de</strong>Computação e Sistemas Digitais, Escola Politécnica da <strong>USP</strong>. Edição <strong>de</strong> 2001.3. <strong>PCS</strong>-EP<strong>USP</strong>. Cofre Digital. Apostila <strong>de</strong> <strong>PCS</strong>2308. Departamento <strong>de</strong> Engenharia <strong>de</strong> Computação eSistemas Digitais, Escola Politécnica da <strong>USP</strong>. Edição <strong>de</strong> 2002.4. RANZINI, E.; HORTA, E. L.; MIDORIKAWA, E. T. Projeto <strong>de</strong> circuitos com MAX+PLUS II. Apostila<strong>de</strong> Laboratório Digital. Departamento <strong>de</strong> Engenharia <strong>de</strong> Computação e Sistemas Digitais, EscolaPolitécnica da <strong>USP</strong>. 2002.5. TOCCI, R. J.; WIDMER, N. S.; MOSS, G. L. Digital Systems: principles and applications. 11 th ed.,Prentice-Hall, 2011.7. MATERIAL DISPONÍVELCircuitos Integrados TTL7400, 7404, 7408, 7432, 7474, 7485 (comparador <strong>de</strong> magnitu<strong>de</strong>), 7486,74148 (codificador <strong>de</strong> priorida<strong>de</strong>), 74161, 74163, 74189 (memória).Caso seja necessário o uso <strong>de</strong> outro componente, verifique antes sua disponibilida<strong>de</strong>no Laboratório Digital.<strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong> (2012) 5

EP<strong>USP</strong> — <strong>PCS</strong> 2011/2305/2355 — Laboratório Digital8. EQUIPAMENTOS NECESSÁRIOS 1 painel <strong>de</strong> montagens experimentais. 1 fonte <strong>de</strong> alimentação fixa, 5V 5%, 4A. 1 osciloscópio digital. 1 multímetro digital. 1 gerador <strong>de</strong> pulsos. 1 computador com o programa Altera Quartus II.Histórico <strong>de</strong> RevisõesE.T.M./2002 – adaptaçãoE.T.M./2003 – revisão e adaptaçãoE.T.M./2004 – revisãoE.T.M./2006 – revisãoE.T.M./2010 – revisãoE.T.M./2012 – revisão<strong>Verificador</strong> <strong>de</strong> <strong>Senhas</strong> (2012) 6