5. 5 Predstavljanje brojeva i aritmetička kola ...

5. 5 Predstavljanje brojeva i aritmetička kola ...

5. 5 Predstavljanje brojeva i aritmetička kola ...

You also want an ePaper? Increase the reach of your titles

YUMPU automatically turns print PDFs into web optimized ePapers that Google loves.

<strong>5.</strong><br />

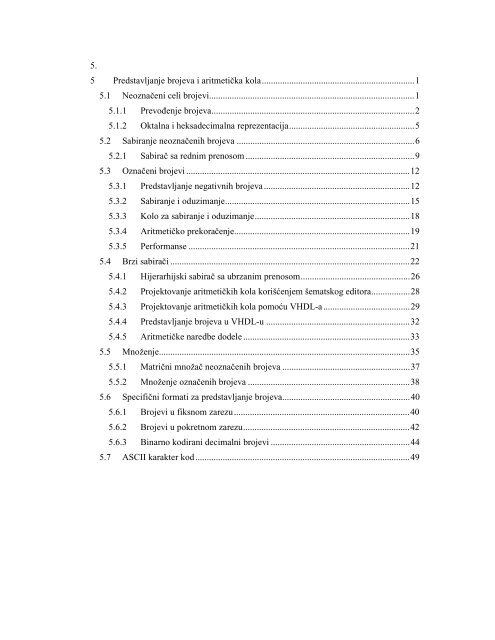

5 <strong>Predstavljanje</strong> <strong>brojeva</strong> i <strong>aritmetička</strong> <strong>kola</strong>...................................................................1<br />

<strong>5.</strong>1 Neoznačeni celi brojevi..........................................................................................1<br />

<strong>5.</strong>1.1 Prevođenje <strong>brojeva</strong>.........................................................................................2<br />

<strong>5.</strong>1.2 Oktalna i heksadecimalna reprezentacija.......................................................5<br />

<strong>5.</strong>2 Sabiranje neoznačenih <strong>brojeva</strong>..............................................................................6<br />

<strong>5.</strong>2.1 Sabirač sa rednim prenosom..........................................................................9<br />

<strong>5.</strong>3 Označeni brojevi..................................................................................................12<br />

<strong>5.</strong>3.1 <strong>Predstavljanje</strong> negativnih <strong>brojeva</strong>................................................................12<br />

<strong>5.</strong>3.2 Sabiranje i oduzimanje.................................................................................15<br />

<strong>5.</strong>3.3 Kolo za sabiranje i oduzimanje....................................................................18<br />

<strong>5.</strong>3.4 Aritmetičko prekoračenje.............................................................................19<br />

<strong>5.</strong>3.5 Performanse.................................................................................................21<br />

<strong>5.</strong>4 Brzi sabirači.........................................................................................................22<br />

<strong>5.</strong>4.1 Hijerarhijski sabirač sa ubrzanim prenosom................................................26<br />

<strong>5.</strong>4.2 Projektovanje aritmetičkih <strong>kola</strong> korišćenjem šematskog editora.................28<br />

<strong>5.</strong>4.3 Projektovanje aritmetičkih <strong>kola</strong> pomoću VHDL-a......................................29<br />

<strong>5.</strong>4.4 <strong>Predstavljanje</strong> <strong>brojeva</strong> u VHDL-u...............................................................32<br />

<strong>5.</strong>4.5 Aritmetičke naredbe dodele.........................................................................33<br />

<strong>5.</strong>5 Množenje..............................................................................................................35<br />

<strong>5.</strong><strong>5.</strong>1 Matrični množač neoznačenih <strong>brojeva</strong>........................................................37<br />

<strong>5.</strong><strong>5.</strong>2 Množenje označenih <strong>brojeva</strong>.......................................................................38<br />

<strong>5.</strong>6 Specifični formati za predstavljanje <strong>brojeva</strong>........................................................40<br />

<strong>5.</strong>6.1 Brojevi u fiksnom zarezu.............................................................................40<br />

<strong>5.</strong>6.2 Brojevi u pokretnom zarezu.........................................................................42<br />

<strong>5.</strong>6.3 Binarno kodirani decimalni brojevi.............................................................44<br />

<strong>5.</strong>7 ASCII karakter kod..............................................................................................49

5 <strong>Predstavljanje</strong> <strong>brojeva</strong> i <strong>aritmetička</strong> <strong>kola</strong><br />

Ovo poglavlje je posvećeno digitalnim kolima koja obavljaju aritmetičke operacije. Biće<br />

razmatrana digitalna <strong>kola</strong> za sabiranje, oduzimanje i množenje. Takođe, biće pokazano kako<br />

se piše VHDL kod koji opisuje <strong>aritmetička</strong> <strong>kola</strong>. Koncepti koji će tom prilikom biti uvedeni<br />

mogu se lako primeniti na mnoge druge tipove <strong>kola</strong>.<br />

Pre nego što se usredsredimo na konstrukciju aritmetičkih <strong>kola</strong>, bitno je uspostaviti vezu<br />

između <strong>brojeva</strong> sa kojima baratamo u realnom životu i načina na koji su u digitalnim<br />

sistemima predstavljaju numeričke veličine. Digitalni sistemi su izgrađeni od <strong>kola</strong> koja<br />

obrađuju binarne, ili logičke, promenljive. U prethodnim poglavljima bavili smo se logičkim<br />

promenljivama na jedan uopšteni način, koristeći logičke promenljive za predstavljanje stanja<br />

prekidača ili nekih drugih uslova koji nisu imali numeričku pozadinu. Da bi se predstavila<br />

neka numerička vrednost, nije dovoljna jedna logička promenljive, već više njih, pri čemu<br />

svaka promenljiva odgovara jednoj cifri broja. U ovom poglavlju biće opisano više načina<br />

kako se brojevi mogu predstaviti pomoću binarnih promenljivih i kako se pomoću takvih<br />

reprezentacija mogu obavljati osnovne računske operacije.<br />

<strong>5.</strong>1 Neoznačeni celi brojevi<br />

Najjednostavnija vrsta <strong>brojeva</strong> su svakako celi brojevi. Pozitivni celi brojevi se zovu<br />

neoznačeni, dok se celi brojevi koji mogu biti i negativni i pozitivni zovu označeni celi<br />

brojevi. U računarskoj terminologiji za cele brojeve koristi se termin intedžer (integer). Osim<br />

celih, kod digitalnih sistema koriste se i razlomljeni brojevi, o čemu će više reči biti u odeljku<br />

X.<br />

U svakodnevnom životu, za predstavljanje i baratanje brojevima koristimo decimalni<br />

brojni sistem. U ovom dobro poznatom sistemu, brojevi se zapisuju kao niz cifara koje imaju<br />

10 mogućih vrednosti, od 0 do 9. Decimalni sistem je pozicioni brojni sistem, s obzirom da je<br />

svakoj cifarskoj poziciji u zapisu broja pridružena težina, a vrednost broja je jednaka<br />

težinskoj suma cifara. Na primer, 1964 = 1×1000 + 9×100 + 6×10 + 4×1. Težine su stepeni<br />

broja 10, tako da, gledano s desna u levo, težina svake sledeće cifarske pozicije je 10 puta<br />

veća od prethodne. U opštem slučaju, n-to cifreni decimalni broj D oblika dn-1dn-2 ... d0 ima<br />

vrednost:<br />

V(D) = dn-1×10 n-1 + dn-2×10 n-2 + ... + d0×10 0<br />

= ∑ − n 1<br />

i<br />

d × 10<br />

i=<br />

0<br />

i<br />

S obzirom da u decimalnom sistemu postoji 10 cifara i da su težine cifarskih pozicija<br />

stepeni broja 10, kažemo da je 10 osnova ili baza (radix, na engleskom jeziku) decimalnog<br />

brojnog sistema. Decimalni brojni sistem je uobičajen i lako razumljiv. Međutim, u<br />

1

digitalnim sistemima nije praktično koristiti cifre koje imaju 10 različitih vrednosti. Kod<br />

digitalnih sistemima koristi se binarni brojni sistem, tj. pozicioni brojni sistem osnove 2, kod<br />

koga postoje samo dve cifre, 0 i 1. Binarne cifre se zovu bitovi, a celi binarni brojevi se<br />

predstavljaju kao niz bitova:<br />

B = bn-1bn-2 ... b0<br />

Po analogiji sa decimalnim brojevima, vrednost n-to bitnog broja B izračunava se na<br />

sledeći način:<br />

V(B) = bn-1×2 n-1 + bn-2×2 n-2 + ... + b0×2 0<br />

=∑ − n<br />

1<br />

i=<br />

0<br />

i<br />

b × 2<br />

(<strong>5.</strong>1)<br />

i<br />

Na primer, vrednost binarnog broja 1011 iznosi:<br />

V = 1×2 3 +0×2 2 +1×2 1 +1×2 0 .<br />

Uočimo da se cifre 0 i 1 koriste i u decimalnom i u binarnom brojnom sistemu, mada u<br />

njima imaju različita značenja. Na primer, broj 11 u decimalnom sistemu ima vrednost<br />

jedanaest, a u binarnom tri. Zato, kada baratamo sa brojevima iz različitih brojnih sistema<br />

koristimo indeks da bi smo ukazali na osnovu brojnog sistema. Tako, binarni broj 1011<br />

zapisujemo kao (1011)2. Vrednost ovog broja je V = 8 + 2 + 1 = 13, što znači: (1011)2=(13)10.<br />

Opseg celobrojnih vrednosti koje se mogu predstaviti binarnim brojem zavisi od broja<br />

bitova koji se koriste. Na primer, sa četiri bita moguće je predstaviti sve cele brojeve iz<br />

opsega od (0000)2=(0)10 do (1111)2=(15)10. U opštem slučaju, korišćenje n bita nam<br />

omogućava da predstavimo celobrojne vrednosti iz opsega 0 do 2 n -1. Neoznačeni celi brojevi<br />

predstavljeni u pozicionom binarnom sistemu se, takođe, nazivaju prirodnim binarnim<br />

brojevima.<br />

U zapisu binarnog broja, bit na krajnjoj desnoj poziciji, kome je pridružena težina 1, zove<br />

se bit najmanje težine (Last-Significant Bit - LSB). Kod neoznačenih celih <strong>brojeva</strong>, bit na<br />

krajnjoj levoj poziciji ima težinu 2 n-1 i zove se bit najveće težine (Most-Significant Bit -<br />

MSB). Često, pogodno je više sukcesivnih bitova tretirati kao jednu celinu. Grupa od četiri<br />

susedna bita zove se tetrada ili nibl, a grupa od osam bitova, bajt. Šesnaest bitova čine dva<br />

bajta ili jednu polu-reč; 32 bita su reč, a 64 bita dupla-reč.<br />

U principu, brojna osnova može biti bilo koji ceo broj, kao na primer 3, 5 ili 11. U<br />

brojnom sistemu osnove r figuriše r cifara, 0, 1, …, r-1, a vrednost broja X=(xn-1xn-2…x0)r<br />

određena je formulom:<br />

n 1<br />

V(X) = ∑ −<br />

i=<br />

0<br />

i<br />

x × r<br />

(<strong>5.</strong>2)<br />

i<br />

Tako, na primer, u brojnom sistemu osnove 5, postoje cifre 0, 1, 2, 3 i 4, a težine cifarskih<br />

pozicija su stepeni broja 5: 1, 5, 25, 125 i td.<br />

<strong>5.</strong>1.1 Prevođenje <strong>brojeva</strong><br />

Zadatak prevođenja <strong>brojeva</strong> je da se broj Ns iz osnove s konvertuje u broj Nr iste vrednosti<br />

iz osnove r. Konverzija Ns→Nr se može obaviti tako što će vrednost broja Ns izračunati u<br />

brojnom sistemu osnove r. Na primer, shodno jednačini (<strong>5.</strong>2) vrednost binarnog broja<br />

P=1425 iznosi:<br />

V (P) = (1×5 2 + 4×5 1 + 2×5 0 )10<br />

2

= (1×25 + 4×5 + 2×1)10<br />

= (47)10<br />

Dakle, važi 1425 = 4710.<br />

Uočimo da su u gornjem izračunavanju, najpre, sve cifre broja P, kao i stepeni broja 5<br />

izraženi kao decimalni brojevi, a da su potom sva potrebna množenja i sabiranja obavljena<br />

primenom decimalne aritmetike.<br />

Konverzija iz nedecimalnog u decimalni broj je laka, zato što se u toku konverzije<br />

računske operacije obavljaju u decimalnom sistemu. Međutim, obrnuta konverzija, iz<br />

decimalnog u nedecimalni sistem, primenom opisanog postupka, predstavlja problem za<br />

čoveka, zato što zahteva da se računske operacije izvode u nedecimalnom sistemu. Na<br />

primer, probajmo da konvertujmo decimalni broj D=(37)10 u binarni. Shodno jednačini (<strong>5.</strong>2),<br />

vrednost ovog broja iznosi:<br />

V(D) = (3×10 1 + 7×10 0 )10 = (3×10 + 7)10<br />

Zamenimo sada sve brojeve iz gornjeg izraza ekvivalentnim binarnim brojevima:<br />

V(D) = (11×1010 + 111)2<br />

Do binarnog broj koji je ekvivalentan decimalnom broju D možemo doći izračunavanjem<br />

gornjeg izraza primenom binarne aritmetike. Međutim, izračunavanje u nedecimalnoj brojnoj<br />

osnovi, ako se obavlja ručno, je naporno i podložno greškama. Zato se konverzija iz<br />

decimalnog u nedecimalni brojni sistem obavlja primenom jednog drugog postupka, koji<br />

omogućava da se računske operacije izvode u decimalnom sistemu.<br />

Konverzija decimalnog broja u nedecimalni sistem osnove r se može obaviti uzastopnim<br />

deljenjem decimalnog broja brojem r. Razmotrimo ovaj postupak na primeru binarnog<br />

sistema, r=2. Neka decimalni broj D=dk-1... d1d0, vrednosti V, treba konvertovati u binarni<br />

broj B=bn-1... b2b1b0. Brojevi D i B imaju istu vrednost V=V(D)=V(B), koja izražena bitovima<br />

broja B iznosi:<br />

V = bn-1×2 n-1 + ... + b2×2 2 + b1×2 1 + b0<br />

= 2×(bn-1×2 n-2 + ... + b1×2 0 ) + b0<br />

Ako V podelimo sa 2, rezultat možemo napisati u obliku:<br />

V R<br />

= Q +<br />

2 2<br />

gde je Q= bn-1×2 n-2 + ... + b1×2 0 celobrojni količnik, koji se može napisati u obliku Q0=<br />

2×(bn-1×2 n-3 + ... + b2×2 0 ) + b1, a R ostatak, R0=b0. Ponovno deljenje sa 2 daje Q0/2= Q1 +<br />

R1/2, gde se Q1 može napisati kao Q1 = 2×(bn-1×2 n-4 + ... + b3×2 0 ) + b2, a R1=b1. Znači,<br />

uzastopnim deljenjem celobrojnih količnika Qi sa 2, sve dok količnik ne postane jednak nuli,<br />

generiše se sekvenca ostataka (b0, b1, ..., bn-1). Uočimo da se ovim postupkom konverzije kao<br />

prvi određuje bit najmanje, a kao poslednji bit najveće težine ekvivalentnog binarnog broja.<br />

Opisani postupak se može direktno uopštiti na konverziju decimalnog broja u proizvoljnu<br />

osnovu r. Naime, ostaci koji se dobijaju uzastopnim deljenjem decimalnog broj sa r<br />

predstavljaju cifre ekvivalentnog broja iz osnove r.<br />

Primer 5-1: 17910→N2<br />

N/2 Q R<br />

3

Primer. 5-2: 3415 → N10<br />

Primer 5-3: 18310→N5<br />

Primer: 5-4: 2013→N5<br />

179/2 = 89 1 LSB<br />

89/2 = 44 1<br />

44/2 = 22 0<br />

22/2 = 11 0<br />

11/2 = 5 1<br />

5/2 = 2 1<br />

2/2 = 1 0<br />

1/2 = 0 1 MSB<br />

17910 = 110011012<br />

3415 = (3×5 2 + 4×5 1 + 1×5 0 )10<br />

= (75 + 20 + 1)10<br />

= (96)10<br />

N/5 Q R<br />

183/5 = 36 3<br />

36/5 = 7 1<br />

7/5 = 1 2<br />

1/5 = 0 1<br />

18310 = 12135<br />

Konverzija između dva nedecimalna sistema se najlakše sprovodi ako se kao među-korak<br />

koristi konverzija u decimalni sistem. Tako, broj 2013 treba prvo prevesti u decimalni<br />

broj, 2033→N10, a zatim dobijeni broj konvertovati u osnovu 5, N10→N5:<br />

2033→N10: 2013 = (2×3 2 + 0×3 1 + 1×3 0 )10<br />

1910→N5:<br />

2033→345<br />

= (18 + 1)10<br />

= 1910<br />

N/5 Q R<br />

19/5 = 3 4<br />

3/5 = 0 3<br />

1910 = 345<br />

4

<strong>5.</strong>1.2 Oktalna i heksadecimalna reprezentacija<br />

Projektanti digitalnog hardvera, u svom radu, pored decimalnog i binarnog, često koriste<br />

još dva brojna sistema: oktalni i heksadecimalni. Osnova oktalnog brojnog sistema je 8, a<br />

heksadecimalnog 16. U oktalnom sistemu, opseg cifara je 0 do 7. U heksadecimalnom<br />

sistemu postoji 16 cifara. Za označavanje prvih 10, koriste se iste cifre kao u decimalnom<br />

sistemu, tj. 0 do 9. Za označavanje heksadecimalnih cifara čije su decimalne vrednosti 10, 11,<br />

12, 13, 14 i 15 koriste se redom slova: A, B, C, D, E i F. U tabeli sa Sl. 5-1 navedeni su zapisi<br />

prvih 19 celih <strong>brojeva</strong> u četiri brojna sistema.<br />

Decimalni Binarni Oktalni Heksadecimalni<br />

00 00000 00 00<br />

01 00001 01 01<br />

02 00010 02 02<br />

03 00011 03 03<br />

04 00100 04 04<br />

05 00101 05 05<br />

06 00110 06 06<br />

07 00111 07 07<br />

08 01000 10 08<br />

09 01001 11 09<br />

10 01010 12 0A<br />

11 01011 13 0B<br />

12 01100 14 0C<br />

13 01101 15 0D<br />

14 01110 16 0E<br />

15 01111 17 0F<br />

16 10000 20 10<br />

17 10001 21 11<br />

18 10010 22 12<br />

Sl. 5-1 Reprezentacija <strong>brojeva</strong> u četiri brojna sistema.<br />

Kod digitalnih sistema dominira binarni brojni sistem. Razlog za korišćenje oktalnog i<br />

heksadecimalnog brojnog sistema leži u činjenici da oni omogućavaju skraćeno zapisivanje<br />

binarnih <strong>brojeva</strong>. Naime, jedna oktalna cifra predstavlja 3, a jedna heksadecimalna cifra 4<br />

bita. Binarni broj se prevodi u oktalni tako što se izdvajaju grupe od po 3 bita, počev od bita<br />

najmanje težine, i svaka grupa zamenjuje odgovarajućom oktalnom cifrom. Na primer,<br />

binarna sekvenca 101011111010100 se konvertuje u oktalni zapis na sledeći način:<br />

što znači (101011111010100)2 = (51724)8. Ako broj bita nije umnožak trojke, tada treba<br />

dodati odgovarajući broj nula sa leve strane. Na primer, (1101100)2 = (154)8:<br />

Slično, binarni broj se prevodi u heksadecimalni razvrstavanjem bitova u grupe od po 4<br />

bita. Tako, 16-bitni broj se predstavlja sa 4 heksadecimalne cifre. Na primer,<br />

(0101100111011010)2 = (59DA)16:<br />

5

Ako broj bitova nije umožak četvorke, tada, pre konverzije, sa leve strane treba dopisati<br />

odgovarajući broj nula. Na primer, (111100)2 = (3C)16:<br />

Konverzija oktalnog (heksadecimalnog) broja u binarni, obavlja se prostom zamenom<br />

oktalnih (heksadecimalnih) cifara sekvencama od 3 (4) bita koje imaju istu brojnu vrednost<br />

kao i cifre koje zamenjuju. Ispod su dati primeri koji ilustruju ovaj postupak:<br />

(603)8 = (110 000 011)2<br />

(A6)16 = (1010 0110)2<br />

Napomenimo da se oktalni brojevi danas retko koriste, iz razloga što većina savremenih<br />

računara i digitalnih sistema operiše sa binarnim brojevima čija je dužina umnožak bajta, npr.<br />

32 ili 64 bita. Ako je broj zapisan u oktalnom sistemu tada je teško direktno odrediti<br />

vrednosti pojedinačnih bajtova. Zato se mnogo češće koristi heksadecimalna notacija, kod<br />

koje dve cifre predstavljaju jedan bajt. Na primer, 32-bitni heksadecimalni broj<br />

(54AB20F3)16 sadrži 4 bajta čije su vrednosti: 5416, AB16, 2016 i F316.<br />

<strong>5.</strong>2 Sabiranje neoznačenih <strong>brojeva</strong><br />

Binarno sabiranje obavlja se sličan način kao decimalno sabiranje, s tom razlikom što<br />

pojedinačne cifre mogu biti samo 0 ili 1. Sabiranje dva jedno-bitna broja, u opštem slučaju,<br />

daje dvo-bitni rezultat, kao što je to ilustrovano na Sl. 5-2a. Ako su oba sabirka 0, tada će i<br />

njihov zbir biti 0, tj. (00)2. Ako je jedan sabirak 0, a drugi 1, zbir je 1, tj. (01)2. Ako su oba<br />

sabirka 1, zbir je 2, tj. (10)2. Bit manje težine ovog zbira zove se bit sume, ili sum, tj. s. Bit<br />

veće težine zove se bit prenosa ili carry, tj. c. Na Sl. 5-2b prikazana je tabela istinitosti koja<br />

definiše operaciju sabiranja dva bita. Lako se može uočiti da je bit sume AND, a bit prenosa<br />

XOR funkcija sabiraka. Na Sl. 5-2c je prikazana logička mreža koja realizuje funkcije s i c.<br />

Kolo koje obavlja sabiranje dva bita zove se polu-sabirač (half-adder - HA). Za<br />

predstavljanje polu-sabirača koristićemo grafički simbol sa Sl. 5-2d.<br />

(a) sabiranje dva bita.<br />

x y<br />

Prenos<br />

cx2 1<br />

Suma<br />

sx2 0<br />

0 0 0 0<br />

0 1 0 1<br />

1 0 0 1<br />

1 1 1 0<br />

(b) tabela istinitosti<br />

6

Sl. 5-2 Polu-sabirač.<br />

Polu-sabirač, razmatran kao izolovano kolo, nema neki veći praktični značaj. Od mnogo<br />

većeg interesa su <strong>kola</strong> koja obavljaju sabiranje više-bitnih <strong>brojeva</strong>. Prilikom sabiranja višebitnih<br />

<strong>brojeva</strong>, kao i kod sabiranja više-cifarskih decimalnih <strong>brojeva</strong>, potrebno je sabrati svaki<br />

par bitova (cifara), ali za svaku bitsku poziciju i dodatno je potrebno uračunati i prenos koji<br />

potiče iz prethodne pozicije, i-1. Na Sl. 5-3 je dat primer sabiranja dva 5-bitna broja<br />

X=(01111)2=(15)10 i Y=(01010)2=(10)10. Sa pet bita moguće je predstaviti cele brojeve iz<br />

opsega 0 do 31. Pošto u konkretnom slučaju važi S=X+Y=(25)10, pet bita biće dovoljna i za<br />

predstavljanje zbira. Uočimo da su na Sl. 5-3, sabirci simbolički označeni sa X=x4x3x2x1x0 i<br />

Y=y4y3y2y1y0. Na ovoj slici su takođe prikazani prenosi koji se generišu u toku sabiranja. Na<br />

primer, prilikom sabiranja bitova x0=1 i y0=0 dobija se suma s0=1 prenos c0=0; prilikom<br />

sabiranja bitova x1=1 i y1=1 dobija se suma s1=0 prenos c1=1 i tako dalje. Za ci kažemo da<br />

predstavlje izlazni prenos (carry-out) iz pozicije i, odnosno ulazni prenos (carry-in) na<br />

poziciju i+1.<br />

U poglavlju X je pokazano kako se projektuju kombinacione mreže polazeći od tabele<br />

istinitosti. Međutim, ovakav pristup nije praktičan za projektovanje sabirača koji treba da<br />

sabira dva 5-bitna broja. 5-bitni sabirač ima 10 ulaza, pa bi za opis njegovog ponašanja bilo<br />

potrebno formirati tabelu istinitosti od 2 10 =1024 vrsta! S toga, bolji pristup je nezavisno<br />

razmatrati sabiranje svakog para bita xi i yi.<br />

Sl. 5-3 Sabiranje više-bitnih binarnih <strong>brojeva</strong>.<br />

Za poziciju i=0 ne postoji ulazni prenos i stoga se sabiranje obavlja na isti način kao na<br />

Sl. 5-2a. Na svakoj od preostalih poziciju i=1,..., n-1, i-ti bitovi sabiraka, xi i yi, se sabiraju<br />

zajedno sa ulaznim prenosom ci. Tako, sada sabiranje na nivou svake bitske pozicije<br />

obuhvata tri bita, xi, yi i ci. Kako najveći zbir tri bita iznosi (11)2, to su za njegovo<br />

predstavljanje, kao i kod sabiranja dva jednobitna broja, potrebna dva bita: suma si, kao bit<br />

manje težine, i izlazni prenos ci+1, kao bit veće težine. Bit sume si predstavlja i-ti bit<br />

konačnog rezultata, dok se bit prenosa ci+1 pridodaje poziciji i+1 kao ulazni prenos. Funkcije<br />

sume i izlaznog prenosa definisane su tabelom istinitosti sa Sl. 5-4a. Bit sume si je zbir po<br />

modulu 2 bitova xi, yi i ci. Drugim rečima, bit sume je jednak 1 ako neparan broj sabiraka ima<br />

vrednost 1, odnosno, 0 ako paran broj sabiraka ima vrednost 1. Izlazni prenos ci+1 jednak je 1<br />

ako je zbir bitova xi, yi i ci veći od 1. Karnoove mape za funkcije si i ci+1 prikazane su na Sl.<br />

5-4a. Na osnovu Karnoovih mapa u mogućnosti smo da izvedemo optimalne izraze oblika<br />

zbir-proizvoda za funkcije ci+1 i si:<br />

ci+1 = xiyi + xici + yici<br />

si = xi’yici’+xiyi’ci’+xi’yi’ci+xiyici<br />

7

Efikasnija realizacija funkcija si i ci+1 može se postići korišćenjem XOR <strong>kola</strong>. XOR<br />

funkcija od dve promenljive definisana je izrazom x1⊕x2 = x1x2’ + x1’x2. Primenom<br />

algebarskih manipulacija, izraz za bit sume može se svesti na formu koja sadrži samo XOR<br />

<strong>kola</strong>, na sledeći način:<br />

si = (xi’yi+xiyi’)ci’+( xi’yi’+xiyi)ci<br />

= (xi’yi+xiyi’)ci’+( xi’yi+xiyi’)’ci<br />

= (xi ⊕ yi)ci’+(xi ⊕ yi)’ci<br />

= (xi ⊕ yi)⊕ ci<br />

U suštini, si predstavlja XOR funkcija od tri promenljive. Napomenimo, da je za XOR<br />

funkciju karakterističan naizmeničan raspored jedinica u Karnoovoj mapi, koji je takav da<br />

onemogućava sažimanje minterma (Sl. 5-4b).<br />

Izraz za funkciju ci+1, takođe, možemo preurediti na način da koristi XOR funkciju. Pri<br />

tome, trebe poći od izraza oblika zbir-minterma:<br />

ci+1 = cixi’yi + cixiyi + cixiyi’ + ci’xiyi<br />

= (ci +ci’)xiyi + ci(xi’yi + cixiyi’)<br />

= xiyi + ci(xi ⊕ yi)<br />

Uočimo da se član (xi⊕ yi) javlja u izrazima za obe funkcije si i ci+1. Ova činjenica<br />

omogućava da se prilikom realizacije funkcija si i ci+1 za izračunavanje člana (xi⊕ yi) koristi<br />

jedinstveno XOR kolo. Kombinaciona mreža koja realizuje funkcije si i ci+1 prikazana je na<br />

Sl. 5-4c. Ovo kolo se zove potpuni-sabirač (full-adder - FA). Grafički simbol potpunog<br />

sabirača prikazan je na Sl. 5-4d.<br />

Sl. 5-4 Potpuni sabirač.<br />

⊕ ⊕ ⊕<br />

8

Imajući u vidu imena <strong>kola</strong>, polu- i potpuni-sabirač, mogli bi smo naslutiti da je potpunisabirač<br />

moguće konstruisati pomoću dva polu-sabirača. Zaista, ako pažljivo pogledamo<br />

kombinacionu mrežu potpunog sabirača sa Sl. 5-4c, možemo učiti da se u njoj kruju dva<br />

polu-sabirača, uz dodatak jednog OR <strong>kola</strong> preko koga se formira izalaz ci+1, kao što je to<br />

naznačeno na Sl. 5-5a. Na Sl. 5-5b je prikazana blok šema potpunog sabirača realizovanog<br />

pomoću polu-sabirača.<br />

Sl. 5-5 Realizacija potpunog sabirača na bazi polu-sabirača.<br />

<strong>5.</strong>2.1 Sabirač sa rednim prenosom<br />

Kao što dobro znamo, ručno sabiranje se obavlja tako što se krene od cifre najmanje<br />

težine i redom sabiraju parovi cifara, sve do cifre najveće težine. Ako se na poziciji i javi<br />

prenos, tada se on dodaje ciframa na poziciji i+1. Identičan postupak se može primeniti i za<br />

konstrukciju digitalnog <strong>kola</strong> koje će obavljati sabiranje binarnih <strong>brojeva</strong>. Binarni sabirač se<br />

formira rednim povezivanjem potpunih sabirača, tako što izlazni prenos svakog potpunog<br />

sabirača služi kao ulazni prenos za potpuni sabirač koji zauzima prvu narednu bitsku poziciju<br />

veće težine. Ovakva vrsta sabirača se zove sabirač sa rednim prenosom ili RCA, prema<br />

engleskom nazivu Ripple-Carry Adder. Struktura n-to bitnog sabirača sa rednim prenosom<br />

prikazana je na Sl. 5-6a. Ova struktura se predstavlja grafičkim simbolom sa Sl. 5-6b.<br />

U opštem slučaju, zbir dva neoznačena n-to bitna broja ima n+1 bita. Kod binarnog<br />

sabirača, ovaj dodatni (n+1)-vi bit je predstavljen bitom izlaznog prenosa iz pozicije najveće<br />

težine, cn, tako da važi:<br />

(cnsn-1…s1s0) = (xn-1…x1x0) + (yn-1…y1y0).<br />

Međutim, digitalni sistemi obično manipulišu brojevima fiksnog obima, npr. 8, 16, 32 ili<br />

64 bita. Rezultat koji ima veći broj bita jednostavno ne bi mogao biti dalje procesiran od<br />

strane takvog sistema. Zato se izlazni prenos cn obično ne koristi kao deo sume, već kao<br />

indikacija prekoračenja dozvoljenog opsega rezultata.<br />

9

(a) unutrašnja struktura;<br />

(b) grafički simbol<br />

Sl. 5-6 n-bitni sabirač sa rednim prenosom.<br />

U strukturi sa Sl. 5-6a, proces izračunavanja počinje onog trenutka kada se na ulaze<br />

sabirača postavi novi par operanada X i Y. Međutim, s obzirom da svaki gejt u svakom<br />

potpunom sabiraču unosi izvesno kašnjenje, korektna vrednost izlazne sume S se ne generiše<br />

istog tog trenutka, već tek nakon nekog vremena. Da bi se u stepenu n-1 odredio bit sume sn-1<br />

neophodna je informacija o prenosu iz stepena n-2, tj. cn-1; da bi se u stepenu n-2 odredio<br />

izlazni prenos cn-1 potrebno je imati informaciju o vrednosti cn-2, i td. Neka kašnjenje<br />

potpunog sabirača iznosi ∆t – vreme od postavljanja ulaza xi, yi, ci do generisanja korektnih<br />

izlaza ci+1 i si. Izlazni prenos iz prvog stepena, c1, stiže do drugog stepena posle vremena ∆t<br />

nakon što su postavljeni x0 i y0. Izlazni prenos iz drugog stepena, c2, stiže do ulaza trećeg sa<br />

kašnjenjem od 2∆t, i td. Signal cn-1 je važeći posle kašnjenja od (n-1)∆t, a celokupna izlaza<br />

suma posle kašnjenja od n∆t.<br />

Napomenimo da vreme sabiranja zavisi i od vrednosti operanada. Kašnjenje od n∆t<br />

odgovara slučaju kada je jedan operand 11...11, a drugi 00...01. U ovom slučaju, prenos koji<br />

se javlja na poziciji 0, prenosi se kroz sve potpune sabirače postavljajući bitove sume na 0. Za<br />

bilo koji drugi par vrednosti operanada, kašnjenje će biti kraće. Na primer, sabiranje <strong>brojeva</strong><br />

00...00 i 00...01 traje samo ∆t. U opštem slučaju, vreme sabiranja određeno je najvećim<br />

brojem uzastopnih pozicija na kojima oba operanda imaju vrednost 1. Međutim, kao se<br />

sabirači koriste za sabiranje operanada proizvoljnih vrednosti, u radu sa sabiračem moramo<br />

računati sa maksimalnim kašnjenjem, n∆t, kako bi smo bili sigurni da ćemo sa izlaza sabirača<br />

uvek očitati ispravan rezultat.<br />

Znači, brzina rada sabirača sa rednim prenosom određena je vremenom prostiranja<br />

signala prenosa kroz potpune sabirače. Što je broj bita koji se sabira veći, to je brzina rada<br />

manja. Ako se radi sa brojevima velike dužine, 32 ili 64 bita, vreme sabiranja može biti<br />

10

neprihvatljivo dugo. Napomenimo da je sabirač sa rednim prenosom samo jednu od većeg<br />

broja različitih konstrukcija sabiračkih <strong>kola</strong>, koje se razlikuju po složenosti (ukupan broj<br />

gejtova) i brzini rada. Sabirač sa rednim prenosom je najjednostavnija, ali ujedno i najsporija<br />

varijanta. Konstrukcija brzih sabiračkih <strong>kola</strong> biće tema odeljka X.<br />

U dosadašnjoj diskusiji razmatrali smo isključivo neoznačene binarne brojeve. Sabiranje<br />

neoznačenih <strong>brojeva</strong> ne zahteva ulazni prenos u stepen 0, tj. c0. Bez obzira na to, ulaz c0 je<br />

prikazan na dijagramu sa Sl. 5-6a, kako bi smo istu strukturu mogli da koristimo i za<br />

oduzimanje binarnih <strong>brojeva</strong>, kao što će to biti pokazano u odeljku X.<br />

Binarni sabirači sa rednim prenosom se lako sprežu kako bi se formirale sabiračke mreže<br />

za veći broj bitova. Na Sl. 5-7 je pokazano kako se sa dva n-bitna sabirača formira 2n-bitni<br />

sabirač.<br />

Sl. 5-7 Sprezanje binarnih sabirača.<br />

Primer. 5-5 Projektovati kolo za množenje neoznačenog 8-bitnog broja konstantom 3.<br />

Odgovor: Neka je A=a7a6…a1a0 i P=3A. Za predstavljanje broja P potrebna su 10 bita:<br />

P=p9p8…p1p0. Pošto važi 3A=A+A+A, za realizaciju <strong>kola</strong> možemo upotrebiti binarne<br />

sabirače. Na Sl. 5-8a je prikazano rešenje koje koristi dva sabirača. Pri sabirač generiše<br />

A+A=2A. Njegov rezultat je predstavljen sa 9 bita: 8 bita sume i izlazni prenos sa pozicije<br />

najveće težine. Drugi sabirač računa 2A+A=3A. Ovaj sabirač je 9-to bitni, iz razlog što<br />

jedan od njegovih operanada, 2A, ima 9 bita. Uočimo da je ulaz x8 drugog sabirača<br />

povezan je na konstantu 0, s obzirom da A ima 8-bita.<br />

Na Sl. 5-8b je prikazano efikasnije rešenje, koje koristi samo jedan 9-bitni sabirač.<br />

Uočimo da je 8-bitni sabirač u rešenju sa Sl. 5-8a nepotreban, s obzirom da se 2A može<br />

dobiti prostim pomeranjem bitova broja A za jednu poziciju na levo, što daje:<br />

2A=a7a6…a1a00. (Ispravnost poslednjeg izraz se može lako proveriti na osnovu jednačine<br />

(<strong>5.</strong>2)). Za obavljanje ovog pomeranja nije potrebno nikakvo kolo, već je dovoljno dopisati<br />

jednu nulu sa desne strane broja, što upravo odgovara načinu na koji je operand A<br />

povezan sa Y ulazom sabirača.<br />

Uočimo, sada, da je u rešenju sa Sl. 5-8b, ulaz najmanje težine sabirača x0 fiksno<br />

postavljen na x0=0. To znači da će bit sume s0 uvek imati vrednost s0=a0. Ovo zapažanje<br />

nam omogućava da dodatno pojednostavimo rešenje, tako što ćemo 9-bitni sabirač<br />

zameniti 8-bitnim, kao na Sl. 5-8c.<br />

11

<strong>5.</strong>3 Označeni brojevi<br />

Sl. 5-8 Kolo koje množi 8-bitni neoznačeni broj sa 3.<br />

U decimalnom brojnom sistemu, znak broja se označava simbolom + ili – levo od cifre<br />

najveće težine. U binarnom brojnom sistemu, znak broja se označava dodatnim bitom koji u<br />

zapisu broja zauzima krajnju levu poziciju. Za pozitivne brojeve, ovaj bit jednak je 0, a za<br />

negativne 1. Znači, kod označenih <strong>brojeva</strong>, krajnji levi bit ukazuje na znak broja, dok se<br />

preostalih n-1 bita predstavlja maginitudu ili apsolutnu vrednost broja, kao što je prikazano<br />

na Sl. 5-9. Važno je zapaziti poziciju bita najveće težine (MSB). Kod neoznačenih <strong>brojeva</strong><br />

svih n bita predstavljaju magnitudu broja – kaže se da su svi bitvi značajni, a MSB se nalazi<br />

poziciji n-1. Kod označenih <strong>brojeva</strong>, značajni su n-1 bita, MSB bit se nalazi na poziciji n-2,<br />

dok bit na poziciji n-1 ukazuje na znak broja.<br />

Sl. 5-9 Formati predstavljana celih <strong>brojeva</strong>.<br />

<strong>5.</strong>3.1 <strong>Predstavljanje</strong> negativnih <strong>brojeva</strong><br />

Za razliku od pozitivnih <strong>brojeva</strong> koji se predstavljaju uvek na isti način, korišćenjem<br />

pozicionog brojnog sistema, za predstavljanje negativnih <strong>brojeva</strong> u upotrebi su tri<br />

reprezentacije: znak-magnituda, jedinični komplement i dvojični komplement.<br />

Znak-magnituda<br />

Kod decimalnog brojnog sistema, magnituda pozitivnih i negativnih <strong>brojeva</strong> predstavlja<br />

se na isti način, a znak je taj koji ukazuje da li se radi o pozitivnom ili negativnom broju.<br />

Ovakav način predstavljanja označenih <strong>brojeva</strong> zove se znak-magnituda, ili znak-apsolutna<br />

vrednost. Ista reprezentacija može se primeniti i na binarne brojeve, a razlika je samo u<br />

12

načinu kodiranja znaka: umesto + i – koristimo 0 i 1. Na primer, +5 = 0101, a -5=1101. Ispod<br />

je navedeno nekoliko 8-bitnih celih <strong>brojeva</strong> u formatu znak-magnituda i njihovi decimalni<br />

ekvivalenati:<br />

(01010101)2 = (+85)10 (11010101)2 = (-85)10<br />

(01111111)2 = (+127)10 (11111111)2 = (-127)10<br />

(00000000)2 = (+0)10 (10000000)2 = (-0)10<br />

Brojni sistem koji koristi reprezentaciju znak-magnituda sadrži isti broj pozitivnih i<br />

negativnih <strong>brojeva</strong>, a nula ima dvojnu reprezentaciju. Najveći pozitivni broj koji se u ovom<br />

sistemu može iskazati sa n bita je +(2 n -1) = 011…11; najmanji negativni broj je –(2 n -1) =<br />

111…11, dok se nula predstavlja sa 000…00 ili 100…00.<br />

Zbog sličnosti sa decimalnim sistemom, reprezentacija znak-magnituda je lako razumljiva<br />

i lako čitljiva. Međutim, iz razloga na koje će kasnije biti ukazano, ona nije pogodna za<br />

primenu kod digitalnih sistema. Pogodniji načini za predstavljanje označenih binarnih<br />

<strong>brojeva</strong> su komplementarne reprezentacije.<br />

Jedinični komplement<br />

U komplementarnom brojnom sistemu, negativni brojevi se definišu preko operacije<br />

komplementiranja koja se primenjuje na njima odgovarajuće pozitivne brojeve.<br />

Razmatraćemo dva komplementarna sistema: jedinični komplement i dvojični komplement,<br />

koji se razlikuju u definiciji operacije komplementiranja <strong>brojeva</strong>. U formatu jediničnog<br />

komplementa, n-bitna reprezentacija negativnog broja K se dobija oduzimanjem njemu<br />

odgovarajućeg pozitivnog broja P od 2 n -1, tj. K=(2 n -1)-P. Na primer, ako je n=4, tada je K =<br />

(2 4 -1)-P = (15)10-P = (1111)2-P. Ako +5 konvertujemo u negativan broj, dobićemo -5 = 1111<br />

– 0101 = 1010. Slično, +3=0011, a -3 = 1111 – 0011 = 1100. Jasno se uočava da se jedinični<br />

komplement datog binarnog broja dobija komplementiranjem svakog pojedinačnog bita,<br />

uključujući i bit znaka.<br />

Ispod je navedeno nekoliko 8-bitnih <strong>brojeva</strong> i njihovih jediničnih komplemenata:<br />

Najveći pozitivni broj koji se može predstaviti u jediničnom komplementu sa n bita je<br />

011…11 = 2 n -1, najmanji negativni broj je 100…00 = -(011…11)2 = -(2 n -1), dok nula ima<br />

dvojnu reprezentaciju: 000…00 ili 111…11.<br />

Brojni sistem jediničnog komplementa se može interpretirati i kao pozicioni brojni sistem<br />

kod koga bit znaka ima težinu –(2 n -1). Ako je B=bn-1bn-2...b1b0 binarni broj predstavljen u<br />

formatu jediničnog komplementa, tada je njegova vrednost:<br />

V<br />

( B)<br />

= b<br />

n−<br />

1<br />

× [ −(<br />

2<br />

n<br />

−1)]<br />

+<br />

∑ − n 2<br />

i<br />

i=<br />

0<br />

i<br />

b × 2<br />

13

Na primer, odredimo vrednost binarnog broja 1010 pod pretpostavkom da je broj<br />

predstavljen u jediničnom komplementu:<br />

V(1010) = 1×[-(2 3 -1)] + 0×2 2 + 1×2 1 + 0×2 0<br />

= (-7+0+2+0)10<br />

= (-5)10<br />

Jedinični komplement se lako izvodi, ali ispoljava izvesne nedostatke kada se koristi u<br />

aritmetičkim operacijama, o čemu će više reči biti u sledećem odeljku.<br />

Dvojični komplement<br />

U formatu dvojičnog komplementa, n-bitna reprezentacija negativnog broja K se dobija<br />

oduzimanjem njemu odgovarajućeg pozitivnog broja P od 2 n , tj. K = 2 n - P. Na primer, ako je<br />

n = 4, tada je K = 2 4 - P = (16)10 - P = (10000)2 - P. Da bi smo odredili dvojični komplement<br />

broja 5, treba obaviti oduzimanje 10000 – 0101, što daje -5 = 1011. Ili -3 = 10000 – 0011 =<br />

1101. Nalaženje dvojičnog komplementa na ovaj način je naporno jer zahteva da se obavi<br />

operacija oduzimanja. Međutim, ako je K1 jedinični, a K2 dvojični komplement broja P tada<br />

važi:<br />

K1 = (2 n -1) – P<br />

K2 = 2 n – P<br />

Odakle sledi K2 = K1 + 1. Dakle, jednostavniji način za nalaženje dvojičnog komplementa<br />

sastoji se u tome da se na jedinični komplement doda jedinica. Ovo je upravo način na koji se<br />

u digitalnoj tehnici dobija dvojični komplement. Ispod je navedeno nekoliko primera<br />

određivanja dvojičnog komplementa 8-bitnih <strong>brojeva</strong>:<br />

U jednom od gore navedenih slučajeva, konkretno, prilikom nalaženja dvojičnog<br />

komplementa nule, prilikom sabiranja jedinice sa jediničnim komplementom, pojavio se<br />

izlazni prenos iz pozicije najveće težine. Međutim, u radu sa dvojičnim komplementom,<br />

izlazni prenos se ignoriše i u obzir uzima samo n bita najmanje težine.<br />

Za ručno izvođenje postoji još jedan lakši način za nalaženje dvojičnog komplementa.<br />

Neka je dat broj B=bn-1bn-2 ... b1b0. Dvojični komplement broja B, K=kn-1kn-2 ... k1k0, može se<br />

odrediti na sledeći način: krećemo od bita najmanje težine na levo i prepisujemo bitove broja<br />

14

B sve dok ne naiđemo na prvu jedinicu, zatim prepisujemo i ovu jednici, a preostale bitove<br />

komplementiramo. Na primer, ako je B=0110, tada prepisujemo k0=b0=0 i k1=b1=1, i<br />

komplementiramo preostale bitove, k2=b2`=0 i k3=b3`=1. Znači, K=1010. Ili, na složenijm<br />

primeru, ako je B=101101000, tada je K= 010011000.<br />

U brojnom sistemu koji koristi dvojični komplement, nula se tretira kao pozitivan broj, i<br />

predstavlja na jedinstveni način: 000...00. Iz tog razloga broj pozitivnih <strong>brojeva</strong> je za jedan<br />

manji od broja negativnih. Naime, najveći pozitivni broj koji se može predstaviti sa n bita u<br />

formatu dvojičnog komplementa je 011...11 = 2 n -1, dok je najmanji negativan broj 10000000<br />

= -(011...11 + 1)2 = -(100...00)2 = -2 n .<br />

Brojni sistem dvojičnog komplementa se može interpretirati i kao pozicioni brojni sistem<br />

kod koga bit znaka ima težinu –2 n . Ako je B=bn-1bn-2...b1b0 binarni broj predstavljen u<br />

formatu dvojičnog komplementa, tada je njegova vrednost:<br />

V ( B)<br />

= −b<br />

n−<br />

1<br />

× 2<br />

n−1<br />

+<br />

∑ − n 2<br />

i=<br />

0<br />

i<br />

2 × b<br />

i<br />

Na primer, odredimo vrednost binarnog broja 1010 pod pretpostavkom da je broj<br />

predstavljen u dvojičnom komplementu:<br />

V(1010) = 1×(-2 3 ) + 0×2 2 + 1×2 1 + 0×2 0<br />

= (-8+0+2+0)10<br />

= (-6)10<br />

Tabela sa Sl. 5-10 ilustruje interpretaciju svih 16 4-bitnih kombinacija u tri razmatrana<br />

sistema za predstavljanje označenih <strong>brojeva</strong>. Uočimo da kod reprezentacija znak-magnituda i<br />

jedinični komplement postoje po dve binarne kombinacije koje predstavljaju vrednost nula.<br />

Kod dvojičnog komplementa postoji samo jedna takva kombinacija. Takođe, uočimo da je<br />

opseg <strong>brojeva</strong> koji se mogu predstavti sa 4 bita kod dvojičnog komplementa -8 do 7, dok je<br />

kod preostale dve reprezentacije -7 do 7.<br />

<strong>5.</strong>3.2 Sabiranje i oduzimanje<br />

b0b1b2b3<br />

znakmagnituda<br />

jedinični<br />

komplement<br />

dvojični<br />

komplement<br />

0111 +7 +7 +7<br />

0110 +6 +6 +6<br />

0101 +5 +5 +5<br />

0100 +4 +4 +4<br />

0011 +3 +3 +3<br />

0010 +2 +2 +2<br />

0001 +1 +1 +1<br />

0000 +0 +0 +0<br />

1000 -0 -7 -8<br />

1001 -1 -6 -7<br />

1010 -2 -5 -6<br />

1011 -3 -4 -5<br />

1100 -4 -3 -4<br />

1101 -5 -2 -3<br />

1110 -6 -1 -2<br />

1111 -7 -0 -1<br />

Sl. 5-10 Interpretacija 4-bitnih označenih celih <strong>brojeva</strong>.<br />

U prethodnom odeljku opisana su tri standardna načina za binarnu reprezentaciju <strong>brojeva</strong>.<br />

Međutim, nisu svi ovi načini podjednako pogodni za primenu u digitalnim sistemima.<br />

15

Osnovni kriterijum za izbor reprezentacije <strong>brojeva</strong> je lakoća sa kojom se nad brojevima u<br />

konkretnoj reprezentaciji obavljaju osnovne računske operacije, kao što su sabiranje i<br />

oduzimanje. U ovom odeljku, na konkretnim primerima, ukazaćemo na dobre i loše strane<br />

svake od tri reprezentacije.<br />

Sabiranje pozitivnih <strong>brojeva</strong> se obavlja na isti način u sve tri reprezentacije, tj. na isti<br />

način kao sabiranje neoznačenih <strong>brojeva</strong> (odeljak X). Međutim, kada se u računicu uvedu i<br />

negativni brojevi, između različitih reprezentacija ispoljavaju se značajne razlike.<br />

Sabiranje <strong>brojeva</strong> u formatu znak-magnituda<br />

Ako oba sabirka imaju isti znak, sabiranje <strong>brojeva</strong> u formatu znak-magnituda je<br />

jednostavno. Magnitude se saberu, a zbiru se dodeli znak sabiraka. Međutim, ako su sabirci<br />

različitog znaka, sabiranje postaje složenije. U tom slučaju, operacija sabiranja se svodi na<br />

oduzimanje manjeg broja od većeg. To znači da je za obavljanje operacije sabiranja<br />

neophodno digitalno kolo koje će ispitati znake sabiraka, uporediti njihove magnitue i biti u<br />

mogućnosti da u zavisnosti od ishoda poređenja obavi sabiranje ili oduzimanje. Složenost<br />

takvog <strong>kola</strong> je značajno veća od odgovarajućih <strong>kola</strong> koja barataju brojevima u<br />

komplementarnim reprezentacijama. Iz tog razloga reprezentacija znak-magnituda se ne<br />

koristi kod digitalnih sistema.<br />

Sabiranje <strong>brojeva</strong> u jediničnom komplementu<br />

Očigledna prednost jediničnog u odnosu na dvojični komplement je u tome što se<br />

negativni broj lako određuje prostim komplementiranjem svih bitova odgovarajućeg<br />

pozitivnog broja. Na Sl. 5-11 je prikazano šta se dešava prilikom sabiranja dva broja<br />

predstavljena u jediničnom komplementu. Navedena su četiri slučaja, pri čemu svaki slučaj<br />

odgovara jednoj konkretnoj kombinaciji znakova sabiraka. Kao što se može videti na gornjoj<br />

polovini slike, izračunavanja 5 + 2 = 7 i (-5) + 2 = (-3) su trivijalna; prostim binarnim<br />

sabiranjem operanada, uključujuči pri tome i bit znaka, dobija se ispravan rezultat. Međutim,<br />

to nije slučaj kod preostala dva primera. Izračunavanje 5 + (-2) = 3 daje bit vektor 10010.<br />

Prvo, rezultat ima pet, a ne četiri bita. Dodatni peti bit je posledica izlaznog prenosa sa<br />

pozicije znaka. Drugo, preostala četiri bita predstavljaju broj 2, a ne 3, što je očigledno<br />

pogrešan rezultat. Međutim, ako uzmemo izlazni prenos sa pozicije znaka i dodamo ga<br />

rezultatu na poziciji najmanje težine, novi rezultat biće ispravna suma, tj. 3. Slična situacija<br />

se javlja kod sabiranja (-5) + (-2) = (-7). Nakon inicjalnog sabiranja, rezultat je pogrešan, zato<br />

što su četiri bita sume 0111, što predstavlja +7, a ne -7. Ali, ponovo, tu je izlazni prenos iz<br />

pozicije bita znaka koji može biti iskorišćen za korekciju rezultata, na način kako je<br />

prikazano na Sl. 5-11.<br />

Sl. 5-11 Primeri sabiranja u jedničnom komplementu.<br />

Zaključak koji se nameće na osnovu razmatranih primera je da sabiranje <strong>brojeva</strong> u<br />

jediničnom komplementu u nekim slučajevima jednostavno, a u nekima nije. Ako je potrebna<br />

korekcija, neophodno je dodatno vreme kako bi se obavilo sabiranje inicijalnog rezultata i<br />

16

izlaznog prenosa. Tako, ukupno vreme sabiranja može biti i dvostruko duže od vremena<br />

sabiranja dva neoznačena broja.<br />

Sabiranje <strong>brojeva</strong> u dvojičnom komplementu<br />

Razmotrimo istu kombinaciju <strong>brojeva</strong> koju smo koristili u primerima za jedinični<br />

komplement. Na Sl. 5-12 je ilustrovano kako se obavlja sabiranje <strong>brojeva</strong> predstavljenih u<br />

dvojičnom komplementu. Sabiranja 5 + 2 = 7 i (-5) + 2 = (-3) su trivijalna. Izračunavanje 5 +<br />

(-2) = 3 daje ispravna četiri bita rezultata, 0011. Pri tome, izlazni prenos iz pozicije bita<br />

znaka, koji u ovom slučaju postoji, možemo, prosto, ignorisati. Četvrti slučaj je (-5) + (-2) =<br />

(-7). Ponovo, četiri bita rezultata, 1001, odgovaraju ispravnoj sumi (-7). I u ovom slučaju,<br />

izlazni prenos iz pozicije bita znaka se može ignorisati.<br />

Sl. 5-12 Primeri sabiranja u dvojičnom komplementu.<br />

Prethodni primeri pokazuju da je sabiranje <strong>brojeva</strong> u dvojičnom komplementu veoma<br />

jednostavno. Brojevi se sabiranju zajedno sa bitom znaka, a rezultat je uvek ispravan.<br />

Eventualni izlazni prenos iz pozicije bita znaka se jednostavno ignoriše. Znači, procedura<br />

sabiranja je uvek ista, nezavisno od znaka operanada, i može se obaviti binarnim sabiračem,<br />

kao što je onaj sa Sl. 5-6. Zbog svega toga, reprezentacija <strong>brojeva</strong> u dvojičnom komplementu<br />

je veoma pogodna za primenu u digitalnim sistemima.<br />

Oduzimanje u dvojičnom komplementu<br />

Najlakši način da se obavi oduzimanje je da se najpre umanjiocu promeni znak, a da se<br />

onda dobijena vrednost sabere sa umanjenikom. Promeni znaka umanjioca odgovara<br />

nalaženje njegovog dvojičnog komplementa. Na Sl. 5-13 je na nekoliko karakterističnih<br />

primera ilustrovan ovaj postupak. Operacija 5 – (+2) = 3 uključuje nalaženje dvojičnog<br />

komplementa broja +2, što daje 1110. Kada se ovaj broj sabere sa 0101 = (+5), dobija se<br />

rezultat 0011 = (+3) uz generisanje prenosa iz pozicije bita znaka. Ako ignorišemo prenos,<br />

rezultat je tačan. Slična situacija postoji za (-5) + (+2) = (-7). U preostala dva slučaja, izlazni<br />

prenos ne postoji i rezultat je tačan.<br />

Sl. 5-13 Primeri oduzimanja u dvojičnom komplementu.<br />

Sl. 5-14 predstavlja jednu vizuelnu ilustraciju procesa sabiranja i oduzimanja 4-bitnih<br />

<strong>brojeva</strong> u dvojičnom komplementu. Slika prikazuje brojčanik po čijem obodu su raspoređene<br />

17

svih 16 4-bitnih kombinacija. Ako bi smo ove binarne kombinacije interpretirali kao<br />

neoznačene cele brojeve, tada bi one predstavljale brojeve od 0 do 1<strong>5.</strong> Ako ih tretiramo kao<br />

brojeve u dvojičnom komplementu, tada njima odgovara opseg celih označenih <strong>brojeva</strong> od -8<br />

do 7, kao što je naznačeno po unutrašnjem obodu brojčanika. Kazaljku brojčanika možemo<br />

podesiti na bilo koji broj, a zatim na taj broj možemo dodati broj +n tako što ćemo odbrojati n<br />

puta unapred, tj. okrenuti kazaljku za n koraka u smeru kretanja kazaljke na časovniku. Jasno<br />

je da okretanjem kazalje za n koraka u suprotnom smeru, od polaznog broja oduzimamo broj<br />

n. Naravno, rezultat ovog postupka će biti tačan samo ako je n dovoljno malo da kazaljka<br />

prilikom okretanje ne pređe granicu između +7 i -8.<br />

Sl. 5-14 Grafička reprezentacija 4-bitnih <strong>brojeva</strong> u dvojičnom komplementu.<br />

Interesantno je uočiti još i sledeće. Krajnja pozicija kazaljke biće ista bilo da se ona<br />

okrene za n koraka u jednom smeru ili za 16-n koraka u suprotnom smeru. Dakle, umesto da<br />

radimo sa brojčanikom čija kazaljka može da se okreće u oba smera, možemo koristiti<br />

brojčanik sa kazaljkom koja se okreće samo u smeru kretanja kazaljke na časovniku<br />

(odgovara sabiranju), a da u slučajevima kada želimo da obavimo oduzimanje, prethodno<br />

preračunamo broj koraka po formuli 16-n. Uočimo da 16-n predstavlja upravo dvojični<br />

komplement broja n, a da ova grafička interpretacija potvrđuje naše ranije tvrđenje da se<br />

oduzimanje <strong>brojeva</strong> u dvojičnom komplementu može obaviti sabiranjem umenjenika i<br />

dvojičnog komplementa umanjioca.<br />

<strong>5.</strong>3.3 Kolo za sabiranje i oduzimanje<br />

Jedina razlika između sabiranja i oduzimanja je u tome što je kod oduzimanja potrebno<br />

koristiti dvojični komplement jednog od operanada. Neka su X i Y dva broja, koja treba<br />

sabrati ili oduzeti i neka je Y broj koji prilikom oduzimanja služi kao umanjilac, tj. neka je<br />

S=X±Y. Kao što znamo, dvojični komplement operanda Y se može dobiti dodavanjem<br />

jedinice na njegov jedinični komplement. Dodavanje jedinice na poziciju najmanje težine<br />

može se postići postavljanjem bita ulaznog prenosa c0 na 1. Jedinični komplement datog<br />

broja se dobija komplementiranjem svih njegovih bitova. Komplementiranje broja se može<br />

obaviti pomoću NOT gejtova. Međutim, za ovu namenu biće nam potrebno fleksibilnije kolo,<br />

kako bi smo mogli da u zavisnosti od željene operacije koristimo pravu ili komplementiranu<br />

vrednost operanda Y. Takvo kolo je XOR gejt. Interesantna osobina XOR gejta je da jedan od<br />

njegovih ulaza možemo koristiti kao upravljačku promenljivu pomoću koje ćemo birati da li<br />

će se na izlazu <strong>kola</strong> generisati prava ili komplementarna vrednost drugog ulaza. Ovo je jasno<br />

na osnovu definicije XOR operacije:<br />

z=x ⊗ y = x’y + xy’<br />

18

Neka je x upravljački ulaz. Za x=0, izlaz će biti identičan ulazu y, tj. z= 0’·y + 0·y’=1·y+0·<br />

y’= y. Ali, ako je x=1, izlaz će biti jednak komplementu ulaza y, tj. z= 1’·y + 1·y’=0·y+1· y’=<br />

y’. Drugim rečima, za x=1 XOR gejt funkcioniše kao invertor, dok za x=0, jednostavno<br />

prenosi vrednost sa ulaza y na izlaz.<br />

Kolo za sabiranje/oduzimanje možemo konstruisati na sledeći način. Pretposatavimo da<br />

postoji upravljački signal koji određuje da li treba obaviti sabiranje ili oduzimanje. Neka se<br />

ovaj signal zove Add / Sub (prema engleskim nazivima za sabiranje i oduzimanje: addition i<br />

subtraction). Takođe, neka vrednost 0 ovog signala bira sabiranje, a 1 oduzimanje. Crta iznad<br />

Add upravo ukazuje na ovu činjenicu. Napomenimo da je ovo često korišćena konvencija, tj.<br />

da crta iznad imena upravljačkog signala ukazuje da se akcija specificirana tim imenom<br />

obavlja kada signal ima vrednost 0. Neka je svaki bit operanda Y povezan na jedan ulaz<br />

jednog od XOR gejtova, a da su drugi ulazi svih XOR gejtova povezani na signal Add / Sub .<br />

Izlazi XOR gejtova predstavljaju Y, ako je Add / Sub=0,<br />

odnosno Y’, ako je Add / Sub =1. Tako<br />

dolazimo do <strong>kola</strong> sa Sl. 5-1<strong>5.</strong> Glavni deo ovog <strong>kola</strong> je n-to bitni sabirač, koji može biti<br />

realizovan korišćenjem strukture sabirača sa rednim prenosom sa Sl. 5-6(a). Uočimo da je<br />

upravljački ulaz Add / Sub povezan i na ulaz c0 sabirača. Na ovaj način, biće c0=1 kada se<br />

obavlja oduzimanje, što dodaje jedinicu koja je neophodna da bi se formirao dvojični<br />

komplement operanda Y. Kada se obavlja operacija sabiranja, c0 će biti 0 i neće uticati na<br />

rezultat.<br />

Sl. 5-15 Sabirač/oduzimač.<br />

Kombinovano kolo za sabiranje i oduzimanje je dobar primer jednog važnog koncepta<br />

koji se primenjuje u projektovanju digitalnih sistema. Korisno je projektovati <strong>kola</strong> koja će biti<br />

što je moguće više fleksibilna i na taj način iskoristiti zajedničke delove <strong>kola</strong> za što više<br />

različitih zadataka. Ovakvim pristupom minimizuje se broj gejtova potrebnih za realizaciju<br />

sistema. Takođe, značajno se samanjuje složenost povezivanja komponenti sistema.<br />

<strong>5.</strong>3.4 Aritmetičko prekoračenje<br />

Ako operacija sabiranja ili oduzimanja generiše rezultat koji premašuje opseg brojnog<br />

sistema kažemo da je došlo do aritmetičkog prekoračenja. Drugim rečima, aritmetičko<br />

prekoračenje se javlja u situacijama kada je rezultat pozitivan i suviše veliki ili negativan i<br />

suviše mali tako da ga nije moguće predstaviti raspoloživim značajnim bitovima. Ako za<br />

predstavljanje označenih <strong>brojeva</strong> koristimo n bita, tada rezultat mora biti u opsegu od -2 n-1 do<br />

(2 n-1 -1). Kada su sabirci različitog znaka, do aritmetičkog prekoračenja nikada neće doći, zato<br />

što će rezultat uvek biti manji od pozitivnog i veći od negativnog sabirka. Međutim, ako su<br />

sabirci istog znaka, može se desiti da rezultat bude veći od 2 n-1 -1, ako su oba sabirka<br />

19

pozitivna, odnosno, manji od -2 n-1 , ako su sabirci negativni. Da bi se osigurao ispravan rad<br />

aritmetičkog <strong>kola</strong>, neophodno je biti u mogućnosti detektovati pojavu aritmetičkog<br />

prekoračenja.<br />

Sl. 5-16 Primeri za određivanje uslova prekoračenja.<br />

Na Sl. 5-16 su prikazana četiri slučaja sabiranja <strong>brojeva</strong> u dvojičnom komplementu čije<br />

su magnitude 7 i 2. S obzirom da u ovom primeru za predstavljanje <strong>brojeva</strong> koristimo 4 bita,<br />

broj značajnih bitova je tri, b0-2. Kao što se vidi sa Sl. 5-16, kada su sabirci različitog znaka<br />

rezultat je tačan, tj. nema prekoračenja. Međutim, ako oba broja imaju isti znak, magnituda<br />

rezultata je 9 i ne može biti predstavljena sa samo tri značajna bita, tj. dolazi do prekoračenja.<br />

Ključ za detekciju pojave prekoračenja su dva prenosa: c3 – izlazni prenos iz pozicije najveće<br />

težine i c4 izlazni prenos iz pozicije znaka. Na osnovu primera sa Sl. 5-16, može se zaključiti<br />

da se prekoračenje javlja kada ova dva bita imaju različite vrednosti, a da je rezultat ispravan<br />

ako su njihove vrednosti iste. Izražen u obliku logičkog izraza, uslov prekoračenja glasi:<br />

Prekoračenje = c3c4’ + c3’c4<br />

= c3 ⊗ c4<br />

Ili, u opštem slučaju, za n bitne brojeve, imamo:<br />

Prekoračenje = cn-1 ⊗ cn<br />

Na Sl. 5-17a je prikazana struktura sabirača/oduzimača sa kolom za detekciju<br />

prekoračenja koje ispituje izlazne prenose.<br />

Drugi način za detekciju aritmetičkog prekoračenja upoređuje bitove znaka sabiraka i<br />

rezultata. Neka su X=xn-1xn-2…x0 i Y=yn-1yn-2…y0 binarni brojevi u dvojičnom komplementu, i<br />

S=sn-1sn-2…s0 rezultat njihovog sabiranja. Bitovi xn-1, yn-1 i sn-1 su bitovi znaka ova tri broja.<br />

Aritmetičko prekoračenje postoji ako smo sabiranjem pozitivnih <strong>brojeva</strong> dobili negativan<br />

rezultat ili ako smo sabiranjem negativnih <strong>brojeva</strong> dobili pozitivan rezultat, tj.:<br />

Prekoračenje = xn-1yn-1sn-1’ + xn-1’yn-1’sn-1<br />

Isto tvrđenje, kazano drugim rečima, glasi: do prekoračenja je došlo ako se rezultat<br />

razlikuje po znaku od oba sabirka, tj.:<br />

Prekoračenje = (xn-1 ⊗ sn-1) (yn-1 ⊗ sn-1)<br />

Kolo sabirača/oduzimača kod koga je detekcija prekoračenja realizovana shodno gornjem<br />

izrazu prikazano je na slici. Uočimo da je prvi način za detekciju prekoračenja, Sl. 5-17a,<br />

jednostavniji, jer zahteva sam još jedno dodatno XOR kolo, za razliku od drugog kod koga je<br />

potrebno ugraditi dodatna tri gejta. Međutim, prvo rešenje podrazumeva da je signal izlaznog<br />

prenosa cn-1 dostupan, što ne mora biti slučaj ako rasplažemo sabiračem koji se realizovan<br />

20

kao monolitna komponenta. U tom smislu, drugo rešenja je pogodnije jer koristi samo<br />

spoljašnje signale sabirača/oduzimača.<br />

(a) detekcija prekoračenja na osnovu izlaznih prenosa<br />

(b) detekcija prekoračenja na osnovu znaka sabiraka i rezultata.<br />

Sl. 5-17 Dva načina za detekciju aritmetičkog prekoračenja.<br />

Napomenimo da su dva pravila za detekciju aritmetičkog prekoračenja, u suštini,<br />

ekvivalentna. Potpuni sabirač na poziciji bita znaka obavlja sledeće izračunavanje: (cn, sn-1) =<br />

(xn-1 + yn-1 + cn-1). Ako su oba sabirka pozivitna, xn-1=yn-1=0, izlazni prenos iz pozicije znaka<br />

biće cn=0, bez obzira na vrednost cn-1. Za cn-1=0, bit znaka rezultata biće sn-1=0, što ukazuje<br />

da je rezultat pozitivan i da zbog toga prekoračenja nema. Međutim, ako je cn-1=1, bit znaka<br />

dobija vrednost sn-1=1, što ukazuje na negativan rezultat, tj. na pojavu prekoračenja. Slično,<br />

ako su oba sabirka negativna, xn-1=yn-1=1, izlazni prenos iz pozicije znaka biće cn=1, bez<br />

obzira na vrednost cn-1. Međutim, za cn-1=0, bit znaka dobija vrednost sn-1=0, što ukazuje na<br />

pozitivan rezultat, odnosno na prekoračenje. Dakle, u oba slučaja važi da prekoračenje postoji<br />

ako je cn≠cn-1.<br />

<strong>5.</strong>3.5 Performanse<br />

Prilikom kupovine digitalnog sistema, kao što je računar, kupac naročitu pažnju obraća na<br />

performanse koje se mogu očekivati od sistema, kao i na cenu sistema. Superiorne<br />

performanse obično znače i višu cenu. Međutim, ne tako retko, dešava se da se sistem sa<br />

21

značajno boljim performansama može kupiti po umereno višoj ceni. Takođe, dešava se i da<br />

za sistem sa tek nešto boljim performansama moramo platiti mnogo više. Zato se kao<br />

indikacija vrednosti sistema često koristi odnos cena/performanse.<br />

Sabiranje i oduzimanje <strong>brojeva</strong> su bazične operacije koje se često obavljaju u računarskim<br />

sistemima. Brzina izvršenja ovih operacija ima veliki uticaj na ukupne performanse računara.<br />

Iz tog razloga, razmotrimo brzinu rada <strong>kola</strong> za sabiranje i oduzimanje. Brzina rada ovog <strong>kola</strong><br />

određena je kašnjenjem od trenutka kada se na ulaze <strong>kola</strong> postave operandi X i Y do trenutka<br />

kada se na izlazu <strong>kola</strong> generišu korektne vrednosti svih bitova sume S i izlaznog prenosa cn.<br />

Najveći deo ovog kašnjenja potiče od n-bitnog sabirača. Pretpostavimo da je sabirač<br />

realizovan korišćenjem strukture sa rednim prenosom (Sl. 5-6), kod koje su potpuni sabirači<br />

realizovani kao na Sl. 5-4. Kao što se lako može zaključiti sa Sl. 5-4, kod ove realizacije<br />

potpunog sabirača, kašnjenje izlaznog prenosa, ∆t, jednako je kašnjenju kroz dva gejta, tj.<br />

∆t=2tg, gde je tg kašnjenje kroz jedan gejt. Iz odeljka <strong>5.</strong>2.1 znamo da ukupno kašnjenje<br />

sabirača sa rednim prenosom iznosi n∆t, što je ekvivalentno kašnjenju kroz 2n gejta. Pored<br />

kašnjenja koje je posledica prostiranja signala prenosa kroz sabirač, na ukupno kašnjenje <strong>kola</strong><br />

za sabiranje i oduzimanje dodatno utiču i ulazna XOR <strong>kola</strong>. Ako pretpostavimo da je<br />

kašnjenje kroz XOR kolo jednako tg, dolazimo do zaključka da kolo za sabiranje i<br />

oduzimanje unosi kašnjenje ekvivalentno kašnjenju kroz 2n+1 gejt. Za veće n, npr. n=32 ili<br />

n=64, iznos kašnjenja može biti toliko veliki da značajno degradira performanse celog<br />

sistema. Zato je bitno ispitati mogućnost alternativne realizacije binarnog sabirača, koja će se<br />

odlikovati većom brzinom rada.<br />

Brzina rada bilo kog digitalnog <strong>kola</strong> ograničena je najvećim kašnjenje duž neke od<br />

putanja kroz kolo. U slučaju <strong>kola</strong> sa Sl. 5-15, najduže kašnjenje se javlja duž putanje koja<br />

kreće od ulaza yi, prolazi kroz XOR gejt, a zatim kroz <strong>kola</strong> za generisanje prenosa svih<br />

potpunih sabirača. Najduže kašnjenje se zove kašnjenje kritičnog puta, a putanja koja<br />

uslovljava ovo kašnjenje kritična putanja.<br />

<strong>5.</strong>4 Brzi sabirači<br />

Kašnjenje uzrokovano propagacijom signala prenosa kroz sabirač sa rednim prenosom<br />

može se smanjiti ako promenimo strukturu sabirača na način da svaki stepen i, umesto da<br />

čeka da od stepena i-1 dobije ulazni prenos ci, pre nego što generiše svoj bit sume si,<br />

samostalno pokuša da odredi da li će vrednost ulaznog prenosa biti 0 ili 1. Da bi ukupne<br />

performanse sabirača bile poboljšanje, potrebo je da korektna procena vrednosti ulaznog<br />

prenosa bude obavljena za što je moguće kraće vreme.<br />

Pođimo od izraza za funkciju izlaznog prenosa i-tog stepena sabirača:<br />

ci+1 = xiyi + xici + yici<br />

Ako ovaj izraz rastavimo na sledeći način:<br />

ci+1 = xiyi + (xi + yi)ci<br />

funkciju ci+1 možemo napisati u obliku:<br />

gde je:<br />

ci+1 = gi + pici (<strong>5.</strong>3)<br />

gi = xiyi<br />

pi = xi + yi<br />

Jednačinu (<strong>5.</strong>3) možemo protumačiti na sledeći način. Kada je gi=1, tj. xi=yi=1, stepen i<br />

generiše izlazni prenos, ci+1=1, bez obzira na vrednost ulaznog prenosa ci. Zato se g zove<br />

22

funkcija generisanog prenosa. Funkcija pi jednaka je 1 ako je barem jedan od ulaza xi i yi<br />

jednak 1. U ovom slučaju, ci=1 uslovljava generisanje izlaznog prenosa ci+1, tj. efekat je kao<br />

da se ulazni prenos preneo na izlaz. Zbog toga se funkcija p zove funkcija propagiranog<br />

prenosa. Dakle, stepen i generiše prenos ako su oba njegova sabirka jednaka 1, a propagira<br />

prenos ako je jedan od sabiraka jednak 1.<br />

Jednačina (<strong>5.</strong>3) nam omogućava da rekurzivnom zamenom člana ci eliminišemo<br />

propagaciju prenosa kroz sabirač. Naime, kao što je ci+1 = gi + pici, tako je i ci = gi-1 + pi-1ci-1.<br />

Dakle,<br />

ci+1 = gi + pi(gi-1 + pi-1ci-1)<br />

= gi + pigi-1 + pipi-1ci-1<br />

Nastavljajući sa smenama, sve do c0, dolazimo do izraza za ci+1 sledećeg oblika:<br />

ci+1 = gi + pigi-1 + pipi-1gi-2 + ... + pipi-1... p2p1g0 + pipi-1...p1p0c0 (<strong>5.</strong>4)<br />

Dobijeni izraz se može realizovati u vidu tronivovske AND-OR mreže. U prvom nivou<br />

računaju se funkcije generisanog i propagiranog prenosa, gi i pi. U drugom nivou,<br />

izračunavaju se produktni članovi, koji se, potom, sumiraju u trećem nivou. S obzirom na<br />

mali broj nivoa, ci+1 se izračunava veoma brzo. Šta više, kašnjenje u izračunavanju izlaznih<br />

prenosa ci+1 je fiksno i ne zavisi od i, što znači da ni ukupno kašnjenje sabirača ne zavisi od<br />

obima operanada, tj. n. Binarni sabirač zasnovan na izrazu (<strong>5.</strong>4) zove se sabirač sa ubrzanim<br />

prenosom ili CLA sabirač, prema engleskom nazivu Carry-Lookahead Adder.<br />

Da bi smo bolje razumeli fizičko značenje izraza (<strong>5.</strong>4) uporedićemo konstrukcije sabirača<br />

sa ubrzanim i sabirača sa rednim prenosom. U tom cilju, analizaćemo detaljnu strukturu dva<br />

stepena najmanje težine oba sabirača.<br />

Sl. 5-18 prikazuje prva dva stepena sabirača sa rednim prenosom kod koga su funkcije<br />

izlaznog prenosa realizovane shodno izrazu (<strong>5.</strong>3). Mala brzina rada sabirača sa rednim<br />

prenosom posledica je dugačke putanje duž koje se prostire signal prenosa. Kao što je<br />

posebno naznačeno na Sl. 5-18, kritični put polazi od ulaza x0 i y0 i proteže se do izlaza c2,<br />

prolazeći kroz 5 gejta, 3 gejta u stepenu 0 i 2 u stepenu 1. Za sabirač sa n stepena, kritični put<br />

se nastavlja dalje sve do izlaza cn, prolazeći kroz svaki sledeći stepen na isti način kao kroz<br />

stepen 1. Dakle, kašnjenje kritičnog puta sabirača sa rednim prenosom iznosi 2n+1.<br />

23

Sl. 5-18 Detaljna struktura sabirača sa rednim prenosom.<br />

Na Sl. 5-19 je prikazana detaljna struktura prva dva stepena sabirača sa ubrzanim<br />

prenosom. Sada su funkcije izlaznog prenosa realizovane shodno izrazu (<strong>5.</strong>4), tj.:<br />

c1 = g0 + p0c0<br />

c2 = g1 + p1g0 + p1p0c0<br />

Kao što se može uočiti sa Sl. 5-19, u svakom stepenu sabirača sa rednim prenosom<br />

generišu se funkcije generisanog i propagiranog prenosa. Lokalno, ove funkcije se koriste,<br />

zajedno sa funkcijama g i p svih prethodnih stepena, za generisanje izlaznog prenosa tog<br />

stepene, ali i prosleđuju dalje ka svim narednim stepenima gde se koriste za određivanje<br />

njihovih izlaznih prenosa. Kritični put za određivanje izlaznog prenosa c2 naznačen je na Sl.<br />

5-19. U ovom kolu, c2 se određuje jednako brzo kao i c1, tj. nakon vremena koje je jednako<br />

kašnjenju kroz tri gejta, tj. 3tg. Čak iako ovu strukturu proširimo na n bita, konačni izlazni<br />

prenos cn generisaće se sa kašnjenjem od 3tg. Naravno, što je i veće, tj. kako se krećemo ka<br />

pozicijama veće težine, to izrazi za funkcije ci+1 postaju sve složeniji, što zahteva sve veći<br />

broj gejetova za njihovu realizaciju. Međutim, bez obzira na složenost, broj nivoa logike za<br />

izračunavanje ci+1 ostaje isti, tj. tri.<br />

Ukupno kašnjenje n-to bitnog sabirača sa ubrzanim prenosom isnosi 4tg. Vrednosti svih<br />

funkcija gi i pi određuju se nakon vremena tg. Dodatno kašnjenje od 2tg potrebno je za<br />

određivanje svih signala prenosa. Konačno, treba sačekati još dodatno vreme tg da bi se na<br />

izlazima svih XOR <strong>kola</strong> generisali bitovi sume.<br />

24

Sl. 5-19 Prva dva stepena sabirača sa ubrzanim prenosom.<br />

Izraz (<strong>5.</strong>4) se može realizovati pomoću brze, tri-nivolske AND-OR mreže. Međutim, za<br />

veliko i broj ulaza u pojedine gejtove, koji su potrebni za realizaciju ove funkcije, postaje<br />

isuviše veliki. Kao što je poznato iz poglavlja X, kod većine implementacionih tehnologija<br />

broj ulaza u gejtove, tj. fan-in faktor, ograničen je na relativno mali broj. Zato je neophodno<br />

prilikom projektovanja sabirača sa ubrzanim prenosom uzeti u obzir i ovu činjenicu. Da bi<br />

smo bliže ukazali na ovaj problem, razmotrimo izraze za prvih osam izlaznih prenosa:<br />

c1 = g0 + p0c0<br />

c2 = g1 + p1g0 + p1p0c0<br />

...<br />

c8 = g7 + p7g6 + p7p6g5 + p7p6p5g4 + p7p6p5p4g3 + p7p6p5p4p3g2 + p7p6p5p4p3p2g1<br />

+ p7p6p5p4p3p2p1g0 + p7p6p5p4p3p2p1p0c0<br />

Pretpostavimo da je fan-in raspoloživih gejtova ograničen na četiri ulaza. Očigledno,<br />

pomoću takvih gejtova nije moguće realizovati sve prethodne izraze u obliku tri-nivolske<br />

AND-OR mreže. Nejveći problem je c8, gde se čak zahteva jedno AND kolo sa 9 ulaza.<br />

Takođi, i za sumiranje produktnih članova potrebno je OR kolo sa 9 ulaza. Potreba za<br />

logičkim kolima sa velikim brojem ulaza potiče od produktnih i zbirnih članova sa velikim<br />

brojem literala. Međutim, pravilnom faktorizacijom, moguće je smanjiti maksimalnu veličinu<br />

članova u logičkom izrazu. Jedno moguće rešenje je sledeće:<br />

c8 = (g7 + p7g6 + p7p6g5 + p7p6p5g4)+ [(p7p6p5p4)(g3 + p3g2 + p3p2g1 +p3p2p1g0)]<br />

+ (p7p6p5p4)(p3p2p1p0)c0<br />

Za realizaciju ovog izraza potrebna su 11 AND i tri OR gejta. Međutim, sada<br />

propagaciono kašnjenje iznosi ne više 3tg već 5tg: jedno tg za određivanje gi i pi; 2tg za<br />

sumiranje produktnih članova u zagradama; jedno tg za produktni član u velikim zagradama i<br />

još jedno tg za konačno sumiranje. Dakle, ograničenje u pogledu maksimalnog broja ulaza u<br />

gejtove manifestuje se u povećanju broja nivoa AND-OR mreže, što neminovno povećava<br />

25

propagaciono kašnjenje. Ovaj zaključak nije ograničen samo na konkretno kolo, već veži<br />

generalno za bilo koju logičku mrežu.<br />

<strong>5.</strong>4.1 Hijerarhijski sabirač sa ubrzanim prenosom<br />

Projektovanje digitalnih sistema po pravilu zahteva nalaženje optimalnog kompromisa<br />

između brzine rada sistema i njegove cene. Težnja da se što više poveća brzina rada, obično<br />

ima za posledicu povećanje cene sistema. Isto tako, složenost sistema obično nije moguće<br />

smanjiti, a da to nema za posledicu smanjenje brzine rada. U kontekstu binarnog sabirača,<br />

struktura sa rednim prenosom predstavlja najjednostavnije, ali u isto vreme i najsporije<br />

rešenje. Sa druge strane, sabirač sa ubrzanim prenosom predstavlja najbrže rešenje, ali zato za<br />

neke primene, njegova složenost (cena) može biti isuviše velika. Međutim, mogu postojati<br />

primene kada ni jedna od ove dve varijante sabirača ne zadovoljava postavljene zahteve –<br />

sabirač sa rednim prenosom može biti previše spor, a sabirač sa ubrzanim prenosom previše<br />

složen. Zato je bitno raspolagati nekom fleksibilnom sabiračkom strukturom koja će<br />

omogućiti lako nalaženje kompromisa između složenosti i brzine rada. Jedna takva struktura<br />

je hijerarhijski sabirač sa ubrzanim prenosom.<br />

Pretpostavimo da želimo da projektujemo 32-sabirač. Sabirač možemo podeliti na četiri<br />

8-bitna bloka, tako da bitovi b0-7 pripadaju bloku 0, bitovi b8-15 pripadaju bloku 1, bitovi b16-23<br />

bloku 2 i bitovi b24-32 bloku 3. Svaki blok možemo realizovati kao 8-bitni sabirač sa ubrzanim<br />

prenosom. Signali izlaznog prenosa iz ovih blokova su c8, c16, c24 i c32. Postoje dva načina<br />

kako 8-bitne blokove možemo povezati u jedinstveni 32-bitni sabirač. Jedno rešenje je da<br />

blokove povežemo na isti način kao što bi smo povezali četiri stepena sabirača sa rednim<br />

prenosom (Sl. 5-20). Znači, kod ovog rešenja unutar blokova koristimo tehniku ubrzanog<br />

prenosa, dok se između blokva prenos prenosi redno.<br />

Sl. 5-20 Hijerarhijski CLA sabirač sa rednim prenosom između blokova.<br />

Brže kolo se može realizovati ako se i za generisanje prenosa između blokova, umesto<br />

rednog prenosa, koristi tehnika ubrzanog prenosa. Na Sl. 5-21 je prikazana struktura<br />

hijerarhijskog sabirača sa ubrzanim prenosom kod koga je iskorišćena ova tehnika. Svaki<br />

blok na gornjem delu Sl. 5-21 predstavlja jedan 8-bitni sabirač sa ubrzanim prenosom. Unutar<br />

bloka, u svakom njegovom unutrašnjem stepenu generišu se signali generisanog i<br />

propagiranog prenosa, gi i pi, na prethodno opisan način. Međutim, umesto da svaki blok<br />

generiše signal izlaznog prenosa iz svoje pozicije naveće težine, kao u rešenju sa Sl. 5-20,<br />

sada svaki blok generiše signale generisanog i propagiranog prenosa za celokupan blok. Neka<br />

su ovi signali označeni sa Gj i Pj. Signali Gj i Pj se koriste kao ulazi u <strong>kola</strong> za ubrzanje<br />

prenosa drugog nivoa, prikazana u doljem delu Sl. 5-21, koja određuju prenose između<br />

blokova. Izraze za funkcije Gj i Pj možemo odrediti na osnovu poznatog izraza za c8:<br />

c8 = g7 + p7g6 + p7p6g5 + p7p6p5g4 + p7p6p5p4g3 + p7p6p5p4p3g2 + p7p6p5p4p3p2g1<br />

+ p7p6p5p4p3p2p1g0 + p7p6p5p4p3p2p1p0c0<br />

26

Poslednji član u ovom izrazu kazuje da ako su sve interne funkcije propagiranog prenosa, pi,<br />

i=1,..,7, jednake 1, tada se signal ulaznog prenosa, c0, prenosi kroz celokupan blok. Dakle,<br />

P0 = p7p6p5p4p3p2p1p0<br />

Preostali članovi u izrazu za c8 ukazuju na sve ostale slučajeve kada blok generiše izlazni<br />

prenos. Dakle,<br />

G0 = g7 + p7g6 + p7p6g5 + ... + p7p6p5p4p3p2g1 + p7p6p5p4p3p2p1g0<br />

Konačno, izraz za c8 hijerarhijskog sabirača oblika je:<br />

c8 = G0 + P0c0<br />

Za blok 1, izrazi za G1 i P1 imaju istu formu, osim što indeks i treba zameniti indeksom<br />

i+8. Izrazi za G2, P2, G3 i P3, određuju se na isti način. Ako znamo funkcije generisanog i<br />

propagiranog prenosa na nivou blokova, tada možemo odrediti i izraze za ulazne prenose u<br />

svaki pojedinačni blok:<br />

c16 = G1 + P1c8<br />

= G1 + P1G0 +P1P0 c0<br />

Slično, izrazi za c24 i c32 su oblika:<br />

c24 = G2 + P2G1 +P2P1G0 + P2P1P0c0<br />

c32 = G3 + P3G2 +P3P2G1 + P3P2P1G0 + P3P2P1P0c0<br />

Izračunavanje signala prenosa c8, c16, c24 i c32 na osnovu poznatih vrednosti Gj i Pj unosi<br />

dva dodatna nivoa logike. Znači, pod pretpostavkom da je fan-in ograničen na 4 ulaza, vreme<br />

potrebno da se obavi sabiranje dva 32-bitna broja iznosi: 5tg za određivanje Gj i Pj (na osnovu<br />

prethodno sprovedene analize za c8), plus 3tg za ubrzanje prenosa na drugom nivou (zato što<br />

dva gejta u izrazu za c32 zahtevaju 5 ulaza i zbog toga moraju biti faktorizovani), plus jedno tg<br />

(XOR) za određivanje bitova sume, što u zbiru daje 9tg. Tačnije, konačna suma se generiše<br />

posle 8tg zato što c32 ne utiče na bitove sume. Međutim, c32 se koristi za detekciju<br />

aritmetičkog prekoračenja (Prekoračenje = c32 ⊗ c31). Dakle, trajanje operacije sabiranja,<br />

uključujući detekciju prekoračenja, ekvivalentno je kašnjenju kroz 9 gejtova.<br />

27

Sl. 5-21 Hijerarhijski sabirač sa ubrzanim prenosom.<br />

U odeljku X, utvrđeno je da sabiranje dva n-to bitna broja pomoću sabirača sa rednim<br />

prenosom traje (2n+1)tg, što za n=32 iznosi 65tg. Očigledno, isti zadatak sabirač sa ubrzanim<br />

prenosom obavi za oko 7 puta brže. Ovo značajno poboljšanje performansi ostvareno je na<br />

račun značajno veće složenosti sabirača sa ubrzanim prenosom.<br />

<strong>5.</strong>5 Projektovanje aritmetičkih <strong>kola</strong> korišćenjem šematskog editora<br />

Očigledan način za projektovanje aritmetičkih <strong>kola</strong> pomoću šematskog editora je crtanje<br />

logičke šeme koja će sadržati sva neophodna logička <strong>kola</strong>. Na primer, da bi smo kreirali nbitni<br />

sabirač sa rednim prenosom, treba najpre nacrtati logičku šemu potpunog sabirača.<br />

Zatim, treba kreirati logičku šemu višeg hijerarhijskog nivoa i u njoj povezati n instanci<br />

potpunog sabirača. Hijerarhijska logička šema kreirana na ovaj način trebalo bi liči na kolo sa<br />

Sl. 5-6a. Koristeći istu metodologiju možemo projektovati i kolo za sabiranje i oduzimanje sa<br />

Sl. 5-1<strong>5.</strong><br />

Glavni problem ovakvog načina unosa dizajna je u tome što može biti dugotrajan i<br />

naporan, naročito ako je broj bitova veliki. Ovaj problem bi postao još izraženiji i evidentniji<br />

ako bi smo pomoću šematskog editora pokušali da nacrtamo logičku šemu sabirača sa<br />

ubrzanim prenosom. Kao što je poznato iz odeljka <strong>5.</strong>4, sabirač sa ubrzanim prenosom ne<br />

poseduje homogenu strukturu, već se svaki njegov stepen, u delu logike za generisanje<br />

prenosa, razlikuje od ostalih. Iz tog razoga bilo bi neophodno nacrtati posebnu logičku šemu<br />

za svaki stepen sabirača. Šta više, u svakom sledećem stepenu, logika za generisanje prenosa<br />

postaje sve složenija, i zahteva sve već broj gejtova, tako da bi logičke šeme brzo postale<br />

glomazne i nepregledne. Daleko bolji način za kreiranje aritmetičkih <strong>kola</strong> pomoću šematskog<br />

editora je onaj koji se oslanja na korišćenje unapred projektovanih struktura.<br />

Kao što je naglešeno u odeljku X, sastavni deo alata za šematski unos dizajna je<br />

biblioteka grafičkih simbola osnovnih logičkih gejtova. Ovi gejtovi se koriste za kreiranje<br />

relativno jednostavnih <strong>kola</strong>. Pored biblioteke osnovnih gejtova, alati za šematski unos dizajna<br />

tipično poseduju i biblioteku često korišćenih, složenijih struktura, ako što su sabirači ili<br />

28

ALU jedinice. Svako takvo kolo može biti uvršćeno u logičku šemu i korišćeno kao deo<br />

većeg <strong>kola</strong>. Kod CAD sistema, za module ovog tipa koristi se pojam makroćelija ili<br />

megafunkcija.<br />

Postoje dva glavna tipa makroćelija: tehnološki-zavisne i tehnološki-nezavisne.<br />

Tehnološki-zavisna makroćelija je prilagođena konkretnoj implementacionoj tehnologiji. Na<br />

primer, u odeljku <strong>5.</strong>4 je razmatrana konstrukcija sabirača sa ubrzanim prenosom pod<br />