Logikbausteine Aufgabensammlung

Logikbausteine Aufgabensammlung

Logikbausteine Aufgabensammlung

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

1. Aufgabe<br />

Die parasitäre Kapazität des Einganges eines Digitalbausteines betrage Ci=5pF. Der Eingang<br />

wird über einen Treiber mit Ausgangswiderstand RD=200Ω angesteuert. Die<br />

Versorgungsspannung der gesamten Logikschaltung betrage VDD=+3,3V, die (idealisierten)<br />

Logikpegel sind deshalb 0V (Low) bzw. +3,3V (High).<br />

2. Aufgabe<br />

a) Welche Anstiegszeit (rise time) weist die Spannung am Eingang des<br />

Digitalbausteines auf? Wie hängt die Anstiegszeit von den Logikpegeln ab?<br />

b) Welche Abfallzeit (fall time) weist die Spannung am Eingang des<br />

Digitalbausteines auf? Wie hängt die Abfallzeit von den Logikpegeln ab?<br />

c) Der Digitalbaustein erkennt einen High-Pegel am Eingang, wenn die<br />

Eingangsspannung mindestens 70% des vollen High-Pegels von +3,3V beträgt.<br />

Wie lange dauert es deshalb nach Umschalten des Eingangspegels von Low auf<br />

High, bis der Digitalbaustein den High-Pegel auch als solchen erkennt?<br />

d) Der Digitalbaustein erkennt einen Low-Pegel am Eingang, wenn die<br />

Eingangsspannung maximal 30% des vollen High-Pegels von +3,3V beträgt. Wie<br />

lange dauert es deshalb nach Umschalten des Eingangspegels von High auf Low,<br />

bis der Digitalbaustein den Low-Pegel auch als solchen erkennt?<br />

e) Beschreiben Sie, inwiefern das obige analysierte Verhalten eine Auswirkung auf<br />

die maximale Taktfrequenz hat.<br />

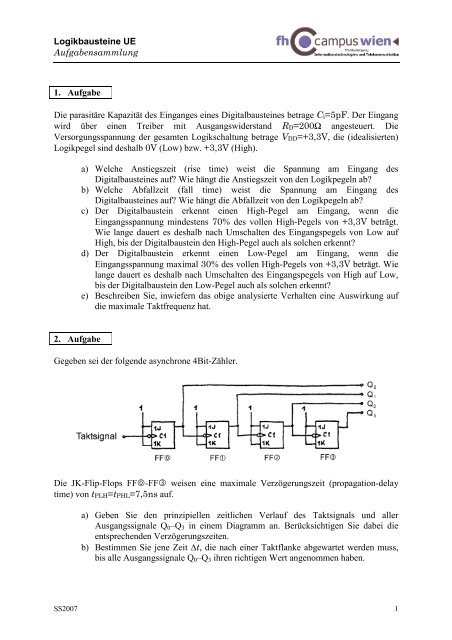

Gegeben sei der folgende asynchrone 4Bit-Zähler.<br />

Die JK-Flip-Flops FF-FF weisen eine maximale Verzögerungszeit (propagation-delay<br />

time) von tPLH=tPHL=7,5ns auf.<br />

a) Geben Sie den prinzipiellen zeitlichen Verlauf des Taktsignals und aller<br />

Ausgangssignale Q0–Q3 in einem Diagramm an. Berücksichtigen Sie dabei die<br />

entsprechenden Verzögerungszeiten.<br />

b) Bestimmen Sie jene Zeit ∆t, die nach einer Taktflanke abgewartet werden muss,<br />

bis alle Ausgangssignale Q0–Q3 ihren richtigen Wert angenommen haben.<br />

SS2007 1

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

3. Aufgabe<br />

c) Die Ausgangssignale Q0–Q3 sollen in einer anschließenden Schaltung mit der<br />

jeweils nächsten negativen Flanke desselben Taktsignals in Register mit einer<br />

Vorbereitungszeit (setup time) tsu=2,5ns geladen werden. Bestimmen Sie die<br />

dafür maximal zulässige Taktfrequenz fmax.<br />

Gegeben sei der folgende synchrone 4Bit-Zähler.<br />

Die JK-Flip-Flops FF-FF weisen eine maximale Verzögerungszeit (propagation-delay<br />

time) von tPLH=tPHL=7,5ns sowie eine Vorbereitungszeit (setup time) von tsu=2,5ns auf, für<br />

die &-Gatter G-G gelte tPLH=tPHL=4,1ns als maximale Verzögerungszeit.<br />

4. Aufgabe<br />

a) Geben Sie den prinzipiellen zeitlichen Verlauf des Taktsignals und aller<br />

Ausgangssignale Q0–Q3 in einem Diagramm an. Berücksichtigen Sie dabei die<br />

entsprechenden Verzögerungszeiten.<br />

b) Bestimmen Sie jene Zeit ∆t, die nach einer Taktflanke abgewartet werden muss,<br />

bis alle Ausgangssignale Q0–Q3 ihren richtigen Wert angenommen haben.<br />

c) Bestimmen Sie die maximal zulässige Taktfrequenz fmax, so dass noch alle<br />

zeitlichen Bedingungen erfüllt werden und die Schaltung damit richtig<br />

funktioniert.<br />

Eine l=10m lange Leitung mit Wellenwiderstand ZW=100Ω wird von einem Digitalbaustein<br />

(Treiber) am Eingang angesteuert. Die Ausbreitungsgeschwindigkeit der Signale auf der<br />

Leitung sei v≈2⋅10 8 m/s. Der Digitalbaustein (Treiber) schalte einmalig vom Logikpegel 0V<br />

auf 5V und weist einen Innenwiderstand Ri=25Ω auf. Der Ausgang der Leitung ist an einen<br />

weiteren Logikbaustein angeschlossen, dessen Eingang sehr hochohmig ist.<br />

Geben Sie die Spannungsverläufe ue(t), ua(t) am Eingang und Ausgang der Leitung für<br />

folgende Schaltungen an und beschreiben Sie die zeitlichen Abläufe:<br />

SS2007 2

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

5. Aufgabe<br />

a) Abschluss des Leitungsendes mit RT=100Ω<br />

b) Erhöhung des Quellwiderstandes mit RT=75Ω<br />

In der untenstehenden Abbildung sind drei Digitalbausteine IC1-IC3 an eine Leitung mit<br />

einem Wellenwiderstand ZW=100Ω, die als Bus wirkt, angeschlossen. Die Leitung muss als<br />

lange betrachtet werden, d.h. sie erfordert die Berücksichtigung von allfälligen Reflexionen.<br />

IC1 IC2 IC3<br />

a) Überlegen Sie, was prinzipiell passiert, wenn jeweils einer der ICs (IC1, IC2 oder<br />

IC3) alleine ein Signal an die Leitung legt. Die jeweils anderen ICs sind passiv,<br />

legen also kein Signal an die Leitung an. Berücksichtigen Sie dabei, dass aus Sicht<br />

jedes ICs eigentlich zwei Leitungen an dessen Eingang/Ausgang angeschlossen<br />

sind, eine nach rechts und eine nach links laufende.<br />

Hinweis: Von keiner der beiden Leitungen ist zu Beginn bekannt, was am<br />

entsprechenden Ende tatsächlich angeschlossen ist.<br />

b) Welchen Widerstand sieht nach Punkt a) demnach jeder Ausgang im ersten<br />

Moment?<br />

c) Sind Reflexionen auf der Leitung/dem Bus zulässig oder verfälschen diese den<br />

Pegel? Falls Reflexionen vermieden werden müssen, wie kann man dies in obiger<br />

Schaltung erreichen?<br />

SS2007 3

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

6. Aufgabe<br />

d) Welchen Widerstand müssen die Eingänge der jeweils passiven (also der nicht<br />

sendenden) ICs aufweisen, damit keine irgendwie geartete Verfälschung der Pegel<br />

auftritt? Berücksichtigen Sie dabei, dass eine bei einem IC-Eingang eintreffende<br />

Welle den Eingangswiderstand und den „Widerstand“ des weiterlaufenden<br />

Leitungsstückes sieht (Wie sind diese zueinander geschaltet? Verfolgen Sie dazu<br />

den möglichen Stromfluss).<br />

Die folgenden Betrachtungen sollen anhand der untenstehenden Abbildung eines Standard-<br />

TTL-NAND-Gatters durchgeführt werden. Nehmen Sie für die leitende Diode UD=0,6V<br />

(Flussspannung) sowie für einen leitenden Transistor UBE=0,6V und UCE=0,2V an.<br />

7. Aufgabe<br />

a) Bestimmen Sie, wie ein nicht angeschlossener (offener) Eingang für die Schaltung<br />

wirkt. Wirkt dieser als Low, High oder als ein ungültiger Zustand am Eingang?<br />

b) Geben Sie an, welcher maximale Ausgangsstrom<br />

o bei Kurzschluss am Ausgang (z.B. ungeladener Kondensator im ersten<br />

Moment des Umschaltens des Ausgangs; Kondensatorspannung kann nicht<br />

springen!)<br />

o bei minimalem, gerade noch gültigen High-Pegel (Ua,Hmin=2,4V) am Ausgang<br />

o bei maximalem, gerade noch gültigen Low-Pegel (Ua,Lmax=0,4V) am Ausgang<br />

(gibt es in diesem Fall überhaupt eine Grenze?)<br />

fließen kann.<br />

In einer Digitalschaltung (TTL-Logikfamilie) mögen offene (z.B. ungenutzte) Eingänge in<br />

geeigneter Weise mit Versorgungsspannung (VCC=+5V±10%, High) bzw. Masse (0V, Low)<br />

verbunden sein. Siehe dazu untenstehende Schaltungen.<br />

SS2007 4

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

8. Aufgabe<br />

a) b)<br />

R PU<br />

V CC<br />

&<br />

SN74F30<br />

74F260<br />

a) Damit in einem ungünstigen Betriebsfall keine zu großen Ströme in die<br />

Gattereingänge fließen, werden diese nicht direkt sondern über einen Pull-Up-<br />

Widerstand RPU mit der Versorgungsspannung verbunden. Bestimmen Sie den<br />

Maximalwert RPU,max, so dass gerade noch ein richtiger High-Pegel Ue,Hmin (siehe<br />

Datenblatt) an den Eingängen auftritt. Berücksichtigen Sie dabei die jeweiligen<br />

Eingangsströme IIH (siehe Datenblatt des Bausteines) sowie den dabei<br />

ungünstigsten Wert der Versorgungsspannung.<br />

b) Mit einer Digitalschaltung soll das Drücken eines Tasters ausgewertet werden.<br />

Wird dieser betätigt, so liegen in obiger Schaltung die beiden mit dem Taster<br />

verbundenen Eingänge auf logisch High. Damit auch im nicht betätigten Zustand<br />

ein gültiger Pegel am Eingang anliegt, der sich vom Fall des gedrückten Tasters<br />

unterscheidet, wird ein Pull-Down-Widerstand RPD verwendet. Bestimmen Sie<br />

den Maximalwert RPD,max, so dass gerade noch ein richtiger Low-Pegel Ue,Lmax<br />

(siehe Datenblatt) an den Eingängen auftritt. Berücksichtigen Sie dabei die<br />

jeweiligen Eingangsströme IIL (siehe Datenblatt des Bausteines).<br />

Hinweis: Ein aus dem Eingang herausfließender Eingangsstrom ist im Datenblatt mit<br />

negativem Vorzeichen ausgewiesen. Ein hineinfließender Strom hingegen mit<br />

positivem Vorzeichen.<br />

Für die untenstehende Wired-AND-Verknüpfung dreier Open-Collector-Ausgänge des<br />

Bausteines SN74F38 ist der Pull-Up-Widerstand RC zu dimensionieren. Die<br />

Versorgungsspannung VCC sei +5V±10%. An den „Ausgang“ der Wired-AND-Verknüpfung<br />

sind 4 Eingänge eines Bausteines 74F00 angeschlossen.<br />

SS2007 5<br />

R PD<br />

V CC<br />

≥1<br />

74F00

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

9. Aufgabe<br />

a) Bestimmen Sie den kleinsten zulässigen Wert RC,min, so dass keiner der OC-<br />

Ausgänge von G1-G3 bei Low am Ausgang zerstört wird. Berücksichtigen Sie<br />

dazu den maximal zulässigen Ausgangsstrom IOL von G1-G3 aus dem Datenblatt<br />

(überlegen Sie, was der ungünstigste Fall bzgl. Durchschalten von G1-G3 ist, d.h.<br />

wenn ein einziger auf Low schaltet, alle schalten auf Low, ...), den ungünstigsten<br />

Wert der Versorgungsspannung sowie die Eingangsströme IIL der Eingänge des<br />

74F00-Bausteines bei Low (siehe Datenblatt).<br />

b) Bestimmen Sie den maximal zulässigen Wert RC,max, so dass die<br />

Ausgangsspannung Ua gerade noch einen gültigen TTL-High-Pegel von<br />

Ua,Hmin=2,0V annimmt. Berücksichtigen Sie dazu die Eingangsströme IIH der<br />

Eingänge des 74F00-Bausteines bei High (siehe Datenblatt) sowie die<br />

Ausgangsströme IOH der OC-Ausgänge und ebenso den diesmal ungünstigsten<br />

Wert der Versorgungsspannung.<br />

Hinweis: Ein in den Ausgang hineinfließender Ausgangsstrom ist im Datenblatt mit<br />

positivem Vorzeichen ausgewiesen.<br />

Es soll die Verlustleistung eines idealisierten NMOS-Inverters berechnet werden. Der<br />

MOSFET soll als idealer Schalter wirken, d.h. im eingeschalteten Zustand wirkt er als<br />

Kurzschluss (Widerstand zwischen Drain und Source RDS=0Ω) gegen Masse, im<br />

ausgeschalteten Zustand wirkt er wie eine Unterbrechung (RDS=∞). Der Ausgang sei<br />

unbelastet.<br />

=<br />

VGS=Ue<br />

Die Eingangsspannung Ue=VGS schalte periodisch zwischen VDD (z.B. +5V) und 0V.<br />

SS2007 6<br />

VDD<br />

RD<br />

VDS=Ua

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

10. Aufgabe<br />

Ue<br />

a) Geben Sie den Zeitverlauf der Ausgangsspannung Ua und des Stromes iD an.<br />

b) Geben Sie den Zeitverlauf der (dynamischen) Verlustleistung pR,dyn(t) im<br />

Widerstand RD an.<br />

Hinweis: p(t)=±u(t)⋅i(t) (Vorzeichen abhängig von der Orientierung der Stromund<br />

Spannungsbezugsrichtungen zueinander.)<br />

c) Berechnen Sie den Mittelwert der (dynamischen) Verlustleistung<br />

P = p ( t)<br />

im Widerstand.<br />

R, dyn<br />

VDD<br />

R, dyn<br />

d) Geben Sie die (statische) Verlustleistung PR,stat im Widerstand an, wenn der<br />

MOSFET kontinuierlich ein- bzw. ausgeschaltet ist.<br />

e) Tritt auch im MOSFET eine Verlustleistung auf, wenn<br />

o dieser als idealer Schalter wirkt?<br />

o dieser im eingeschalteten Zustand einen Widerstand RDS>0Ω darstellt?<br />

Es soll die Verlustleistung eines idealisierten CMOS-Inverters mit kapazitiver Last CL<br />

berechnet werden. Die MOSFETs sollen als ideale Schalter wirken. (Schalter S1 und S2<br />

werden gegenphasig geschaltet.)<br />

Die Eingangsspannung Ue schalte periodisch zwischen VDD (z.B. +5V) und 0V.<br />

SS2007 7<br />

CL<br />

=<br />

Ue<br />

VDD<br />

S2<br />

S1<br />

CL<br />

Ua

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

Es soll nun eine komplette Periode T (ein vollständiger Schaltzyklus Low→High→Low) am<br />

Ausgang betrachtet werden. Zu Beginn sei Schalter S2 offen und S1 geschlossen.<br />

11. Aufgabe<br />

Ue<br />

VDD<br />

a) Schalter S2 werde geschlossen und S1 gleichzeitig geöffnet. Der Kondensator CL<br />

lädt sich vollständig auf die Spannung VDD auf. Welche Ladungsmenge Q nimmt<br />

er dabei auf?<br />

b) Nach einer Zeit T/2 wird der Schalter S2 geöffnet und S1 geschlossen. Was<br />

passiert mit der am Kondensator gespeicherten Ladung Q und der<br />

Ausgangsspannung Ua?<br />

c) Welcher Strom ist folglich im Mittel während einer Periode T von der<br />

Versorgungsspannung VDD gegen Masse (über den „Umweg“ des Kondensators<br />

CL) geflossen?<br />

∆Q<br />

Hinweis: I = ∆t<br />

d) Welche mittlere (dynamische) Leistung Pdyn gibt die Versorgungsspannung VDD<br />

ab bzw. nimmt die Schaltung über die Spannungsversorgung (VDD) auf? Da der<br />

Kondensator CL keine Leistung verbraucht, muss der CMOS-Inverter diese<br />

Leistung verbrauchen!<br />

e) Geben Sie die (statische) Verlustleistung Pstat des CMOS-Inverters an, wenn die<br />

Eingangsspannung konstant Low bzw. High ist.<br />

Hinweis: Welcher Strom fließt in diesem Fall im Mittel von der<br />

Versorgungsspannung VDD gegen Masse?<br />

f) Wenn die Schalter S1 und S2 nicht „schlagartig“ öffnen bzw. schließen, sondern<br />

eine gewisse Zeit dafür benötigen, fließt während des Umschaltens kurzzeitig ein<br />

Querstrom IDD direkt von der Versorgungsspannung VDD gegen Masse. Wie hängt<br />

die dadurch bewirkte Verlustleistung von der Frequenz ab?<br />

Hinweis: Jeder Schaltvorgang Low→High und High→Low ist mit einem<br />

Stromimpuls gleich bleibender konstanter Form (Höhe und Dauer) verbunden.<br />

Wie ändert sich dementsprechend der dadurch bewirkte mittlere Strom?<br />

Eine Digitalschaltung soll bei entsprechenden Eingangssignalen ein externes Gerät an der<br />

Netzspannung einschalten. Dazu wird mittels eines Transistors ein Relais mit 24V<br />

Gleichspannung angesteuert, das letztlich das Einschalten des Gerätes vornimmt.<br />

SS2007 8

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

Damit das Relais den Schalter S schließt, muss ein ausreichend großer Schaltstrom I durch<br />

die Relaisspule fließen.<br />

Der maximale Kollektorstrom durch den Transistor betrage 100mA, seine Stromverstärkung<br />

sei B=50.<br />

12. Aufgabe<br />

Relaisspule<br />

(Widerstand R)<br />

Ansteuerung<br />

durch<br />

Digitalausgang<br />

ID<br />

24V=<br />

230V~<br />

Gerät<br />

Schalter S<br />

a) Wie groß ist der maximal erforderliche Ausgangsstrom ID der Digitalschaltung<br />

zum Einschalten des Gerätes?<br />

b) Welchen Widerstand R muss die Relaisspule mindestens aufweisen, damit der<br />

Transistor nicht zerstört wird?<br />

c) Wie müsste man die Schaltung erweitern, wenn der Widerstand R der Relaisspule<br />

zu klein ist?<br />

Gegeben sei eine Digitalschaltung mit +5V Spannungsversorgung. Mit Hilfe von<br />

Leuchtdioden (LED…Light-Emitting-Diode) soll der Betriebszustand des Systems angezeigt<br />

werden. Leuchtdioden verhalten sich im Prinzip wie gewöhnliche Dioden, jedoch ist ihre<br />

Flussspannung in Durchlassrichtung größer als 0,6V!<br />

• Mit einer roten LED soll angezeigt werden, dass das System eingeschaltet ist.<br />

Geben Sie eine möglichst einfache Schaltung an, die dies bewirkt. Nehmen Sie<br />

dazu eine typische Flussspannung der LED von 2V bei 10mA an.<br />

• Mit einer grünen LED soll der Status eines Digitalausganges angezeigt werden.<br />

Geben Sie eine Schaltung an, die dies bewirkt. Nehmen Sie dazu eine typische<br />

Flussspannung der LED von 2,5V bei 10mA an. Überlegen Sie, wie die LED über<br />

ein logisch High am Ausgang sowie ein logisch Low am Ausgang aktiviert werden<br />

kann. Sehen Sie in das Datenblatt irgendeines Digitalbausteines und überlegen Sie<br />

welche der beiden Methoden besser (zuverlässiger) ist.<br />

SS2007 9<br />

I

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

13. Aufgabe<br />

Für einen Speicherbaustein (Versorgungsspannung VDD=+3,3V) soll die erforderliche<br />

Kapazität CB seines Abblockkondensators bestimmt werden. Zuerst wird der maximal<br />

auftretende Laststrom, den der Speicherbaustein während des Umschaltens am Ausgang<br />

liefern muss, bestimmt.<br />

• Die Lastkapazität eines Digitalausganges (einer Datenleitung) betrage CL=30pF.<br />

Innerhalb von ∆t=2ns soll die Ausgangsspannung um 3V (Umschalten<br />

Low→High) steigen. Welcher Strom muss deshalb zum Aufladen der<br />

Lastkapazität fließen?<br />

Der Speicherbaustein weise 36 Datenleitungen auf, die im ungünstigsten Fall gleichzeitig von<br />

Low auf High schalten. Den gesamten Laststrom nimmt der Speicherbaustein über die<br />

Versorgungsspannung auf.<br />

14. Aufgabe<br />

• Wie groß muss die Kapazität CB des Abblockkondensators mindestens sein, wenn<br />

die Versorgungsspannung durch die plötzlich erhöhte Stromaufnahme während der<br />

Umschaltzeit von ∆t=2ns maximal um 0,05V absinken darf?<br />

Es soll die Verlustleistung eines Zählerbausteines 74HC163 (siehe Datenblatt) bei VCC=+5V<br />

Spannungsversorgung bestimmt werden. Die Eingangstaktfrequenz (clock, CP) sei<br />

fi =25MHz. An jedem Ausgang Q0–Q3 des Zählers wirke eine Lastkapazität CL von jeweils<br />

5,5pF (CMOS-Eingang mit 3,5pF + 2pF Leiterbahnkapazität).<br />

• Berechnen Sie die Verlustleistung des Zählerbausteines.<br />

Hinweis: Beachten Sie die jeweilige Taktfrequenz an den Ausgängen!<br />

15. Aufgabe<br />

Es sollen die grundsätzlichen Elemente einer allgemeinen Digitalschaltung zusammengefasst<br />

werden.<br />

Nehmen Sie dazu an, dass auf einer Leiterplatte eine Digitalschaltung bestehend aus zwei<br />

integrierten Digitalbausteinen (IC1, IC2) aufgebaut werden soll. Das Eingangssignal wird<br />

über einen Stecker St1 angeschlossen und das verarbeitete Ausgangssignal wird wieder über<br />

einen Stecker St2 ausgegeben. Die integrierten Digitalbausteine mögen auch unbenutzte<br />

Eingänge aufweisen.<br />

Geben Sie den prinzipiellen Aufbau der Schaltung unter Berücksichtigung der wesentlichen<br />

Einflussfaktoren (wie Spannungsversorgung, Leiterbahnführung usw.) an. Erklären Sie,<br />

warum gewisse Komponenten zusätzlich für den Schaltungsaufbau erforderlich sind.<br />

SS2007 10

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

Das folgende Rechteck symbolisiere die Leiterplatte, auf der die Komponenten (dargestellt<br />

durch einfache rechteckige, benannte Blöcke) und die Verbindungsleitungen eingezeichnet<br />

werden sollen.<br />

16. Aufgabe<br />

Ein Speicherbaustein (SRAM) ist nach untenstehendem Schema an einen Mikroprozessor µP<br />

angeschlossen. Der Adress-Decoder generiert dabei aus entsprechenden Adressleitungen das<br />

Chip-Select Signal CS .<br />

µP<br />

Adressbus<br />

A<br />

R / W<br />

Datenbus D<br />

Adress-<br />

Decoder<br />

SRAM<br />

Der Adress-Decoder weist eine maximale Verzögerungszeit von tPD,AD=10ns auf. Der<br />

Speicherbaustein erfordert eine minimale Vorbereitungszeit (setup time) tSU=20ns bzgl. des<br />

SS2007 11<br />

CS

<strong>Logikbausteine</strong> UE<br />

<strong>Aufgabensammlung</strong><br />

CS -Signals vor der Datenübernahme mit der steigenden Flanke des R / W -Signals. Die Dauer<br />

des Schreibpulses ( R / W -Signal) darf minimal tWP=15ns betragen.<br />

a) Zeichnen Sie im untenstehenden Diagramm den Zeitverlauf des Signals CS ein und<br />

tragen Sie die Zeiten tPD,AD , tSU , tWP ein.<br />

b) Geben Sie an, nach welcher Zeit tW,min der Mikroprozessor frühestens nach dem<br />

Ausgeben der gültigen Adresse die Daten mit der steigenden Flanke des R / W -Signals in<br />

den Speicher schreiben kann, damit die Zeitbedingungen erfüllt sind. Nach welcher Zeit<br />

∆t, ab dem Ausgeben der gültigen Adresse, muss für diesen Fall spätestens das R / W -<br />

Signal auf Low geschaltet werden?<br />

c) Die Haltezeit (hold time) der Adressleitungen des Speicherbausteines beträgt minimal<br />

tH=0ns (bezogen auf die steigende Flanke des R / W -Signals). Wie lange dauert minimal<br />

somit ein kompletter Schreibvorgang beginnend mit dem Anlegen einer Adresse? Dies ist<br />

die Zykluszeit tWC.<br />

d) Wenn mit jedem Schreibzyklus 2 Bytes in den Speicher geschrieben werden, wie hoch ist<br />

folglich die maximale Datenrate für das Schreiben?<br />

17. Aufgabe<br />

Für die Steuersignale eines Halbleiter-Speicherbausteines gibt es zwei typische<br />

Implementierungen. Bei der einen wird jeweils eine getrennte Steuerleitung für Lese- und<br />

Schreibzugriffe ( RD und WR , “Intel-style“) verwendet, bei der anderen eine gemeinsame<br />

Steuerleitung zur Unterscheidung der Datenrichtung sowie eine Auswahlleitung ( R / W und<br />

OE 1 , “Motorola-style“).<br />

Geben Sie jeweils eine Digitalschaltung an, welche die Steuerleitungen einer<br />

Implementierung in jene der anderen Implementierung umcodiert.<br />

1 OE … Output Enable; manchmal auch E (Enable) oder ähnlich bezeichnet<br />

SS2007 12