Überblick - Uni Bremen

Überblick - Uni Bremen

Überblick - Uni Bremen

Sie wollen auch ein ePaper? Erhöhen Sie die Reichweite Ihrer Titel.

YUMPU macht aus Druck-PDFs automatisch weboptimierte ePaper, die Google liebt.

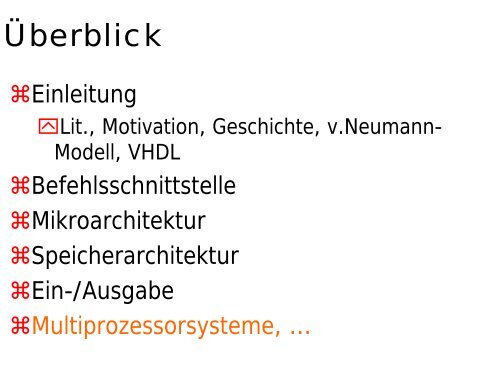

<strong>Überblick</strong><br />

zEinleitung<br />

yLit., Motivation, Geschichte, v.Neumann-<br />

Modell, VHDL<br />

zBefehlsschnittstelle<br />

zMikroarchitektur<br />

zSpeicherarchitektur<br />

zEin-/Ausgabe<br />

zMultiprozessorsysteme, ...

Kap.6<br />

Multiprozessorsysteme

Einsatz der zusätzlich verfügbaren<br />

Chipfläche<br />

z Parallelität auf Bitebene: bis etwa 1985<br />

y Kombinatorische Addierer und Multiplizierer, etc.<br />

y → wachsende Wortbreite auf 64 Bit<br />

z Parallelität auf Instruktionsebene: 1985 bis heute<br />

y Pipelining der Instruktionsverarbeitung<br />

y Mehrere Funktionseinheiten (→ superskalare Prozessoren)<br />

bei mehr als 4 Funktionseinheiten verhindern Datenabhängigkeiten<br />

oft eine effiziente Ausnutzung<br />

z Integration von Caches und Hauptspeicher auf die Chipfläche: 1990<br />

bis heute<br />

y Zur Verringerung der mittleren Zugriffszeiten<br />

y → DEC Alpha 21164: 77% der Fläche für Caches<br />

z Parallelität auf Prozessorebene: Perspektive

Performanz von Rechnern lässt sich durch<br />

Parallelverarbeitung<br />

steigern.<br />

z Parallelverarbeitung erfolgt bei<br />

y Verteilten Systemen<br />

Diese bestehen aus mehreren Prozessoren ohne gemeinsamen<br />

Speicher. Jeder Prozessor hat einen eigenen Speicher (local memory).<br />

Die Prozessoren tauschen Daten durch Nachrichten aus.<br />

Nachteil: Evtl. hoher Aufwand für Nachrichtenaustausch.<br />

y Parallelrechnern<br />

Diese bestehen ebenfalls aus mehreren Prozessoren und haben einen<br />

gemeinsamen Speicher (shared memory). Die Kommunikation erfolgt<br />

über den gemeinsamen Speicher.<br />

Nachteil: Evtl. Performanz-Probleme, wenn viele Prozessoren<br />

gleichzeitig auf den Speicher zugreifen wollen.

Architektur von<br />

verteilten/parallelen Systemen<br />

z Systeme mit Verbindungsnetzwerk und lokalem<br />

Speicher<br />

M1<br />

M2<br />

M3<br />

M4<br />

Cache<br />

Cache<br />

Cache<br />

Cache<br />

P1<br />

P2<br />

P3<br />

P4<br />

Verbindungsnetzwerk<br />

y Zugriff auf fremden lokalen Speicher nicht möglich<br />

y Kommunikation durch Austausch von Nachrichten<br />

y gute physikalische Skalierbarkeit

Architektur von<br />

verteilten/parallelen Systemen ff<br />

z Symmetrische Multiprozessoren (SMP)<br />

y gemeinsamer nichtverteilter Speicher<br />

P1<br />

P2<br />

P3<br />

P4<br />

Cache<br />

Cache<br />

Cache<br />

Cache<br />

Speicher<br />

y meist busbasiert mit physikalisch gemeinsamem Speicher<br />

y Reduktion der Speicherzugriffslatenz durch lokale Caches<br />

y Problem: Cache-Kohärenz<br />

y Beispiele: SGI Challenge, Sun Enterprise

Architektur von<br />

verteilten/parallelen Systemen ff<br />

z Verteilter gemeinsamer Speicher<br />

y lokale Speichermodule<br />

y gemeinsamer Adressraum<br />

P1<br />

P2<br />

P3<br />

P4<br />

M1<br />

M2<br />

M3<br />

M4<br />

Verbindungsnetzwerk<br />

Beispiel:<br />

Cray T3D

Architektur von<br />

verteilten/parallelen Systemen ff<br />

z Verteilter gemeinsamer Speicher mit lokalem Cache<br />

y lokale Speichermodule<br />

y gemeinsamer Adressraum<br />

y Zugriff der Prozessoren über prozessor-eigenen Cache<br />

P1<br />

P2<br />

P3<br />

P4<br />

Cache<br />

Cache<br />

Cache<br />

Cache<br />

M1<br />

M2<br />

M3<br />

M4<br />

Verbindungsnetzwerk<br />

Beispiele:<br />

HP Convex SPP

Unterteilung von<br />

paralleln/verteilten Systemen<br />

nach dem verwendeten Speichermodell:<br />

y verteilter Speicher, getrennte Adressräume<br />

y verteilter Speicher, gemeinsamer Adressraum<br />

y Nichtverteilter Speicher, gemeinsamer Adressraum<br />

nach der Homogenität der Prozessoren<br />

y homogene Parallelrechner: alle Prozessoren sind gleich<br />

y heterogene Parallelrechner: Prozessoren dürfen sich<br />

hardwaremäßig unterscheiden<br />

Nach der Hierarchie zwischen den Prozessoren<br />

y symmetrische Parallelrechner: die Prozessoren sind bzgl. ihrer<br />

Rolle im System untereinander austauschbar<br />

y nichtsymmetrische Parallelrechner: es gibt Masters und Slaves<br />

Nach der Eigenständigkeit der Prozessoren<br />

y lose gekoppelte Parallelrechner: Netzwerk von eigenständigen<br />

Rechnern<br />

y eng gekoppelte Parallelrechner: physikalisch ein Rechner

Bsp.:<br />

Flynn's Schema ´66<br />

z Einteilung von Rechnern in Klassen:<br />

y SISD (Single Instruction stream, Single Data stream)<br />

→ Personal Computer<br />

y SIMD (Single Instruction stream, Multiple Data streams)<br />

→ Vektorrechner, wie Illiac IV (1972, 64 Knoten), CM-2 (1987, 65536<br />

Knoten) Die gleiche Instruktion wird parallel auf einen Vektor von<br />

Daten angewendet.<br />

y MISD (Multiple Instruction streams, Single Data stream)<br />

Mehrere Anweisungen parallel.<br />

y MIMD (Multiple Instruction streams, Multiple Data streams)<br />

→ INMOS Transputer, CONVEX SPP, CRAY T3D/T3E, IBM SP2

Verbindungsstrukturen<br />

z Der Kommunikationsaufwand zwischen den Prozessoren ist<br />

einer der Hauptpunkte für die Leistung des parallelen/verteilten<br />

Systems.<br />

⇒ nicht jedes Problem ist für Parallelisierung geeignet.<br />

z Verschiedene Kommunikationsstrukturen unterscheiden sich<br />

hinsichtlich ihrer Kosten und ihrer Leistung.<br />

Beispiel:<br />

Vollständiger<br />

Verbindungsgraph

Modellierung von Verbindungen<br />

z Modellierung: Die Topologie eines Parallelrechners wird durch einen<br />

abstrakten Graphen G=(V,E) dargestellt, mit<br />

y V = { 1, ... , n } Menge der Knoten, d.h. der Prozessoren<br />

y E ⊆ { {a,b}; a,b ∈ V }, die Menge der Kanten, d.h. der Verbindungen<br />

z Charakteristika einer Verbindungsstruktur<br />

y Durchmesser(G) = max v,w∈V<br />

{ Länge des kürzesten Pfades von v nach<br />

w}<br />

y Grad(G) = max v∈V<br />

| { w ∈ V; {v,w} ∈ E } |<br />

y Anzahl der physikalischen Verbindungen (G) = | E |

Verbindungsstrukturen<br />

z Vollständiger Verbindungsgraph<br />

Zu teuer wegen dem großen Fanout<br />

• Durchmesser = 1<br />

• Grad = n-1<br />

• |Verbindungen| = n(n-1)/2, keine „Kollisionen“

Verbindungsstrukturen ff<br />

z Stern<br />

• Durchmesser = 2<br />

• Grad = n-1<br />

• |Verbindungen| = n-1,

Verbindungsstrukturen ff<br />

z Bus<br />

Topologie versagt bei den heutigen Technologien bei<br />

großem Datentransfer zwischen den Prozessoren<br />

• Ein Bus lässt sich als Stern modellieren, wobei der zentrale Knoten<br />

aber kein Prozessor ist, sondern der zentrale Bus.<br />

• Gleiches „Flaschenhalsproblem“ wie bei Stern.

Beispiel für Bustopologie: Ethernet<br />

Charakteristika<br />

z Bus-Topologie<br />

z 10 - 100 Mbit / Sekunde<br />

z Paket-Versand mit Paketgrößen von 64-1518 Bytes<br />

z Nicht abhörsicher: alle hören mit !<br />

z (Lokales) Rechnernetz über eine Bridge mit der Außenwelt<br />

verbunden, die die Nachrichten filtert und verstärkt<br />

Übertragungsvorgang<br />

z Nachrichten werden in Pakete fester Länge zerteilt. Jedes Paket<br />

enthält Headerinformation mit Zieladresse und Sequenznummer<br />

z Jeder Rechner horcht am Bus und empfängt die Pakete, die seine<br />

Adresse tragen<br />

z Kollisionen von mehreren Sendern werden erkannt.

Verbindungsstrukturen ff<br />

z Ring<br />

• Durchmesser = n/2<br />

• Grad = 2<br />

• |Verbindungen| = n,<br />

Beispiel für Ring: Token-Ring<br />

Es kreist ein sogenanntes Token<br />

(spezielles Paket).<br />

Ein Rechner darf nur dann senden, wenn<br />

er das Token besitzt.

Beispiel für Ringtopologie: CDDI/FDDI-<br />

Ring<br />

[Copper / Fiber Distributed Data Interconnect]<br />

Charakteristika<br />

z Ring-Topologie<br />

z Besteht aus zwei gegenläufigen Ringen<br />

→ Fehlertolerantes Netz<br />

z ... ansonsten wie beim Token-Ring

CDDI/FDDI-Ring ist fehlertolerant !

Verbindungsstrukturen ff<br />

z Stern<br />

HUB<br />

• Durchmesser = 2<br />

• Grad = 1<br />

• |Verbindungen| = n,

Verbindungsstrukturen ff<br />

z MESH (torusähnliches Gitter)<br />

Typischer Vertreter war das Transputer-Netz von INMOS<br />

• Durchmesser = n 1/2<br />

• Grad = 4<br />

• |Verbindungen| = 2n

Verbindungsstrukturen ff<br />

z Hypercube (d-dimensionaler Würfel)<br />

Nicht verwendbar, da Grad zu hoch<br />

• Durchmesser = log n<br />

• Grad = log n<br />

• |Verbindungen| = (n log n) / 2, in der Regel keine Wartezeiten

Verbindungsstrukturen ff<br />

z Cube Connected Cycle (CCC)<br />

• Durchmesser ≈ 2 log n<br />

• Grad = 3<br />

• |Verbindungen| = 3n / 2, in der Regel keine Wartezeiten

Verbindungsstrukturen ff<br />

z Crossbar Switch<br />

meist verwendete Struktur bei<br />

Parallelrechnern mit gemeinsamen<br />

"nichtverteilten" Speicher<br />

CPU 0<br />

CPU 1<br />

CPU 2<br />

CPU 3<br />

CPU 4<br />

CPU 5<br />

CPU 6<br />

CPU 7<br />

S0 S1 S2 S3 S4 S5 S6 S7<br />

keine<br />

Verbindung<br />

Verbindung<br />

Nachteil: n⋅m Crosspoints<br />

entspricht

Verbindungsstrukturen ff<br />

z Omega Netzwerk (als Alternative zum Crossbar Scwitch)<br />

P<br />

R<br />

O<br />

Z<br />

E<br />

S<br />

S<br />

O<br />

R<br />

E<br />

N<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

1A<br />

1B<br />

1C<br />

1D<br />

2A<br />

2B<br />

2C<br />

2D<br />

3A<br />

3B<br />

3C<br />

3D<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

S<br />

P<br />

E<br />

I<br />

C<br />

H<br />

E<br />

R<br />

... besitzt nur n/2 log n Schalter

Verbindungsstrukturen ff<br />

z Omega Netzwerk<br />

y der obere Ausgang eines Schalters ist der 0-Ausgang<br />

y der untere Ausgang eines Schalters ist der 1-Ausgang<br />

y ein Schalter der Stufe i schaltet gemäß dem i-ten Bit der<br />

Zieladresse<br />

P<br />

R<br />

O<br />

Z<br />

E<br />

S<br />

S<br />

O<br />

R<br />

E<br />

N<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

1A<br />

1B<br />

1C<br />

1D<br />

2A<br />

2B<br />

2C<br />

2D<br />

3A<br />

3B<br />

3C<br />

3D<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

S<br />

P<br />

E<br />

I<br />

C<br />

H<br />

E<br />

R

Verbindungsstrukturen ff<br />

z Omega Netzwerk<br />

y nicht jede Kommunikation ist gleichzeitig möglich, auch wenn alle<br />

Zieladressen paarweise verschieden sind (blocking<br />

network)<br />

P<br />

R<br />

O<br />

Z<br />

E<br />

S<br />

S<br />

O<br />

R<br />

E<br />

N<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

1A<br />

1B<br />

1C<br />

1D<br />

2A<br />

2B<br />

2C<br />

2D<br />

3A<br />

3B<br />

3C<br />

3D<br />

000<br />

001<br />

010<br />

011<br />

100<br />

101<br />

110<br />

111<br />

S<br />

P<br />

E<br />

I<br />

C<br />

H<br />

E<br />

R

Local and Wide Area Networks<br />

4 Mbit/s<br />

Token Ring<br />

4 Mbit/s<br />

Subnet<br />

(Telekom)<br />

2 Mbit/s<br />

B-ISDN<br />

34 Mbit/s<br />

155 Mbit/s<br />

Token Ring<br />

Token Ring<br />

10 Mbps 4Mbps<br />

Ethernet<br />

z Lokale Netze (LAN): Netze mit Ausdehnung von wenigen 100 Metern zur<br />

Verbindung der Rechner einer Abteilung oder einer kleineren Firma<br />

z Weitverkehrsnetze (WAN): zur weltweiten Verbindung über Datennetze<br />

der Post bzw. private / kommerzielle Satellitenverbindungen

Vermittlungsarten<br />

z Paket-vermittelnde Vermittlung<br />

y Nachricht wird in ein oder mehrere Pakete verpackt<br />

y Jedes der Pakete enthält die Adresse des Empfängers<br />

y Es wird kein Pfad vom Sender zum Empfänger freigeschaltet<br />

y Das Paket wird in Abhängigkeit der Empfängeradresse immer nur zu<br />

einem direkten Nachbarn geschickt.<br />

z Leitungsvermittelnde Vermittlung<br />

Leitungsvermittelnde Vermittlung<br />

y Es wird im Netzwerk ein Pfad vom Sender zum Empfänger geschaltet,<br />

über den alle Nachrichten geschickt werden (Bsp: Telefonverbindung)

Leitungsvermittelnde Vermittlung<br />

Sender 1<br />

Sender 1<br />

Empfänger 1<br />

Empfänger 1<br />

Sender 2<br />

Sender 2<br />

Empfänger 2<br />

Empfänger 2<br />

Sender 3<br />

Sender 3<br />

Empfänger 3<br />

Empfänger 3<br />

Ú Schnelle Übertragung großer Datenmengen<br />

‣ Geschalteter Pfad blockiert andere Verbindungen

Paket-vermittelnde Vermittlung<br />

Sender 1<br />

Sender 1<br />

Empfänger 1<br />

Empfänger 1<br />

Sender 2<br />

Sender 2<br />

Empfänger 2<br />

Empfänger 2<br />

Sender 3<br />

Sender 3<br />

Empfänger 3<br />

Empfänger 3<br />

Ú Keine Verbindung muss lange warten<br />

‣ Unterbrechungen während einer Übertragung möglich

Kommunikationskontrolle<br />

z<br />

z<br />

deterministische Kontrolle<br />

der Weg eines jeden Pakets ist reproduzierbar<br />

randomisierte Kontrolle<br />

an bestimmten Stellen des Algorithmus werden zufällige<br />

Entscheidungen getroffen<br />

Beispiel: Valiant-Paradigma<br />

u Route zu einer zufälligen Zwischenadresse<br />

u Route dann erst zum Ziel