2. Übung Vorlesung Rechnerstrukturen WS 2000/2001

2. Übung Vorlesung Rechnerstrukturen WS 2000/2001

2. Übung Vorlesung Rechnerstrukturen WS 2000/2001

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

<strong>2.</strong> Übung<br />

<strong>Vorlesung</strong> <strong>Rechnerstrukturen</strong> <strong>WS</strong> <strong>2000</strong>/<strong>2001</strong><br />

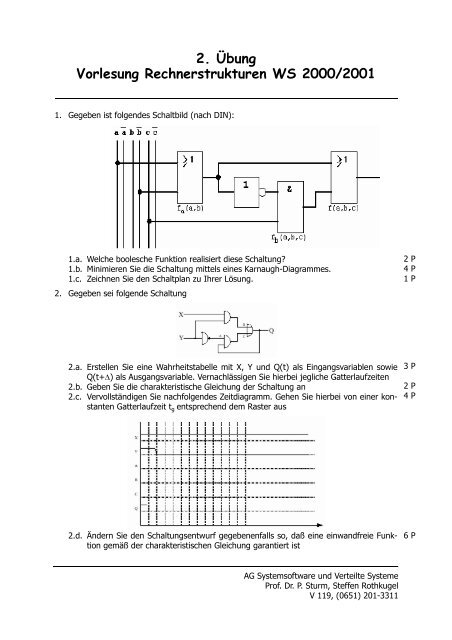

1. Gegeben ist folgendes Schaltbild (nach DIN):<br />

1.a. Welche boolesche Funktion realisiert diese Schaltung?<br />

1.b. Minimieren Sie die Schaltung mittels eines Karnaugh-Diagrammes.<br />

1.c. Zeichnen Sie den Schaltplan zu Ihrer Lösung.<br />

<strong>2.</strong> Gegeben sei folgende Schaltung<br />

2 P<br />

4 P<br />

1 P<br />

<strong>2.</strong>a. Erstellen Sie eine Wahrheitstabelle mit X, Y und Q(t) als Eingangsvariablen sowie<br />

Q(t+,) als Ausgangsvariable. Vernachlässigen Sie hierbei jegliche Gatterlaufzeiten<br />

<strong>2.</strong>b. Geben Sie die charakteristische Gleichung der Schaltung an<br />

<strong>2.</strong>c. Vervollständigen Sie nachfolgendes Zeitdiagramm. Gehen Sie hierbei von einer konstanten<br />

Gatterlaufzeit t g entsprechend dem Raster aus<br />

3 P<br />

2 P<br />

4 P<br />

<strong>2.</strong>d. Ändern Sie den Schaltungsentwurf gegebenenfalls so, daß eine einwandfreie Funktion<br />

gemäß der charakteristischen Gleichung garantiert ist<br />

6 P<br />

AG Systemsoftware und Verteilte Systeme<br />

Prof. Dr. P. Sturm, Steffen Rothkugel<br />

V 119, (0651) 201-3311

3. Zeichnen Sie ein Timingdiagramm für die folgende Schaltung:<br />

10 P<br />

Finden Sie zunächst einen nicht-oszillierenden Zustand der Schaltung, wobei der Schalter<br />

wie gezeigt in Position (1) steht. Beginnen Sie Ihr Timingdiagramm in diesem stabilen<br />

Zustand und tragen Sie die Signale an den markierten Anschlüssen A bis D ein.<br />

Zum Zeitpunkt T wird der Schalter in Position (2) gebracht. Vervollständigen Sie Ihr Timingdiagramm,<br />

indem Sie die Signale A bis D in weiteren 15 Rastereinheiten einzeichnen.<br />

Gehen Sie dabei von einer konstanten Gatterlaufzeit t g aus.<br />

4. Mittels RS-Latches kann festgestellt werden, welches von zwei Ereignissen zuerst eingetreten<br />

ist.<br />

4.a. Entwerfen Sie eine Schaltung mit drei Eingängen und drei Ausgängen, die feststellt,<br />

welches der drei Eingangssignale zuerst eingetreten ist. Dabei soll der Ausgang des<br />

zuerst selektierten Einganges logisch 1 werden und die anderen beiden Ausgänge<br />

sollen logisch 0 liefern.<br />

4.b. Diskutieren Sie, wie Sie die Schaltung erweitern würden, um eine höhere Anzahl von<br />

Ein- und Ausgängen realisieren zu können.<br />

5. Ein D-Latch ist ein Baustein, der einen Datenwert zwischenspeichern kann. Das D-Latch<br />

hat einen Steuereingang C, einen Dateneingang D sowie einen Ausgang Q. Solange der<br />

Steuereingang C log. 0 ist, wird das aktuelle Datensignal D an den Ausgang Q weitergegeben.<br />

Sobald C auf log. 1 geht, wird der aktuelle Ausgangszustand an Q beibehalten.<br />

5.a. Entwerfen Sie ein Zustandsdiagramm für das D-Latch.<br />

5.b. Geben Sie eine entsprechende Wahrheitstabelle an.<br />

5.c. Geben Sie die charakteristische Gleichung des D-Latches an.<br />

5.d. Entwerfen Sie eine möglichst minimale Schaltung für das D-Latch.<br />

10 P<br />

6 P<br />

4 P<br />

3 P<br />

2 P<br />

6 P<br />

Ausgegeben: 03.11.<strong>2000</strong><br />

Abgabe: bis spätestens Donnerstag 16.11.<strong>2000</strong> vor der Übung<br />

AG Systemsoftware und Verteilte Systeme<br />

Prof. Dr. P. Sturm, Steffen Rothkugel<br />

V 119, (0651) 201-3311