PC Magazin DOS - Xputer Lab Kaiserslautern

PC Magazin DOS - Xputer Lab Kaiserslautern

PC Magazin DOS - Xputer Lab Kaiserslautern

Erfolgreiche ePaper selbst erstellen

Machen Sie aus Ihren PDF Publikationen ein blätterbares Flipbook mit unserer einzigartigen Google optimierten e-Paper Software.

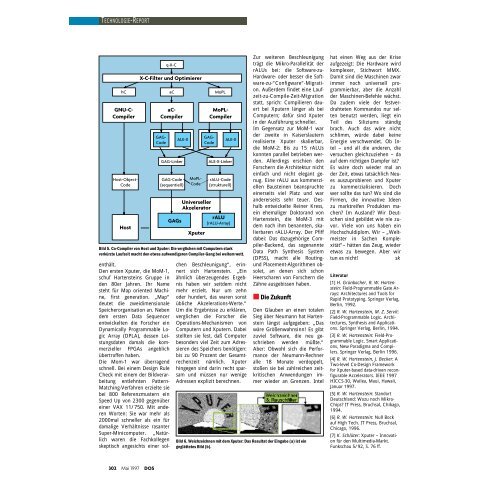

TECHNOLOGIE-REPORThCGNU-C-CompilerHost-Object-CodeHostq-X-CX-C-Filter und OptimiereraCaC-CompilerGAG-CodeGAG-LinkerGAG-Code(sequentiell)GAGsALE-XMoPL-CodeMoPLMoPL-CompilerGAG-CodeUniversellerAkzelerator<strong>Xputer</strong>ALE-XALE-X-LinkerrALU-Code(strukturell)rALU(rALU-Array)Bild 5. Co-Compiler von Host und <strong>Xputer</strong>: Die verglichen mit Computern starkverkürzte Laufzeit macht den etwas aufwendigeren Compiler-Gang bei weitem wett.enthält.Den ersten <strong>Xputer</strong>, die MoM-1,schuf Hartensteins Gruppe inden 80er Jahren. Ihr Namesteht für Map oriented Machine,first generation. „Map“deutet die zweidimensionaleSpeicherorganisation an. Nebendem ersten Data Sequencerentwickelten die Forscher einDynamically Programmable LogicArray (DPLA), dessen Leistungsdatendamals die kommerziellerFPGAs angeblichübertroffen haben.Die Mom-1 war überragendschnell. Bei einem Design RuleCheck mit einem der Bildverarbeitungentlehnten Pattern-Matching-Verfahren erzielte siebei 800 Referenzmustern einSpeed Up von 2300 gegenübereiner VAX 11/750. Mit anderenWorten: Sie war mehr als2000mal schneller als ein fürdamalige Verhältnisse rasanterSuper-Minicomputer. „Natürlichwaren die Fachkollegenskeptisch angesichts einer solchenBeschleunigung“, erinnertsich Hartenstein. „Einähnlich überzeugendes Ergebnishaben wir seitdem nichtmehr erzielt. Nur um zehnoder hundert, das waren sonstübliche Akzelerations-Werte.“Um die Ergebnisse zu erklären,verglichen die Forscher dieOperations-Mechanismen vonComputern und <strong>Xputer</strong>n. Dabeistellten sie fest, daß Computerbesonders viel Zeit zum Adressierendes Speichers benötigen:bis zu 90 Prozent der Gesamtrechenzeitnämlich. <strong>Xputer</strong>hingegen sind darin recht sparsamund müssen nur wenigeAdressen explizit berechnen.Zur weiteren Beschleunigungträgt die Mikro-Parallelität derrALUs bei: die Software-zu-Hardware- oder besser die Software-zu-“Configware“-Migration.Außerdem findet eine Laufzeit-zu-Compile-Zeit-Migrationstatt, sprich: Compilieren dauertbei <strong>Xputer</strong>n länger als beiComputern; dafür sind <strong>Xputer</strong>in der Ausführung schneller.Im Gegensatz zur MoM-1 warder zweite in <strong>Kaiserslautern</strong>realisierte <strong>Xputer</strong> skalierbar,die MoM-2: Bis zu 15 rALUskonnten parallel betrieben werden.Allerdings erschien denForschern die Architektur nichteinfach und nicht elegant genug.Eine rALU aus kommerziellenBausteinen beanspruchteeinerseits viel Platz und warandererseits sehr teuer. Deshalbentwickelte Reiner Kress,ein ehemaliger Doktorand vonHartenstein, die MoM-3 mitdem nach ihm benannten, skalierbarenrALU-Array. Der Pfiffdabei: Das dazugehörige Compiler-Backend,das sogenannteData Path Synthesis System(DPSS), macht alle RoutingundPlacement-Algorithmen obsolet,an denen sich schonHeerscharen von Forschern dieZähne ausgebissen haben.■ Die ZukunftDen Glauben an einen totalenSieg über Neumann hat Hartensteinlängst aufgegeben: „Daswäre Größenwahnsinn! Es gibtzuviel Software, die neu geschriebenwerden müßte.“Aber: Obwohl sich die Performanceder Neumann-Rechneralle 18 Monate verdoppelt,stoßen sie bei zahlreichen zeitkritischenAnwendungen immerwieder an Grenzen. IntelBild 6. Weichzeichnen mit dem <strong>Xputer</strong>: Das Resultat der Eingabe (a) ist eingeglättetes Bild (b).hat einen Weg aus der Kriseaufgezeigt: Die Hardware wirdkomplexer, Stichwort MMX.Damit sind die Maschinen zwarimmer noch universell programmierbar,aber die Anzahlder Maschinen-Befehle wächst.Da zudem viele der festverdrahtetenKommandos nur seltenbenutzt werden, liegt einTeil des Siliziums ständigbrach. Auch das wäre nichtschlimm, würde dabei keineEnergie verschwendet. Ob Intel– und all die anderen, dieversuchen gleichzuziehen – daauf dem richtigen Dampfer ist?Es wäre doch wieder mal ander Zeit, etwas tatsächlich Neuesauszuprobieren und <strong>Xputer</strong>zu kommerzialisieren. Dochwer sollte das tun? Wo sind dieFirmen, die innovative Ideenzu marktreifen Produkten machen?Im Ausland? Wir Deutschensind gebildet wie nie zuvor.Viele von uns haben einHochschuldiplom. Wir – „Weltmeisterin Sachen Komplexität“–hätten das Zeug, wiederetwas zu bewegen. Aber wirtun es nicht!skLiteratur[1] H. Grünbacher, R. W. Hartenstein:Field-Programmable Gate Arrays:Architectures and Tools forRapid Prototyping. Springer Verlag,Berlin, 1992.[2] R. W. Hartenstein, M. Z. Servít:Field-Programmable Logic. Architectures,Synthesis and Applications.Springer Verlag, Berlin, 1994.[3] R. W. Hartenstein: Field-ProgrammableLogic. Smart Applications,New Paradigma and Compilers.Springer Verlag, Berlin 1996.[4] R. W. Hartenstein, J. Becker: ATwo-level Co-Design Frameworkfor <strong>Xputer</strong>-based data-driven reconfigurableAccelerators. IEEE 1997HICCS-30, Wailea, Maui, Hawaii,Januar 1997.[5] R. W. Hartenstein: StandortDeutschland: Wozu noch Mikro-Chips? IT Press, Bruchsal, Chikago,1994.[6] R. W. Hartenstein: Null Bockauf High Tech. IT Press, Bruchsal,Chicago, 1996.[7] K. Schlüter: <strong>Xputer</strong> – Innovationfür den Multimedia-Markt.Funkschau 5/92, S. 76 ff.302 Mai 1997 <strong>DOS</strong>