64 Core Processors - MM4M

64 Core Processors - MM4M

64 Core Processors - MM4M

Create successful ePaper yourself

Turn your PDF publications into a flip-book with our unique Google optimized e-Paper software.

LinuxDevices.com, Aug. 20, 2007<br />

A startup founded by an MIT professor claims to have "solved the fundamental challenges<br />

associated with multicore scalability." Tilera's first products include a <strong>64</strong>-core Tile<strong>64</strong> SoC<br />

(system-on-chip), PCIe Express add-in board for networking and video-processing applications,<br />

multicore-optimized Linux libraries, and an Eclipse-based multicore development environment<br />

toolset.<br />

Fabbed on 90nm process technology at TMSC, the Tile<strong>64</strong> chip is "the first in<br />

a family of chips that can scale to hundreds and even thousands of cores,"<br />

Tilera said. The company plans to bake a 120-core version on 65nm<br />

technology in the future, it added.<br />

The Tile<strong>64</strong> is based on a proprietary VLIW (very long instruction word) architecture, on which a<br />

MIPS-like RISC architecture is implemented in microcode. A hypervisor enables each core to run<br />

its own instance of Linux -- or other OSes, once they become available. Alternatively, the whole<br />

chip can run Tilera's <strong>64</strong>-way SMP (symmetrical multiprocessing) implementation.<br />

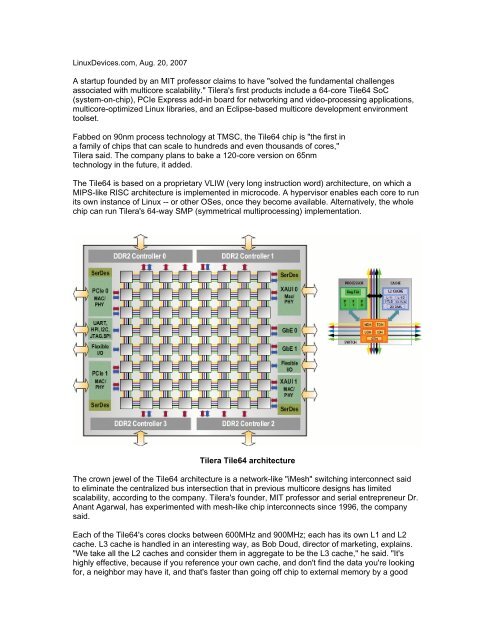

Tilera Tile<strong>64</strong> architecture<br />

The crown jewel of the Tile<strong>64</strong> architecture is a network-like "iMesh" switching interconnect said<br />

to eliminate the centralized bus intersection that in previous multicore designs has limited<br />

scalability, according to the company. Tilera's founder, MIT professor and serial entrepreneur Dr.<br />

Anant Agarwal, has experimented with mesh-like chip interconnects since 1996, the company<br />

said.<br />

Each of the Tile<strong>64</strong>'s cores clocks between 600MHz and 900MHz; each has its own L1 and L2<br />

cache. L3 cache is handled in an interesting way, as Bob Doud, director of marketing, explains.<br />

"We take all the L2 caches and consider them in aggregate to be the L3 cache," he said. "It's<br />

highly effective, because if you reference your own cache, and don't find the data you're looking<br />

for, a neighbor may have it, and that's faster than going off chip to external memory by a good

ways."<br />

The Tile<strong>64</strong> is implemented as a a system-on-chip (SoC) with no requirement for external<br />

northbridge and/or southbridge chips. This saves power, at the expense of locking in a specific<br />

peripheral mix, essentially tying the chip to specific verticals, according to the company. Doud<br />

noted, "We did a lot of research, and believe we have the peripheral mix right for the markets we<br />

are targeting -- networking and video. If we went into storage with a new processor, we'd add<br />

fiber and disk drive interfaces."<br />

Tilera claims that the Tile<strong>64</strong> outperforms Intel's dual-core Xeon processor 10 times, while<br />

offering 30 times better performance per Watt. Compared to TI's top-of-range TMS320DM<strong>64</strong>8<br />

DSP, performance per Watt is claimed to be 40 times better.<br />

Another touted benefit is the ability to consolidate control- and data-plane functions on a single<br />

device, with "solid-wall" processor boundaries reinforcing security and licensing containment<br />

barrier. In this regard, the Tile<strong>64</strong> chip resembles another heavily multicore MIPS<strong>64</strong> chip,<br />

Cavium's 16-way Octeon.<br />

Software environment and tools<br />

Tilera claims that existing, "unmodified" Linux apps will build for the Tile<strong>64</strong> processor using the<br />

company's toolchain. The toolchain includes a compiler licensed from SGI and based on<br />

MIPSpro.<br />

Alternatively, developers can port their applications to Tilera's iLib C library, aimed at exploiting<br />

parallelism while still supporting standard system calls. The approach appears to resemble that<br />

used in Intel's Threading Building Blocks, recently released under an open source license.<br />

Finally, for users wishing to manually tune multi-core application performance, Tilera will offer a<br />

full "MDE" (multicore development environment) toolsuite based on Eclipse. In addition to a full<br />

IDE (integrated development environment), MDE includes a parallel debugger, along with an<br />

application profiler aimed at helping developers figure out what parts of their code to optimize for<br />

multicore.<br />

Tilera is in discussions with "all major Linux support providers," Doud said, adding, "We'll have<br />

ecosystem announcements coming out as we line them up."<br />

Early markets, customers, reference implementations<br />

The first Tile<strong>64</strong> chips target network and video devices that require significant application<br />

processing, such as surveillance systems, and firewalls with deep packet inspection. Early<br />

customers in the networking space reportedly include 3Com and firewall vendor TopLayer, while<br />

early video customers reportedly include U.K.-based high-definition videoconferencing<br />

equipment provider Codian, and BackupTV, a vendor of network-based video recording and<br />

other head-end services for cable TV network providers.<br />

To hasten adoption, Tilera is offering processor daughterboards implemented as PCI Express<br />

cards with six or 12 gigabit Ethernet ports. The cards can be used in production systems with<br />

passive backplanes, or as targets in development hosts, Doud said. He declined to specify<br />

pricing.

CEO Devesh Garg stated, "This is the first significant new development in chip architecture in a<br />

decade. We developed this new architecture because existing multicore technologies simply<br />

cannot scale. Moreover, customers have repeatedly indicated that the current multicore software<br />

tools are very primitive because they are based on single-processor-core models. We're<br />

introducing a revolutionary hardware and software platform that has solved the fundamental<br />

challenges associated with multicore scalability."<br />

Availability<br />

The Tile<strong>64</strong> is available now, in three variants differentiated by I/O mix and clock. Pricing starts at<br />

$435 in 10,000 quantities, the company said. Tilera's iLib and MDE tools, and TilExpress-<strong>64</strong><br />

board are also available at undisclosed pricing.<br />

Henry Kingman